A memory virtualization method and system under the Shenwei architecture

A technology of memory virtualization and Shenwei, which is applied in memory systems, software simulation/interpretation/simulation, multi-programming devices, etc. It can solve the problem of introducing query overhead, inability to take advantage of the software flexibility of Shenwei architecture, and complex code implementation, etc. problems to achieve the effect of eliminating page fault processing overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] In order to make the above objects, features and advantages of the present invention more clearly understood, the present invention will be further described in detail below through specific embodiments and accompanying drawings.

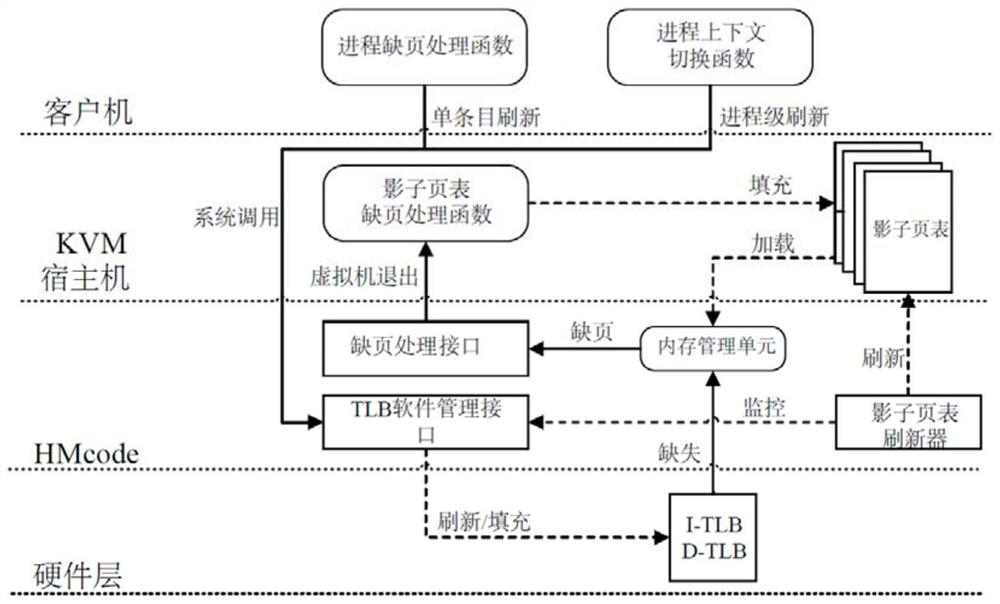

[0044] The "software-managed TLB" mentioned in the present invention means that the architecture exposes the TLB software management interface for the operating system to refresh / fill TLB entries.

[0045] The "shadow page table" in the present invention refers to a page table used to directly cache the mapping relationship between the virtual address of the guest and the physical address of the host in a virtualized environment. This is an important method used to accelerate the efficiency of two-layer address translation.

[0046] The "page table synchronization" in the present invention means that in the shadow page table memory virtualization model, the shadow page table needs to maintain mapping consistency with the client process page t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More