A Low-Power Register Allocation Compilation Optimization Method

A register allocation and optimization method technology, applied in the computer field, can solve problems such as unsatisfactory energy consumption, achieve the effects of optimizing system operating power consumption, low development cost, and tapping the potential of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

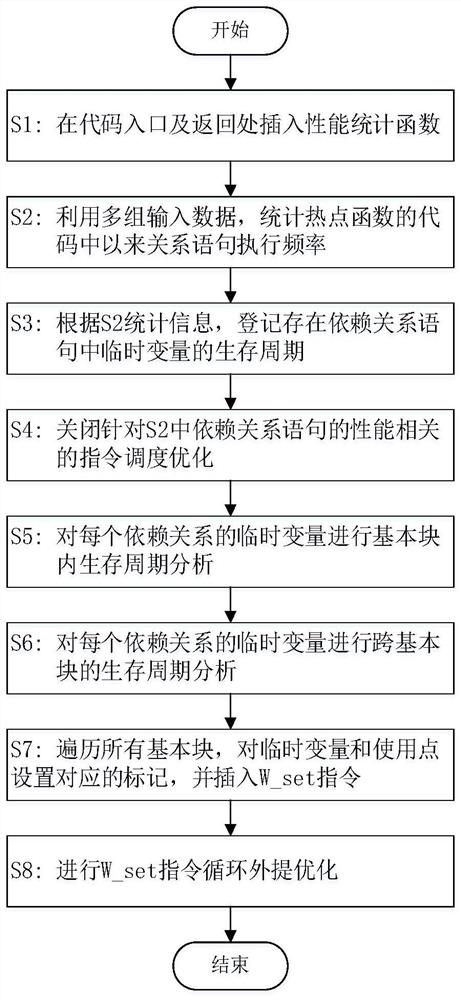

Image

Examples

Embodiment

[0022] Embodiment: A low-power register allocation compilation optimization method, based on the following modules:

[0023] The hardware register file enable setting module is used to control the write-back enable bit of the register file: if the enable is turned on, all the specified registers still need to be written back to the register file after bypassing; if the enable is turned off, all the specified registers are bypassed There is no need to write back after the operation, the register still saves the old value, the hardware provides the enable control setting for write back to the specified register file, the default is to write back all registers after bypassing, if you need to specify the register for non-write back operation , open to the software the control setting of the enable bit;

[0024] The software low-power register allocation optimization compiler module is used to analyze the hotspot functions that consume a lot of power in the program and optimize the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More