Techniques for dynamically compressing memory regions having a uniform value

A technology of memory and memory location, applied in memory system, instrument, memory address/allocation/relocation, etc., can solve the problems of ZBC compression performance limitation and difficulty

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] Conventional Zero Bandwidth Clear (ZBC) mechanisms rely on a single global unified table. Therefore, the number of distinct values available to flush the buffer to a uniform value via ZBC compression is limited to the number of entries in the global uniform table. As described further herein, conventional ZBC mechanisms are enhanced, for example, by extending the number of values available for ZBC encoding beyond the on-chip storage limit.

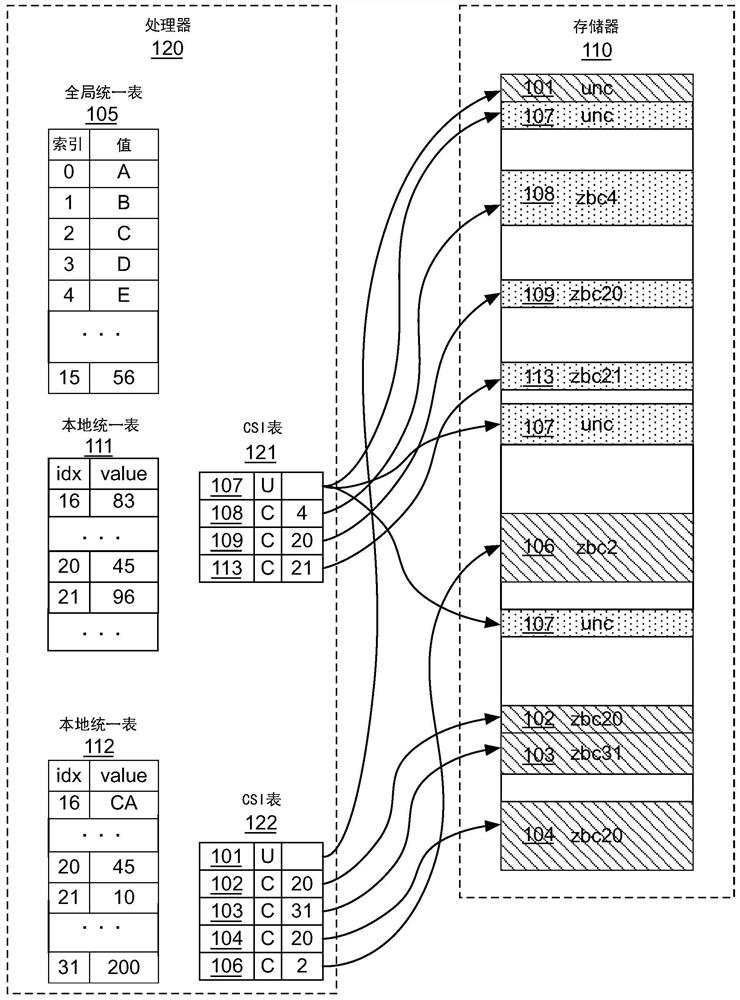

[0021] Figure 1A An exemplary system including a processor 120 and a memory 110 according to an embodiment of the disclosure is shown. In the context described below, a region is a portion of memory associated with a local uniform table (eg local uniform table 111 or 112). All regions are associated with a global consolidated table (eg, global consolidated table 105). Multiple regions may be defined within a memory such as memory 110 . In one embodiment, all regions are of equal size. In another embodiment, the regions may ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More