Batch detection device for bus interface boards

A technology of batch detection and bus interface, which is applied in the field of measurement and control, can solve the problems of long time for signal stability detection and low detection efficiency, and achieve automatic analysis and output, high degree of automation, stability and reliability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

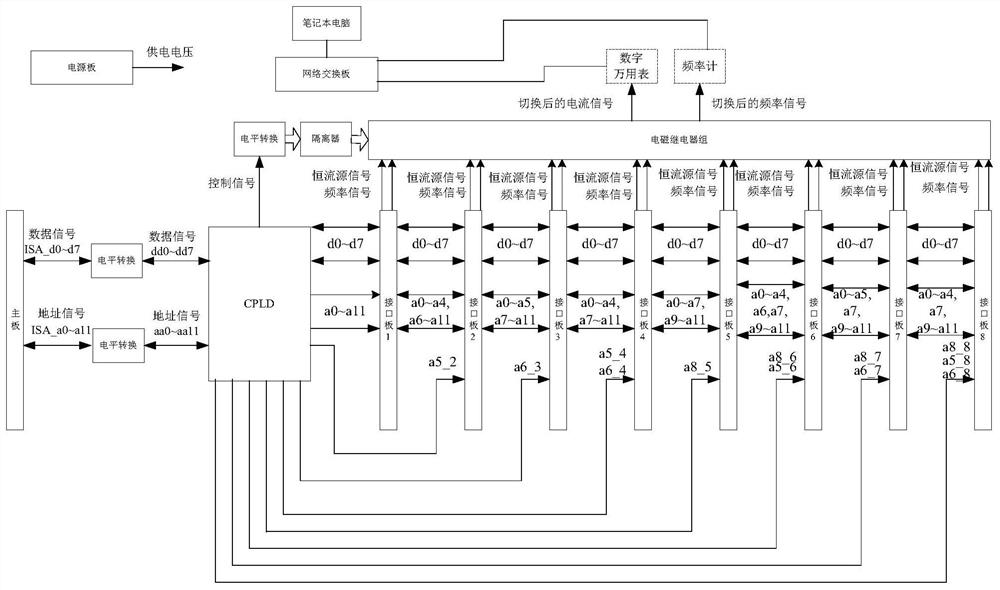

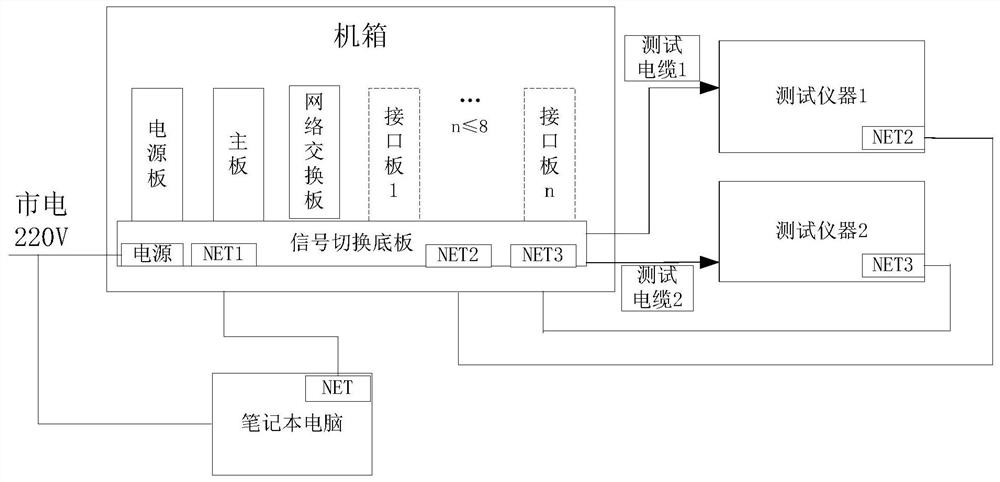

[0042]In this embodiment, eight interface boards are used to describe the device, and the type of the interface board is an ISA bus interface board. In this example, the signals to be detected by the ISA bus interface board are mainly constant current source signals and frequency signals. The required test instruments are a multimeter (current file) and a frequency meter.

[0043] The patent example of the present invention needs to detect 8 identical interface boards at the same time, and the software and hardware states of the 8 interface boards are exactly the same, that is, the board IDs are the same, so it is necessary to switch the CPLD on the bottom board to the 8 interface boards through signal switching The address is decoded to realize the redistribution of the address space, and it is mapped in the address space of the motherboard. Realize the one-to-one correspondence between the main board and each interface board signal, so as to realize the control and interpre...

Embodiment 2

[0070] In this embodiment, the simultaneous testing of board 1, board 2, and board 3 is taken as an example to illustrate the decoding of the CPLD.

[0071] There are address bus and data bus connected between the three boards and the main board, among which the data bus (d0-d7, 8 bits in total) is exactly the same, and each interface board is directly connected to the main board. The address bus is divided into a common bus and a special bus. The common address bus is directly connected, and the special address bus is connected after being decoded by the CPLD. The address bus of the main board has a total of 12 bits, a0-a11, the address bus of interface board 1 is a0-a11; the address bus of interface board 2 is a0-a4, a5_2, a6-a11; the address bus of interface board 3 is a0-a5 , a6_3, a7-a11; addresses a5_2 and a6_3 are the unique address lines of interface board 1 and interface board 2 respectively.

[0072] The technical status of the three interface boards is completely c...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap