Chip test mode switching method and system

A test mode and mode switching technology, applied in the field of testing, can solve problems such as increased difficulty, inability to switch, and reduced chip test coverage, so as to achieve the effect of improving coverage and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

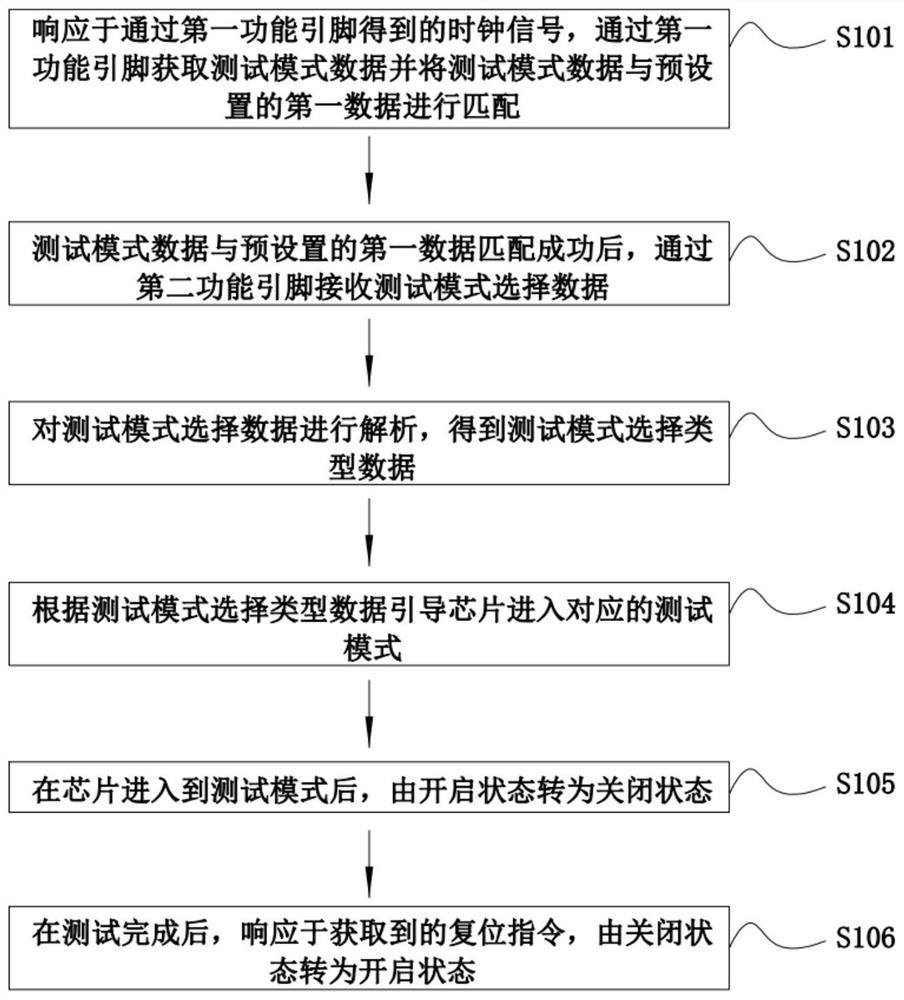

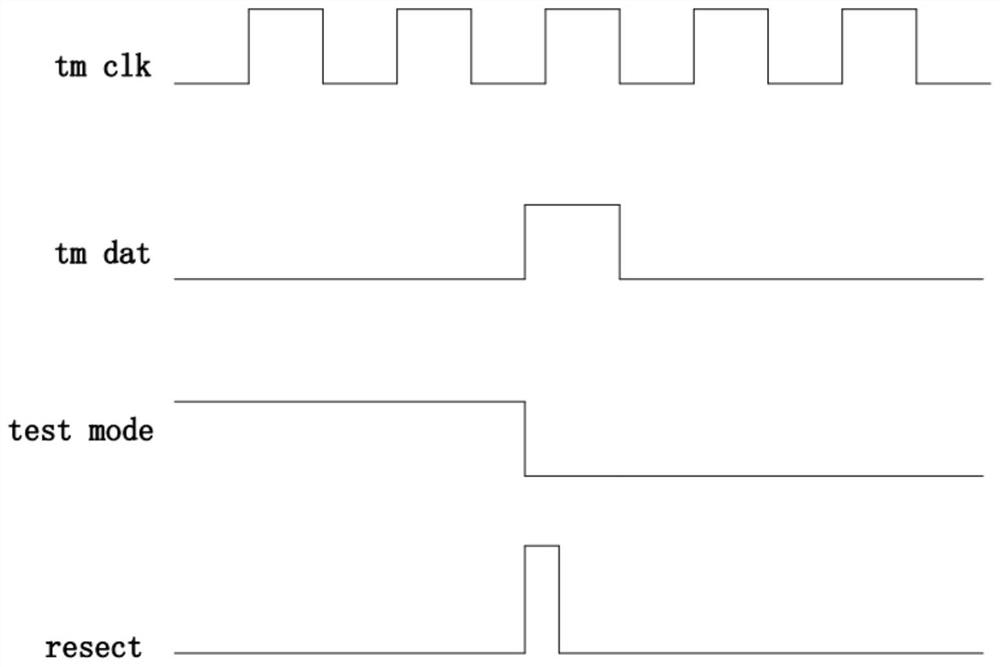

[0080] The technical solution in this application will be described in further detail below in conjunction with the accompanying drawings.

[0081] The chip test mode switching method provided by the embodiment of the present application uses the test mode data and test mode selection data to guide the chip into the test mode. The specific method is to add a monitoring unit to the chip, and the test mode issued by the tester The data is sent to the monitoring unit for judgment, and then the chip is guided into the corresponding test mode according to the test mode selection type data.

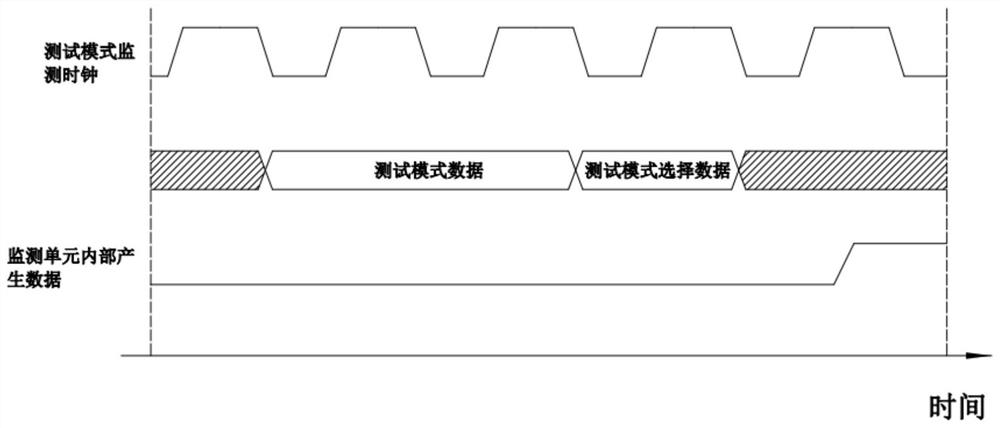

[0082] see figure 1 and figure 2 , the embodiment of the present application provides a chip test mode switching method, which is applied to the monitoring unit in the chip and multiplexes the two function pins of the chip, including the following steps:

[0083] S101, in response to the clock signal obtained through the first function pin, acquire test mode data through the first function p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More