Single event upset resistant latch circuit

An anti-single-event, flip-lock technology, applied in logic circuits, electrical components, generating electrical pulses, etc., can solve problems such as slow data transmission in circuits, and achieve the effect of single-event immunity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

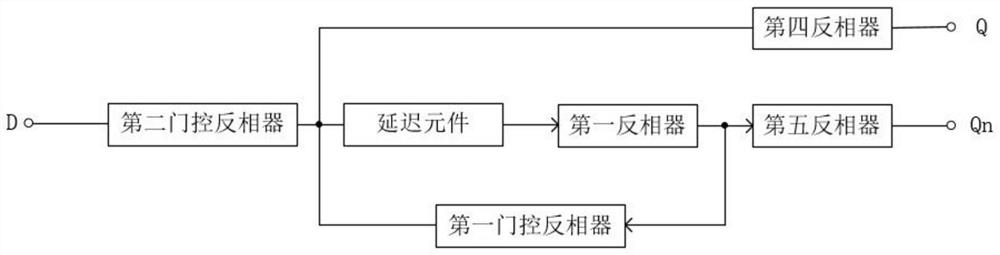

[0046] The embodiment of the present invention solves the technical problem of slow data transmission speed when the latch is hardened by a single event by providing an anti-single event flipping latch circuit.

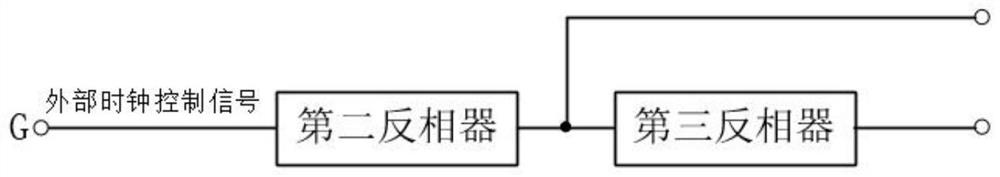

[0047] In order to better understand the technical solution of the present invention, the technical solution of the present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0048] First of all, the term "and / or" that appears in this article is just an association relationship that describes associated objects, which means that there can be three relationships, for example, A and / or B, which can mean: there is A alone, and A exists at the same time and B, there are three cases of B alone. In addition, the character " / " in this article generally indicates that the contextual objects are an "or" relationship.

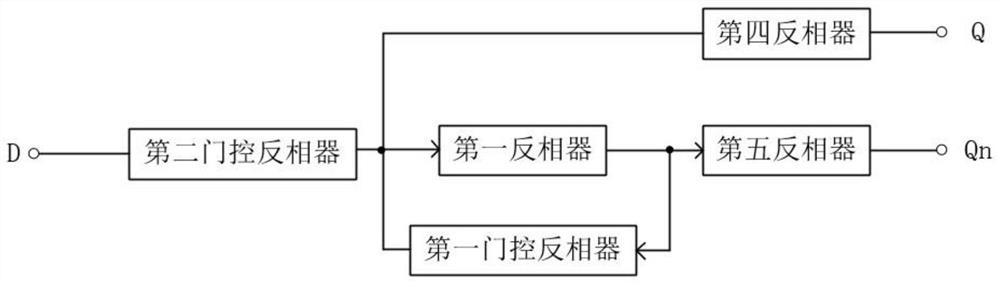

[0049] like figure 2 As shown, a common unhardened latch circuit includes a first inverter, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More