Signal processing device

一种信号处理装置、信号的技术,应用在图像通信、阴极射线管指示器、电视等方向,能够解决电路规模增大等问题,达到防止图像样式模式化的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

[0036] A signal processing device according to Embodiment 1 of the present invention will be described below with reference to the drawings.

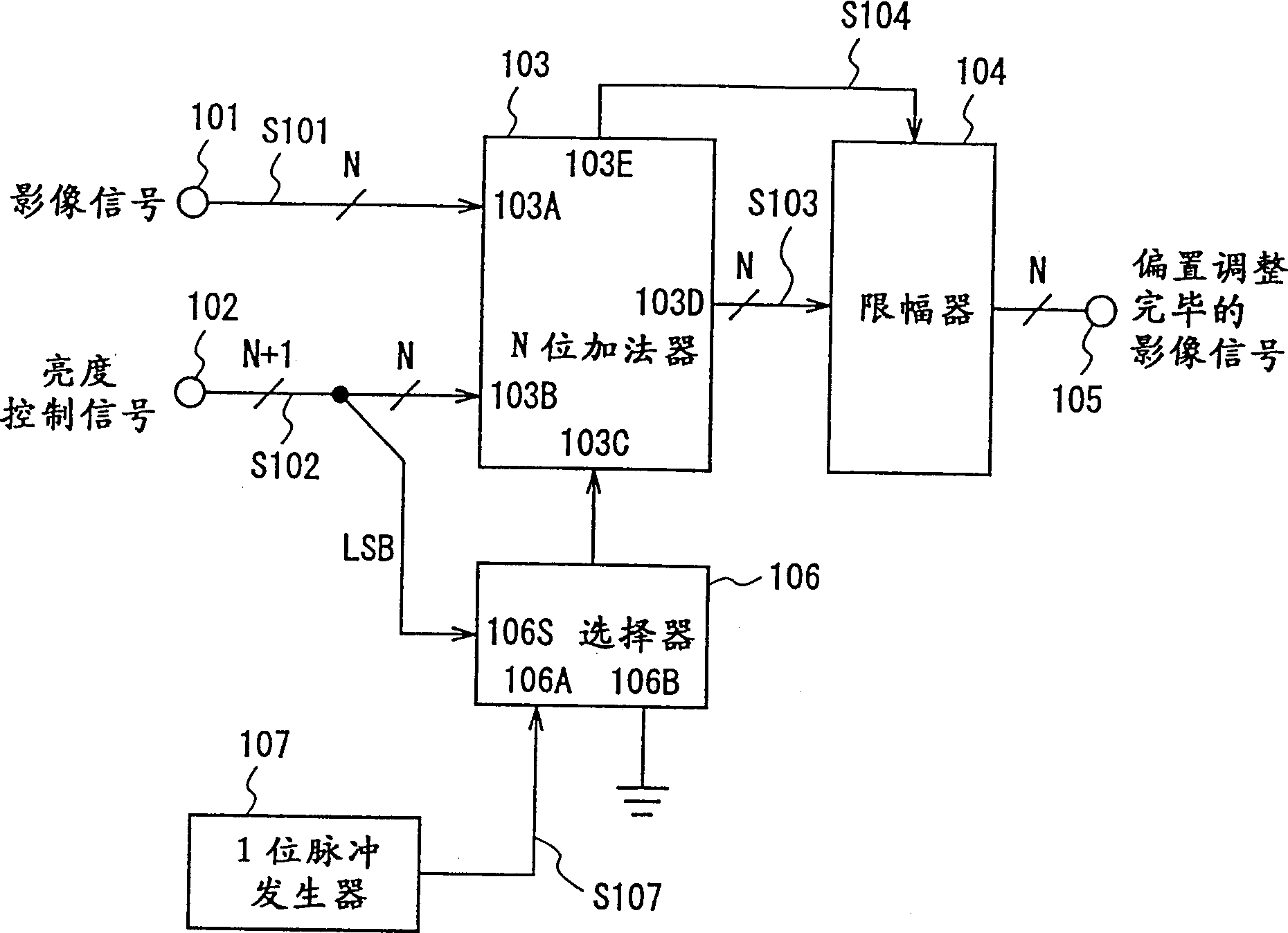

[0037] figure 1 It is a block diagram showing a signal processing device according to Embodiment 1 of the present invention.

[0038] exist figure 1 Among them, the structure of the signal processing device in this embodiment includes: an N-bit adder 103 , a limiter 104 , a selector 106 and a 1-bit pulse generator 107 .

[0039] The N-bit adder 103 adds the N-bit image signal S101 supplied to the input 103A, the upper N-bit signal of the N+1-bit luminance control signal S102 supplied to the input 103B, and the carry input supplied to the input 103C. Then, the addition result is output from output 103D as N-bit signal S103. And, in the addition operation, when an overflow occurs, the overflow 1 bit, that is, the most significant bit of the N+1 bits of the addition result is output from the carry output 103E as the carry output signa...

Embodiment approach 2

[0059] Next, a signal processing device according to Embodiment 2 of the present invention will be described with reference to the drawings. The signal processing device according to Embodiment 2 of the present invention is an example of the 1-bit pulse generator 107 according to Embodiment 1, and generates a 1-bit pulse signal using a vertical synchronization signal, a horizontal synchronization signal, and a pixel clock signal.

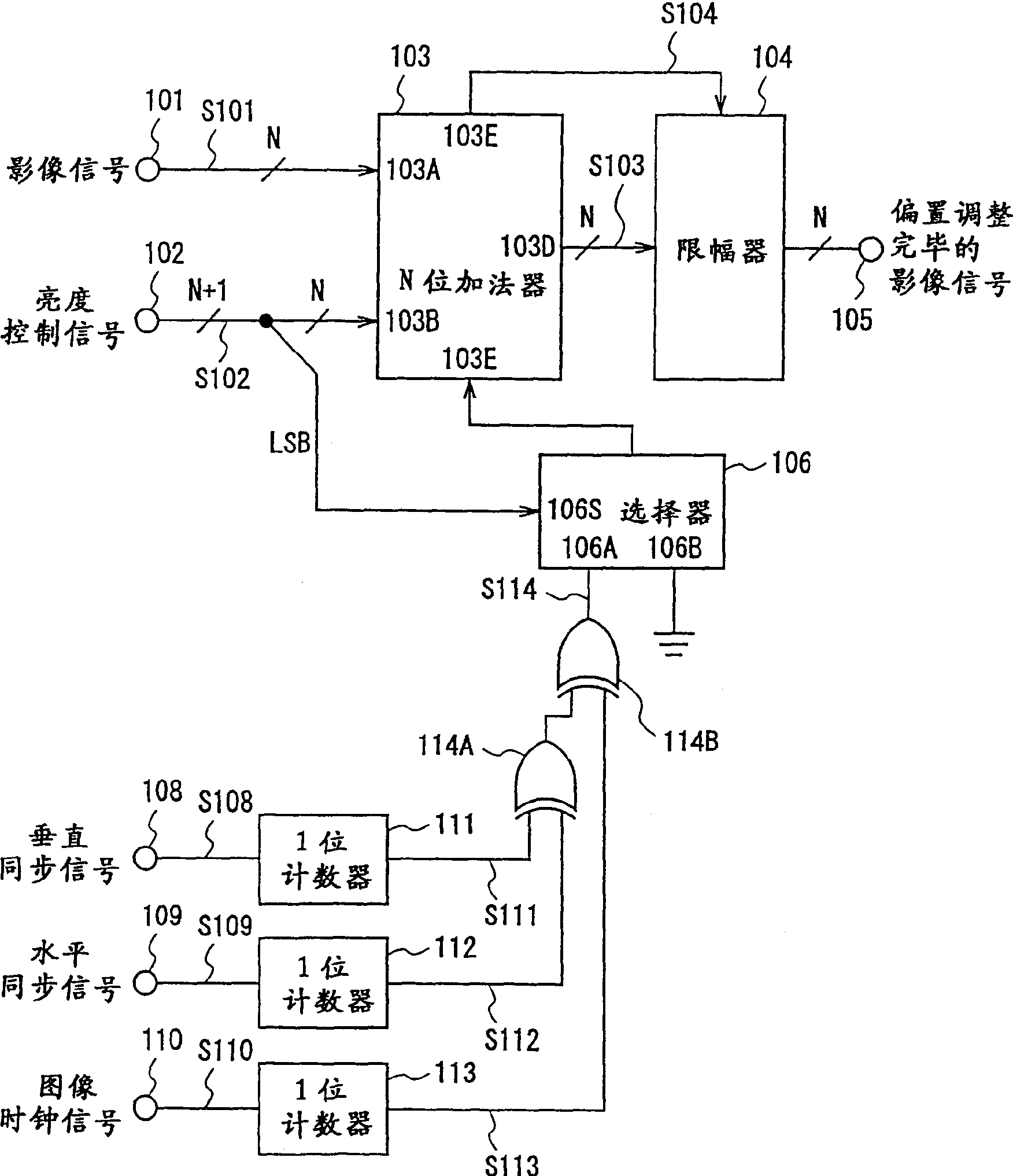

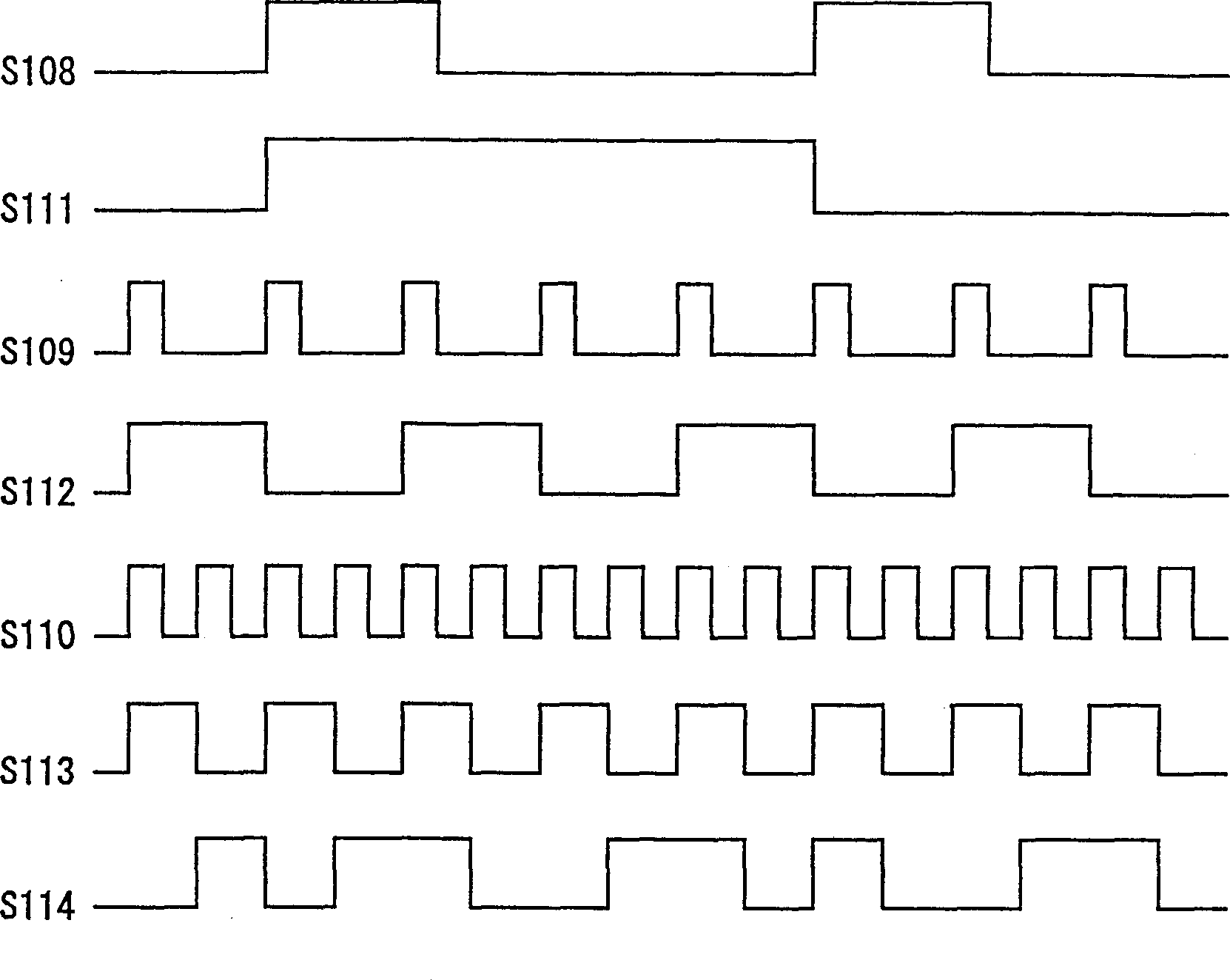

[0060] figure 2 It is a block diagram showing a signal processing device according to Embodiment 2 of the present invention.

[0061] exist figure 2 Among them, the configuration of the signal processing device according to Embodiment 2 includes: N-bit adder 103, limiter 104, selector 106, 1-bit counters 111, 112, 113, and OR gates 114A, 114B. In addition, the configuration and operation of the N-bit adder 103, the limiter 104, and the selector 106 are the same as those in Embodiment 1, and the description thereof will not be repeated.

[0062]...

Embodiment approach 3

[0079] Next, a signal processing device according to Embodiment 3 of the present invention will be described with reference to the drawings.

[0080] Figure 4 It is a block diagram showing a signal processing device according to Embodiment 3 of the present invention.

[0081] exist Figure 4 Among them, the configuration of the signal processing device according to the third embodiment includes: an N-bit adder 103 , a limiter 104 , a selector 115 and a pulse generator 116 . In addition, the configuration and operation of the N-bit adder 103 and the limiter 104 are the same as those in Embodiment 1, and the description thereof will not be repeated.

[0082] The selector 115, according to the M-bit control signal, from 2 M Any one of the input signals is selected, and the selection signal is output to the N-bit adder 103. Here, one input of the selector 115 is grounded. In addition, M is an integer greater than 1.

[0083] Pulse generator 116, the ratio of the period duri...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More