Device and method of branch for processing branch goal address high speed area covering crossed instruction high speed line

A technology of branch target address and target address, which is applied in the field of branch instructions, can solve problems such as complex situations, and achieve the effect of avoiding branch loss and improving branch performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

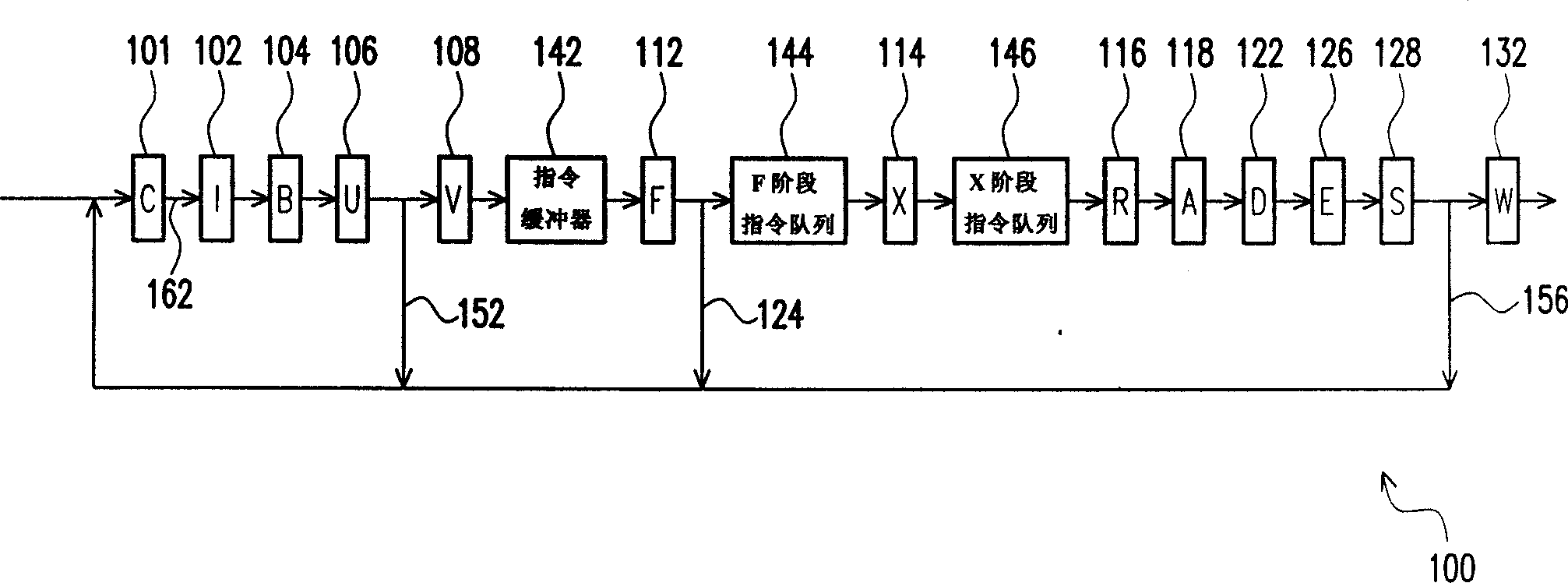

[0032] now refer to figure 1 , which is a block diagram of a microprocessor 100 with a pipeline according to the present invention. Microprocessor 100 includes a number of stages from 101 to 132 . In one embodiment, the microprocessor 100 includes an x86 architecture processor.

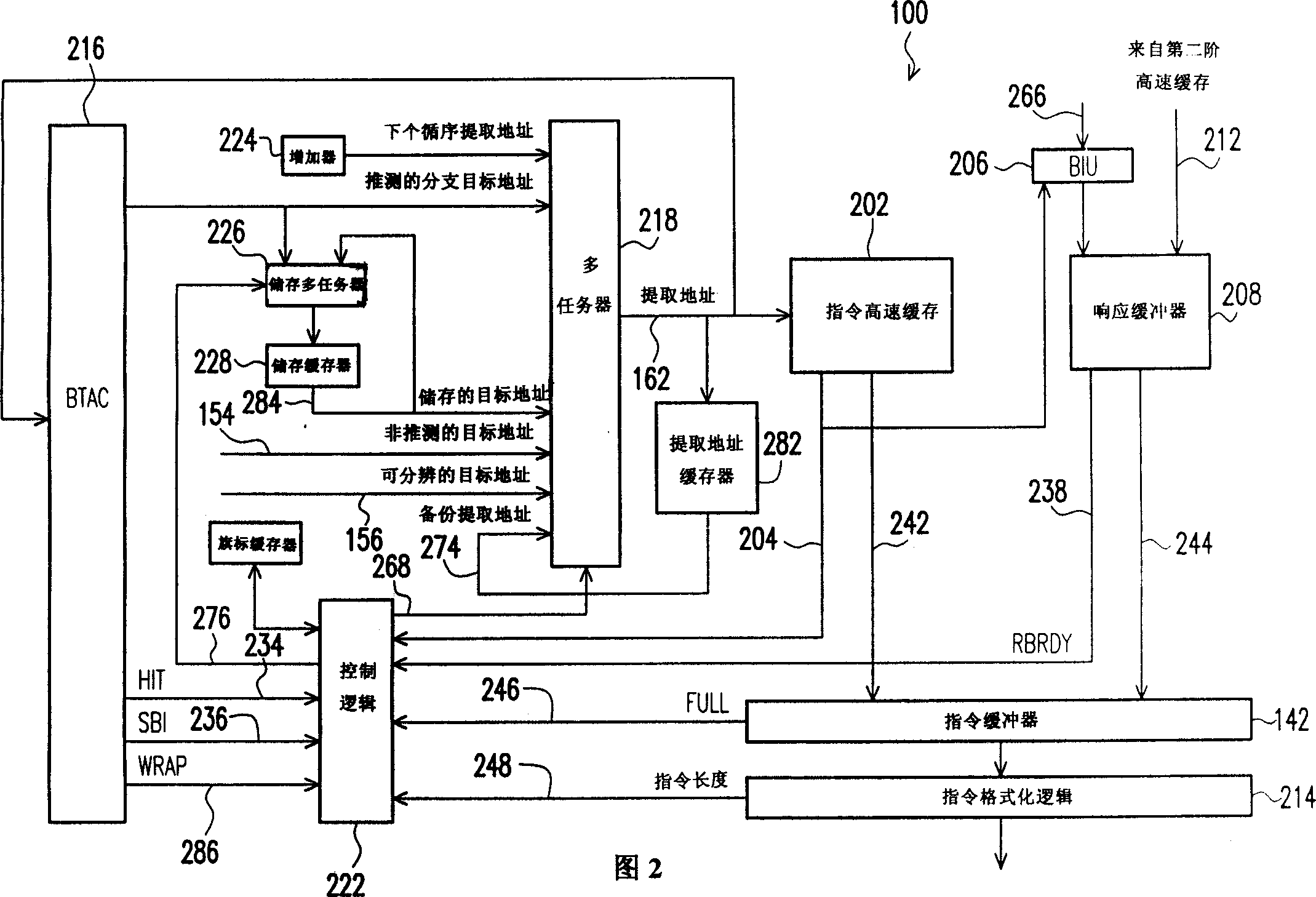

[0033] The first stage of the pipeline processor 100 is the instruction cache generation stage or C stage 101 for short. The C stage 101 generates the fetch address 162 used to select a high-speed line in the instruction cache 202 (see FIG. 2).

[0034] The next stage is the I stage 102, or the instruction fetch stage. In order to fetch instructions to the pipeline processor 100 for execution, the I stage 102 provides the stage for the pipeline processor 100 to fetch the address 162 to the instruction cache 202 (see FIG. 2 ). The instruction cache 202 will be described in more detail with reference to FIG. 2 . In one embodiment, the instruction cache 202 is a two-cycle cache. Stage B 104 is the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com