Patents

Literature

59 results about "Branch target address cache" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

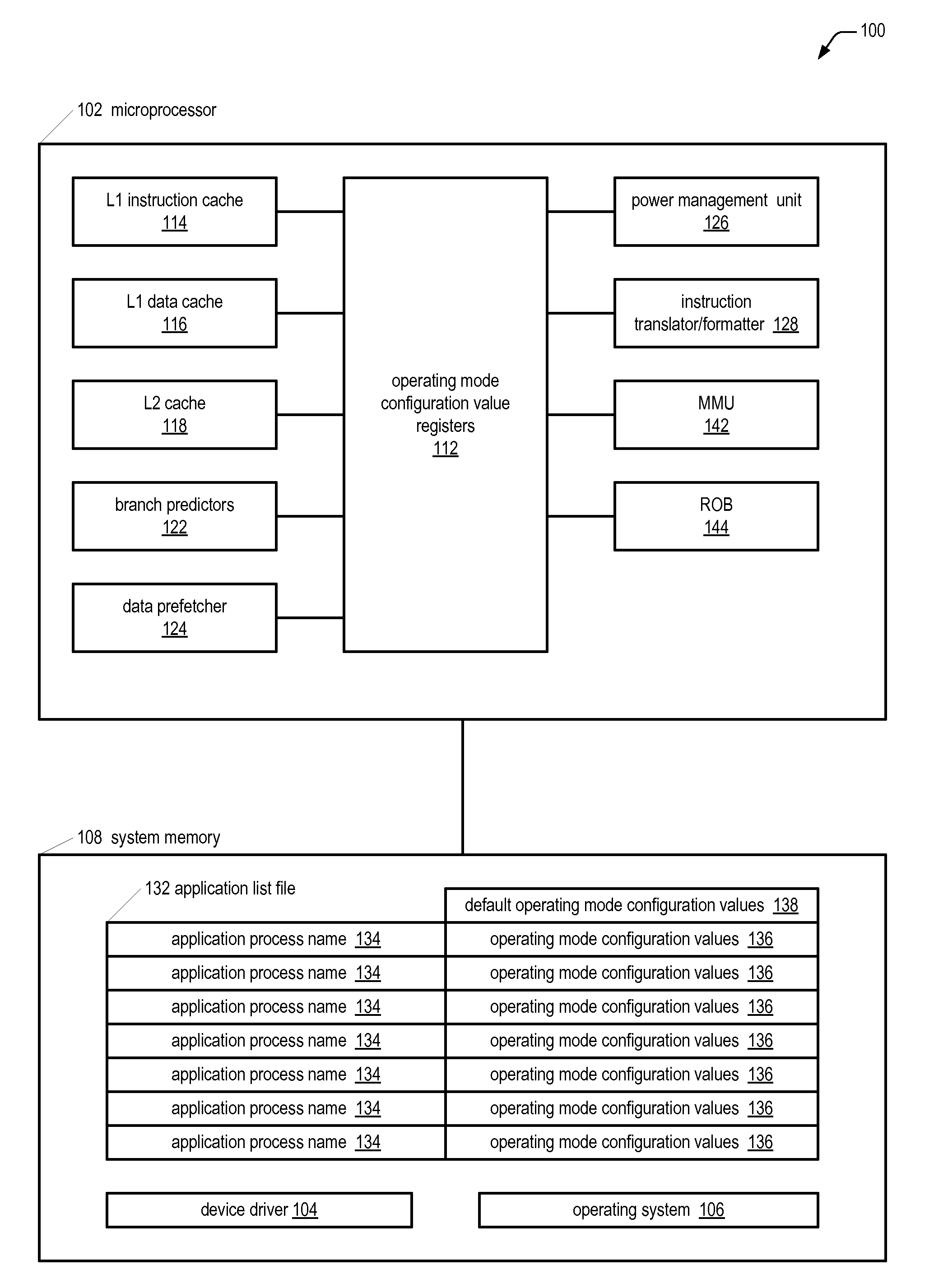

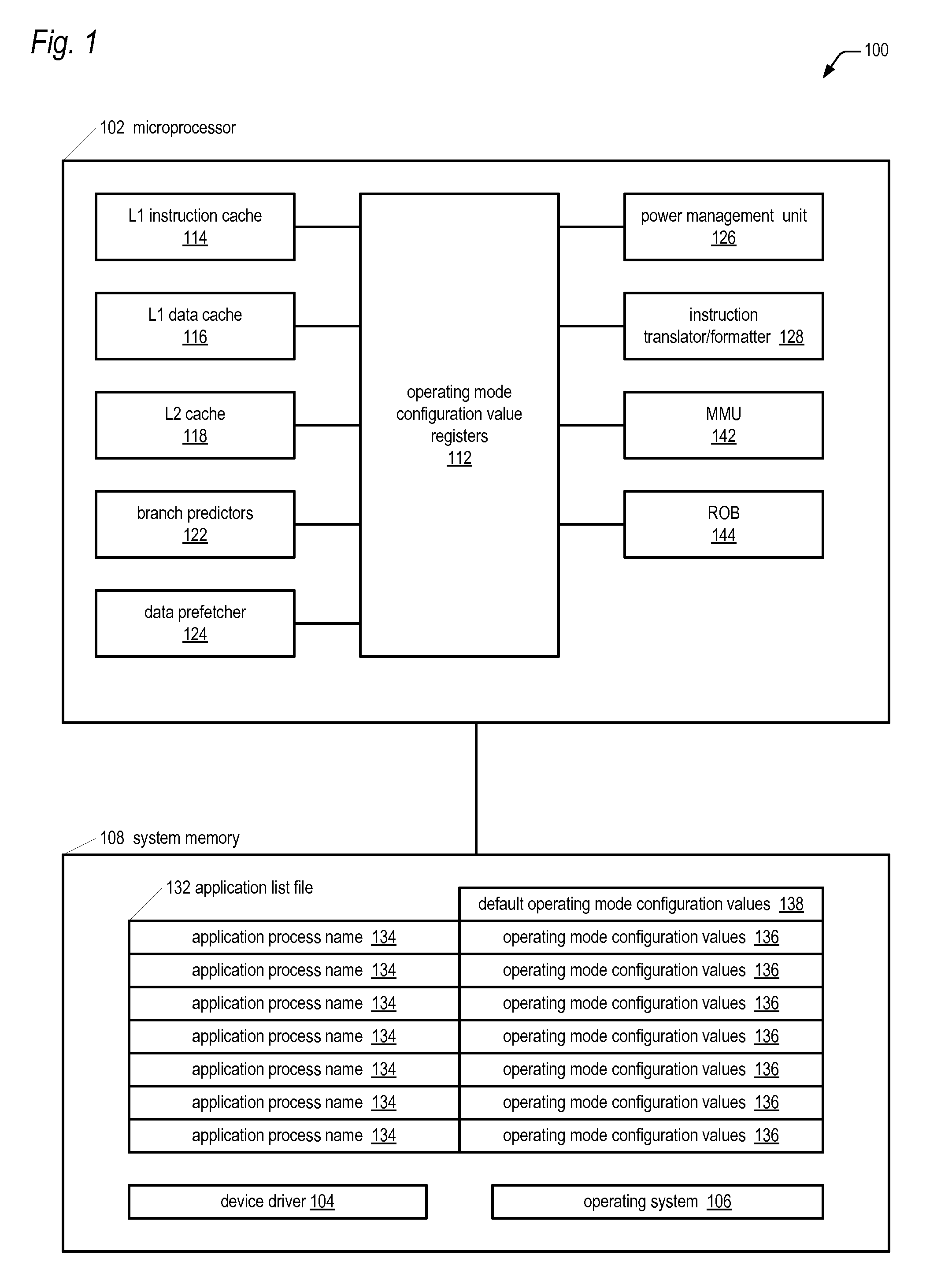

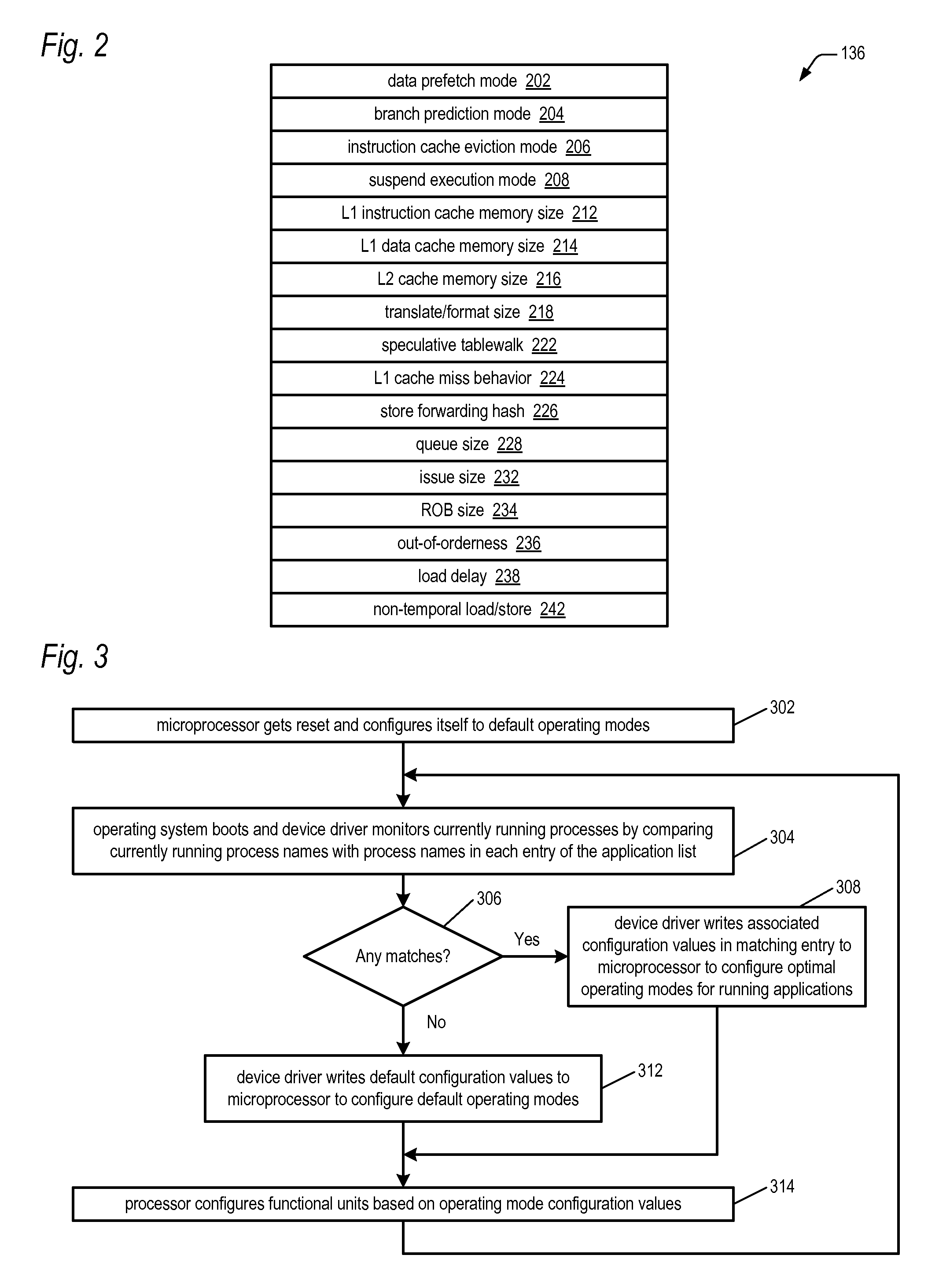

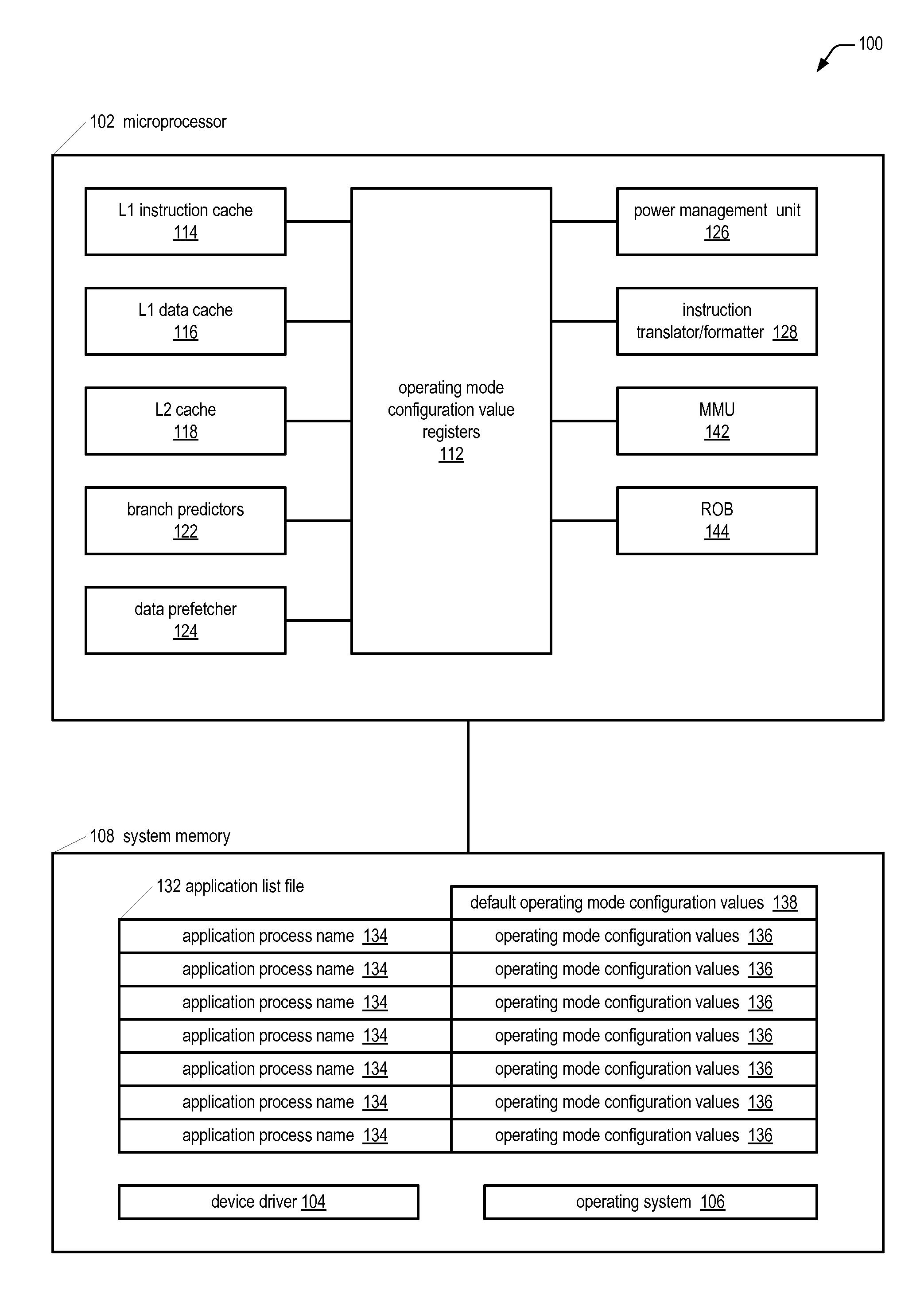

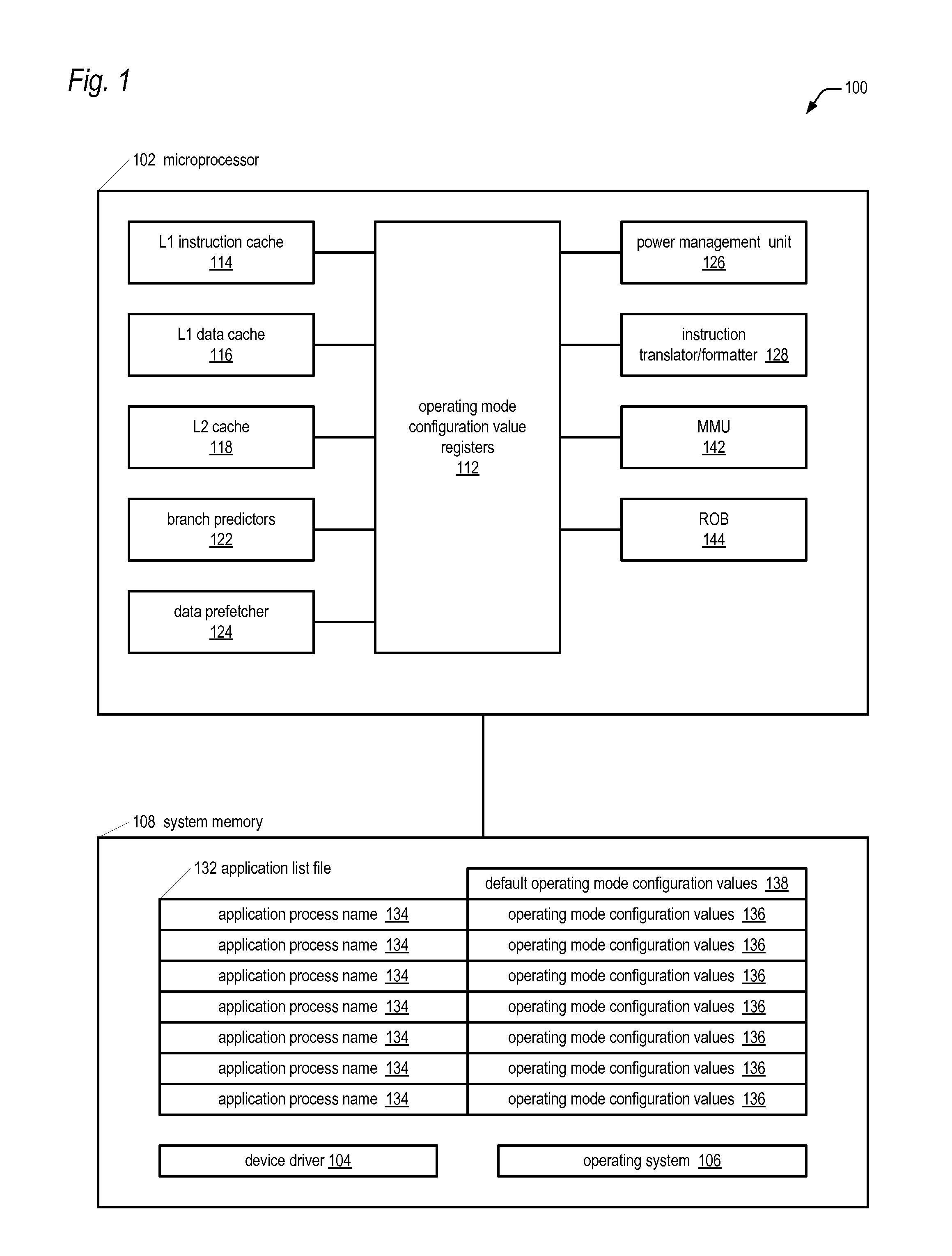

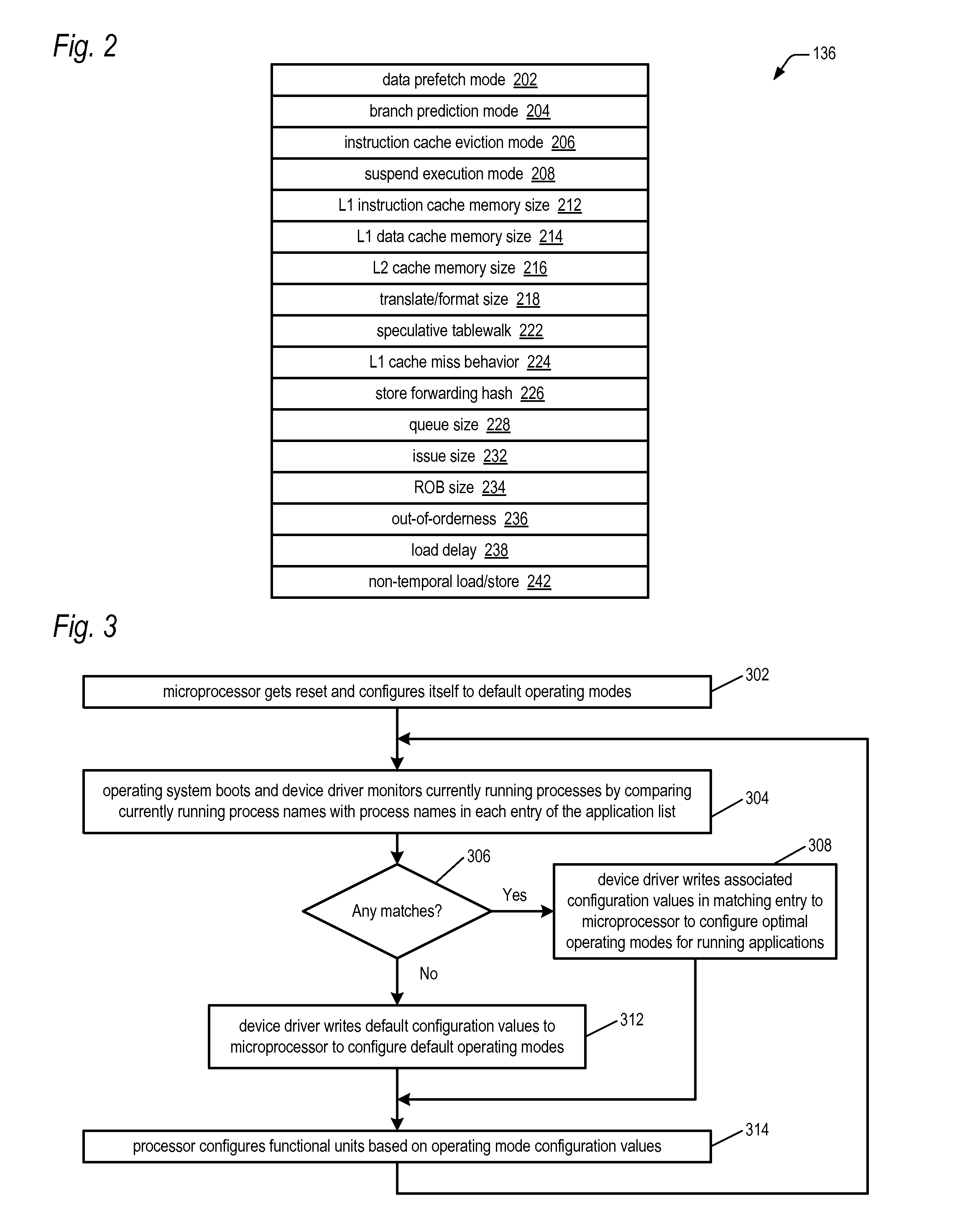

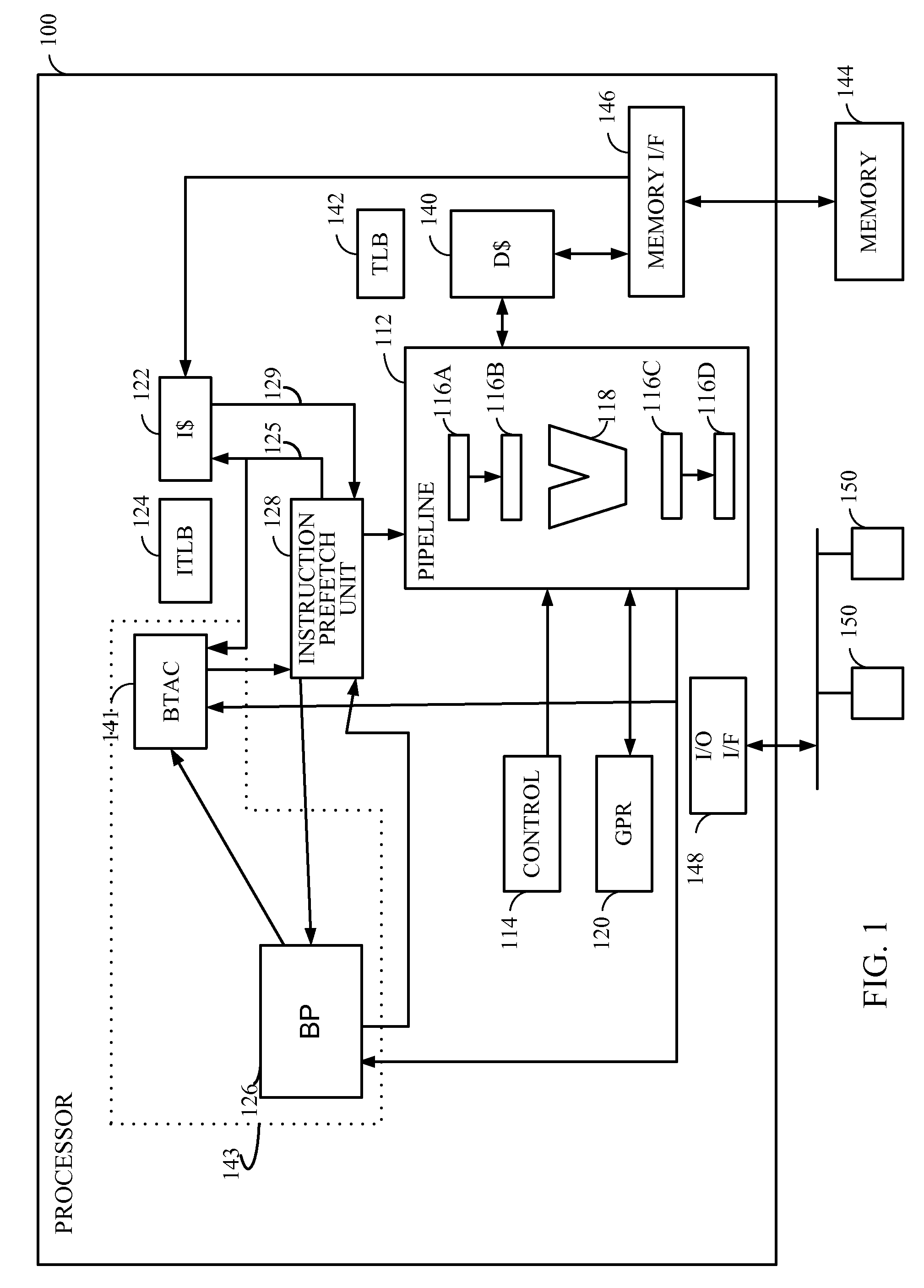

Microprocessor with multiple operating modes dynamically configurable by a device driver based on currently running applications

ActiveUS20100011198A1Improve performanceReduce power consumptionRuntime instruction translationMemory adressing/allocation/relocationBranch target address cacheApplication software

A computing system includes a microprocessor that receives values for configuring operating modes thereof. A device driver monitors which software applications currently running on the microprocessor are in a predetermined list and responsively dynamically writes the values to the microprocessor to configure its operating modes. Examples of the operating modes the device driver may configure relate to the following: data prefetching; branch prediction; instruction cache eviction; instruction execution suspension; sizes of cache memories, reorder buffer, store / load / fill queues; hashing algorithms related to data forwarding and branch target address cache indexing; number of instruction translation, formatting, and issuing per clock cycle; load delay mechanism; speculative page tablewalks; instruction merging; out-of-order execution extent; caching of non-temporal hinted data; and serial or parallel access of an L2 cache and processor bus in response to an instruction cache miss.

Owner:VIA TECH INC

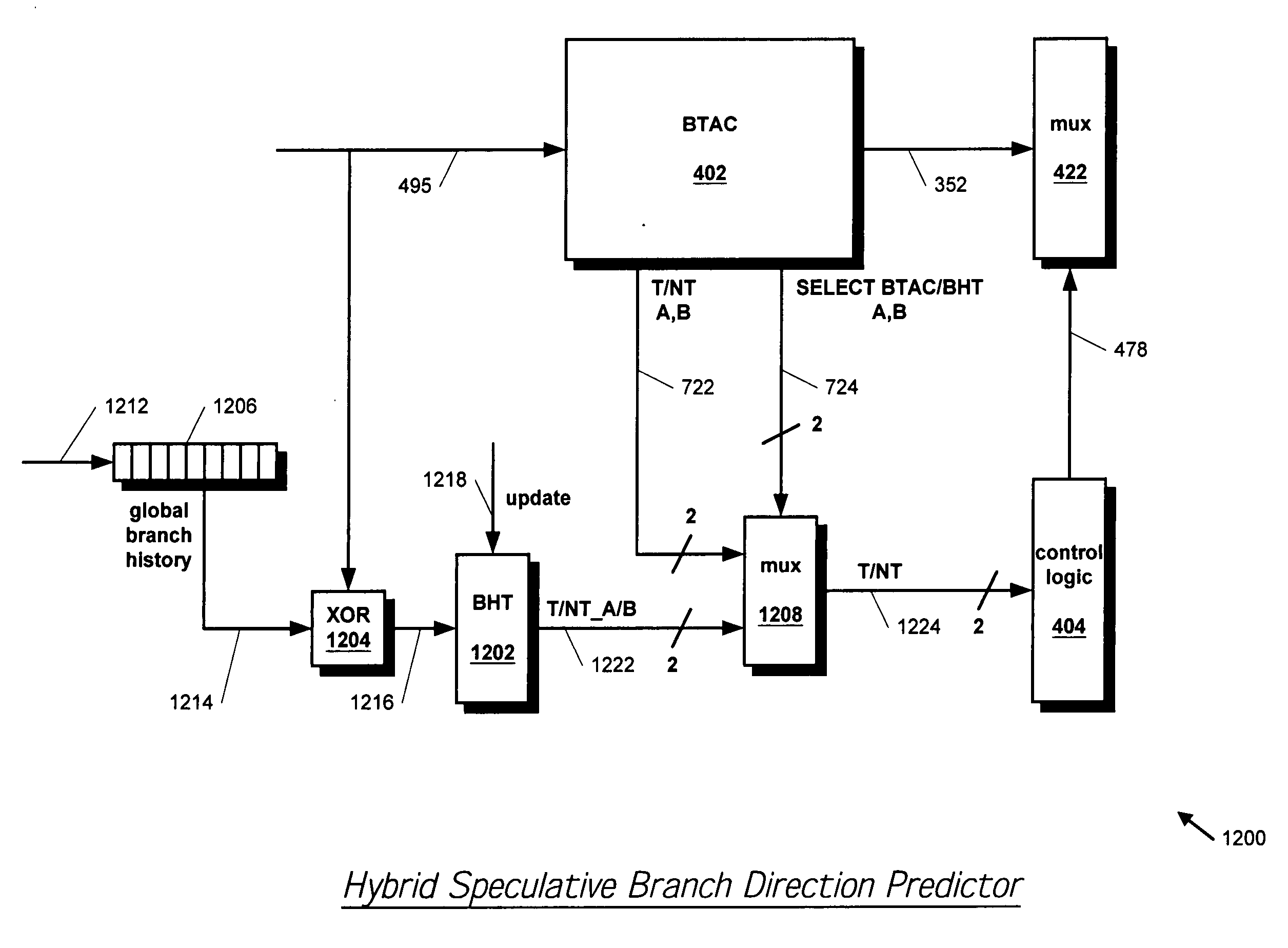

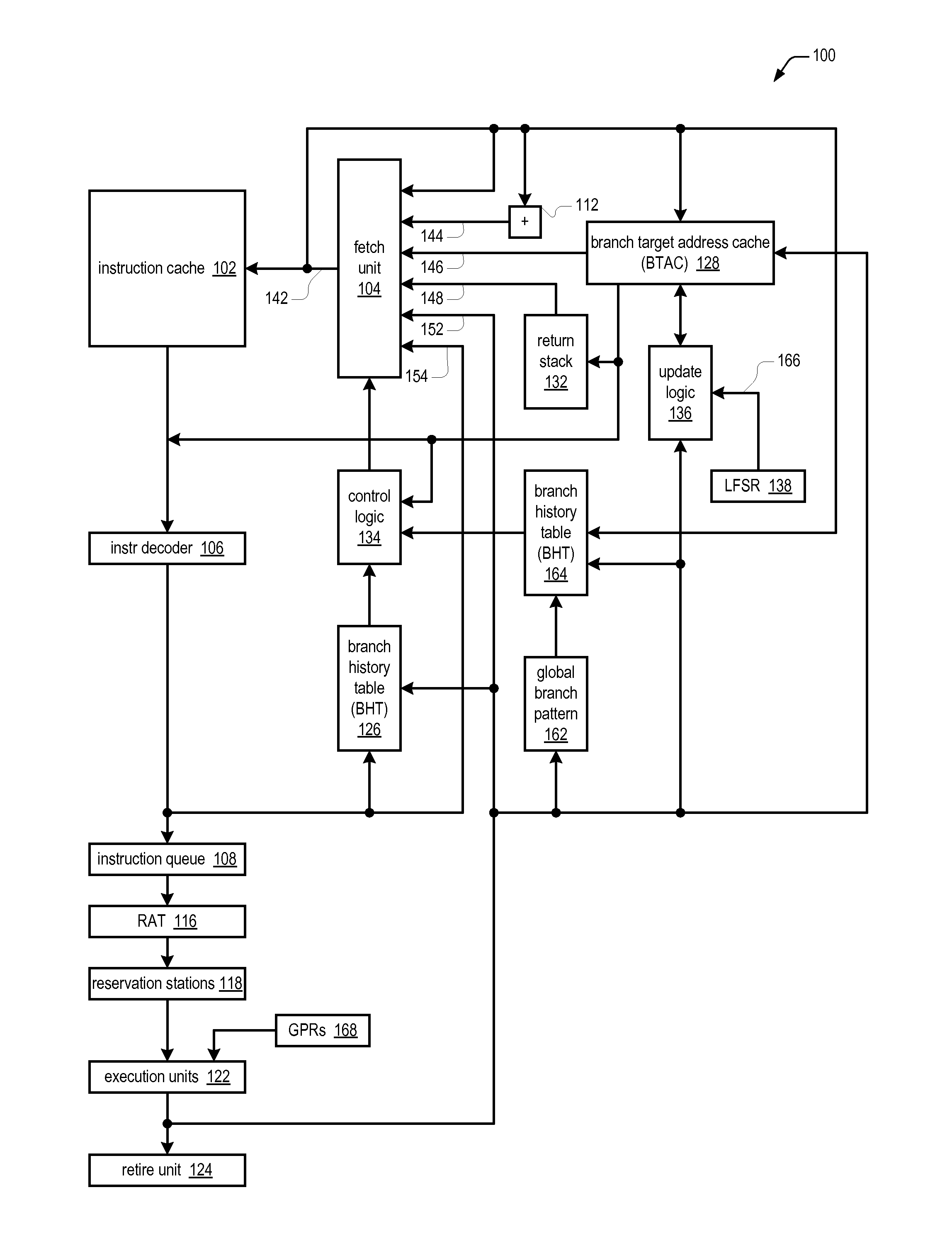

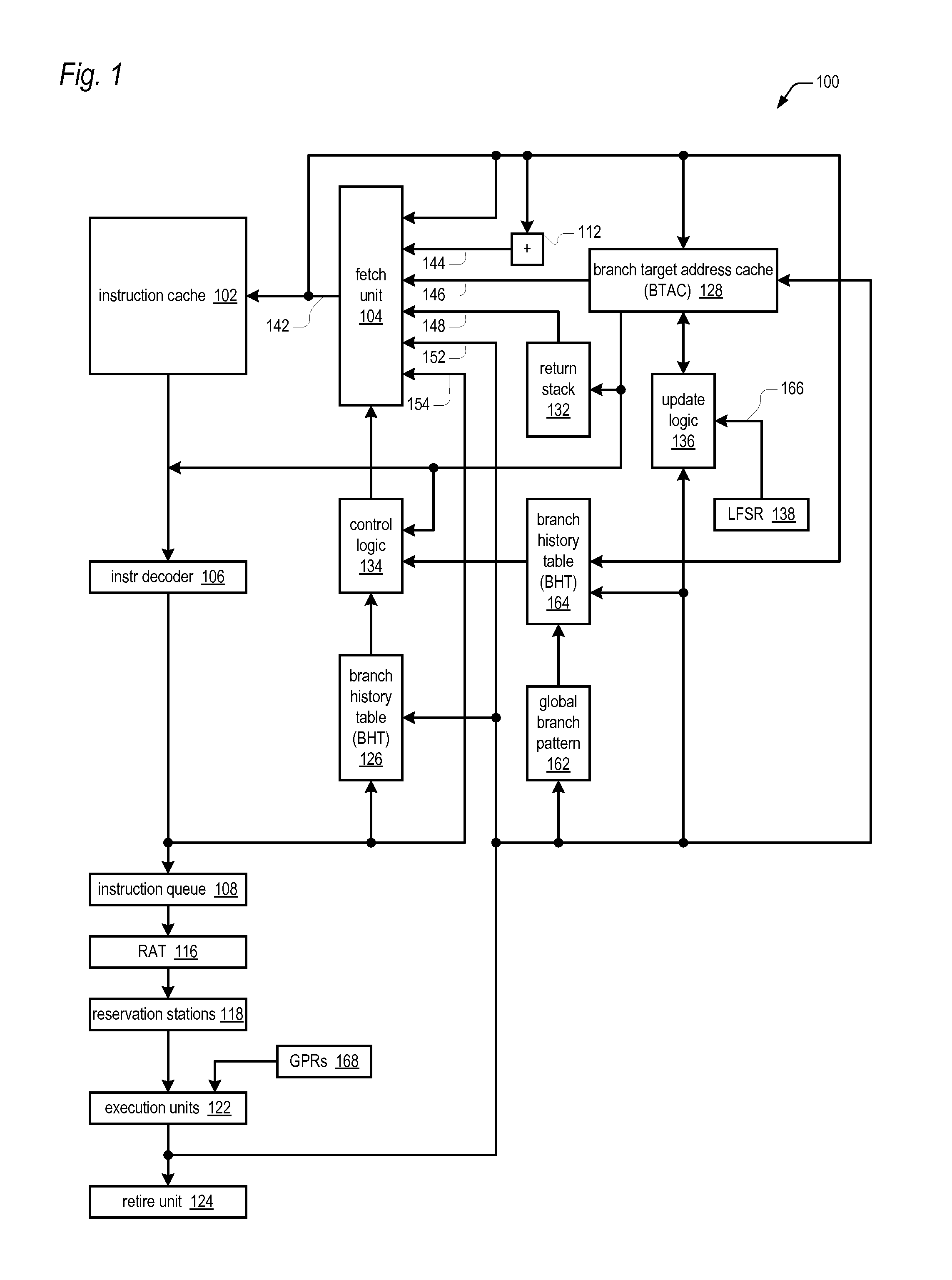

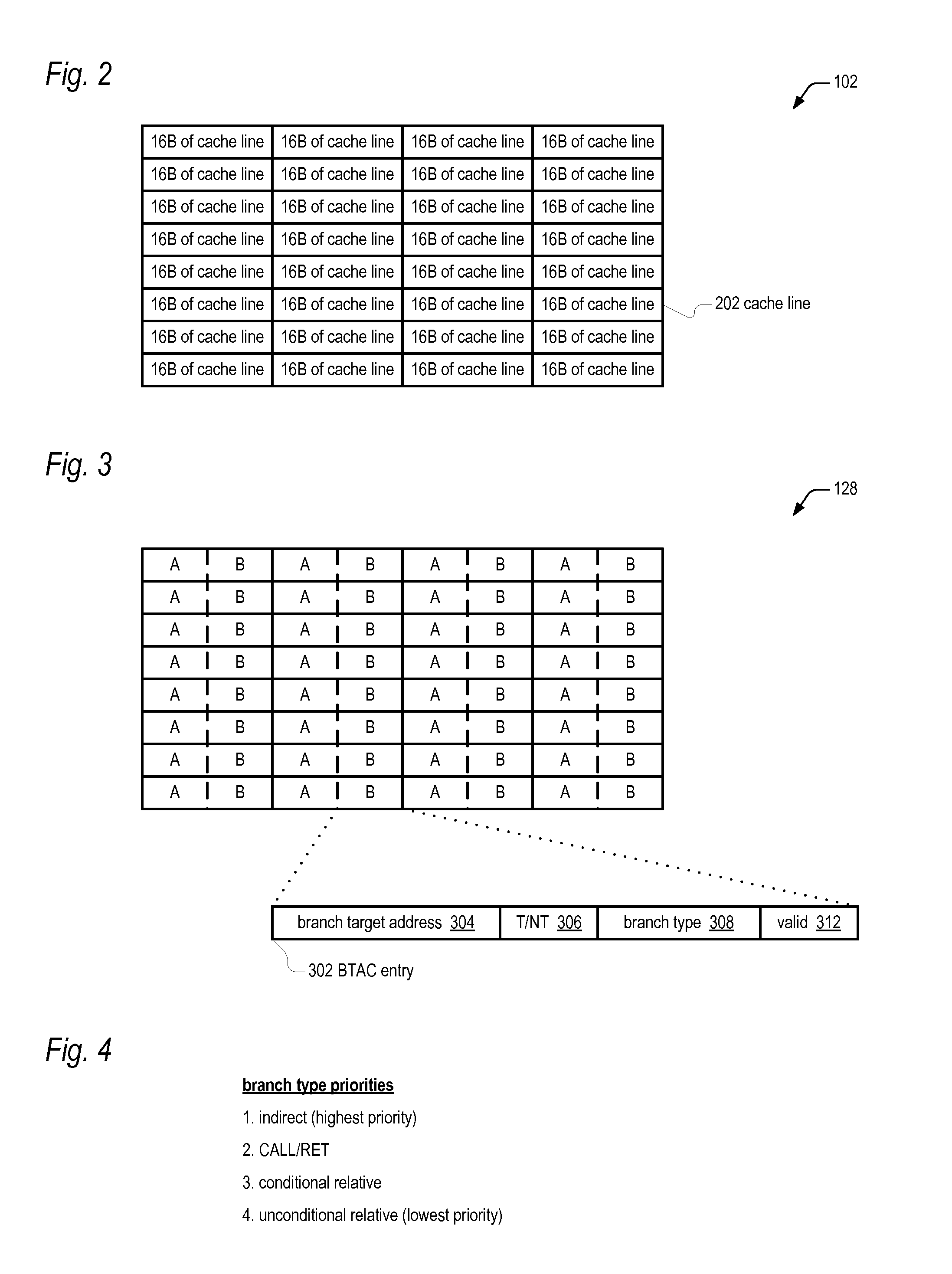

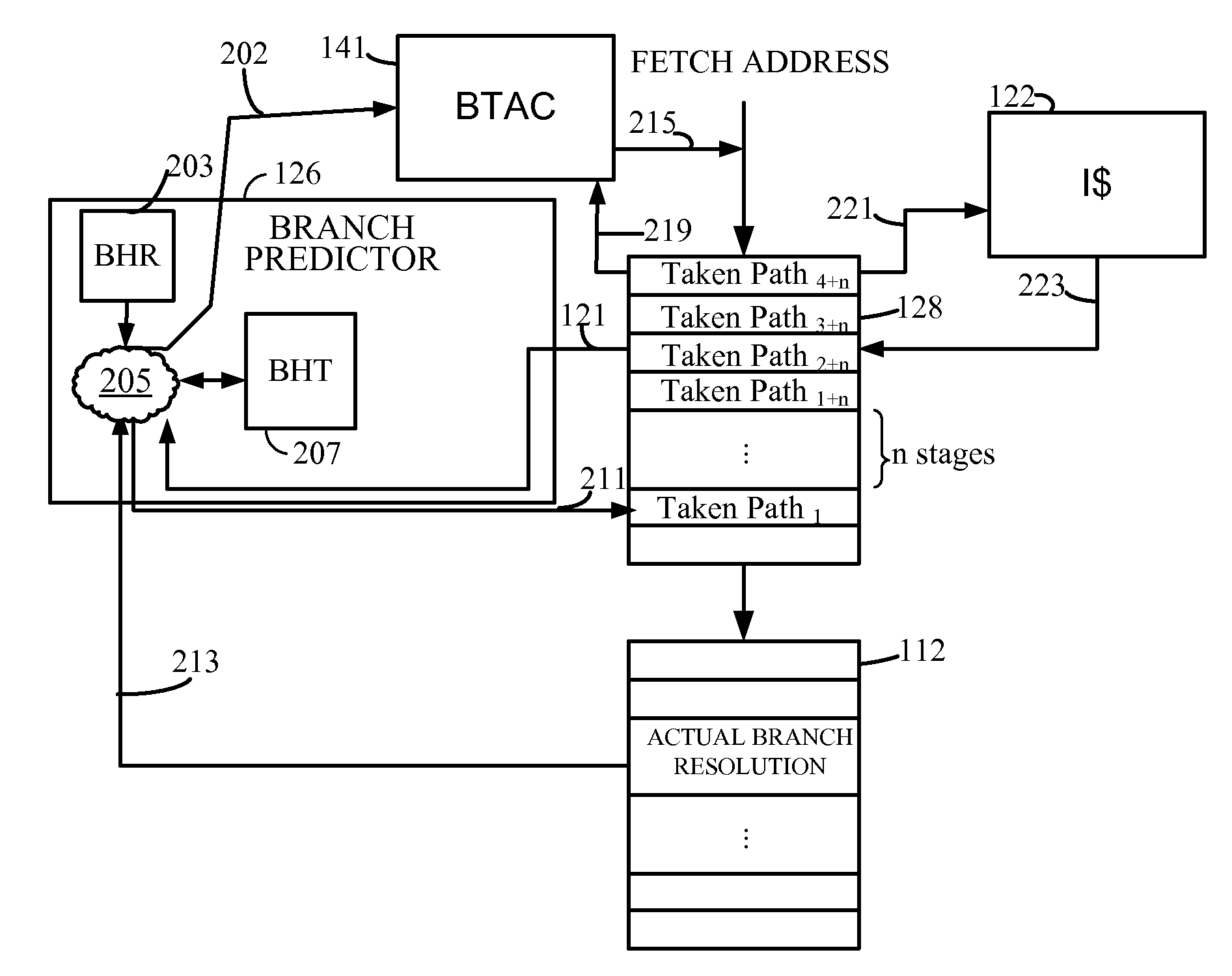

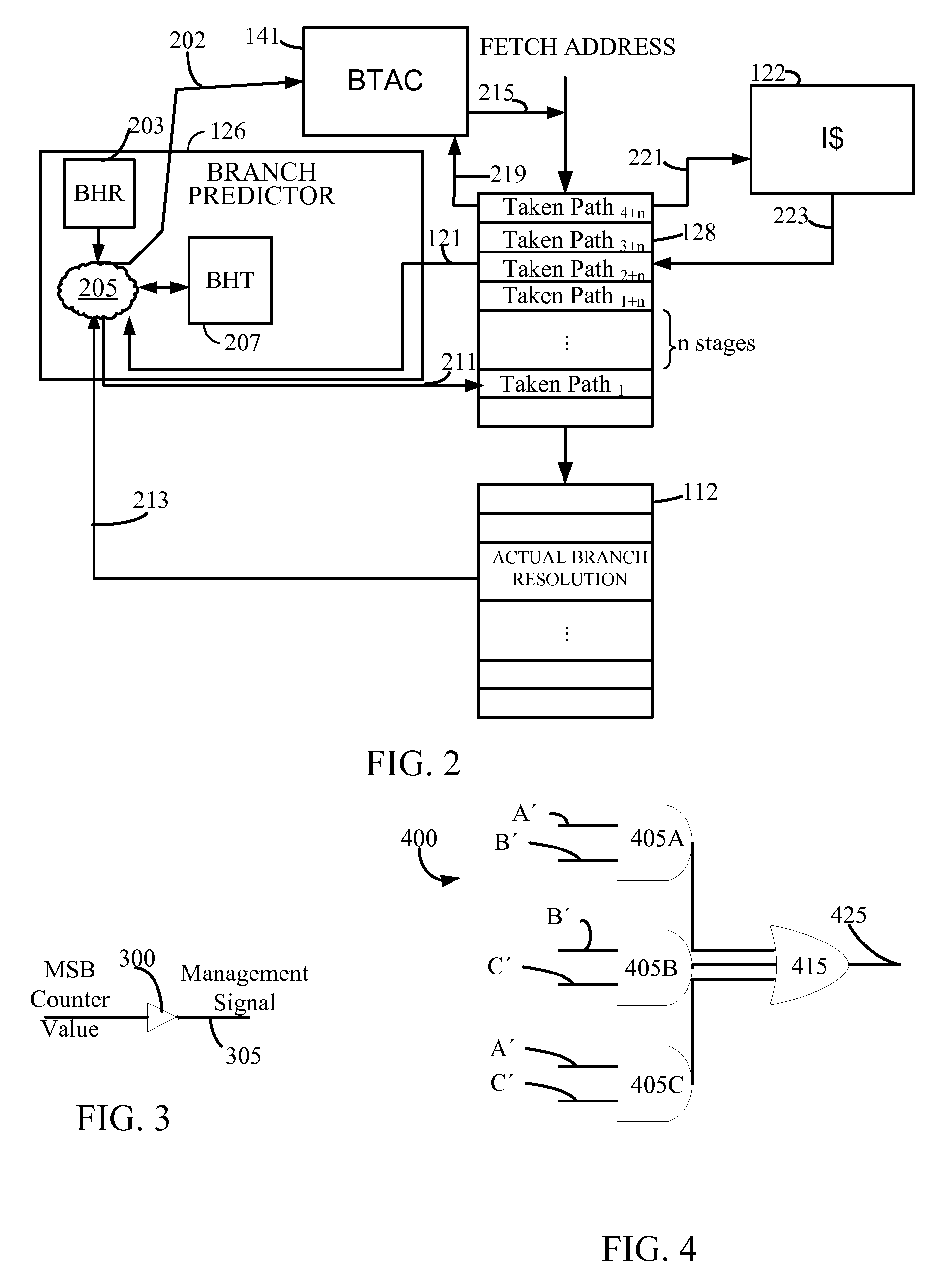

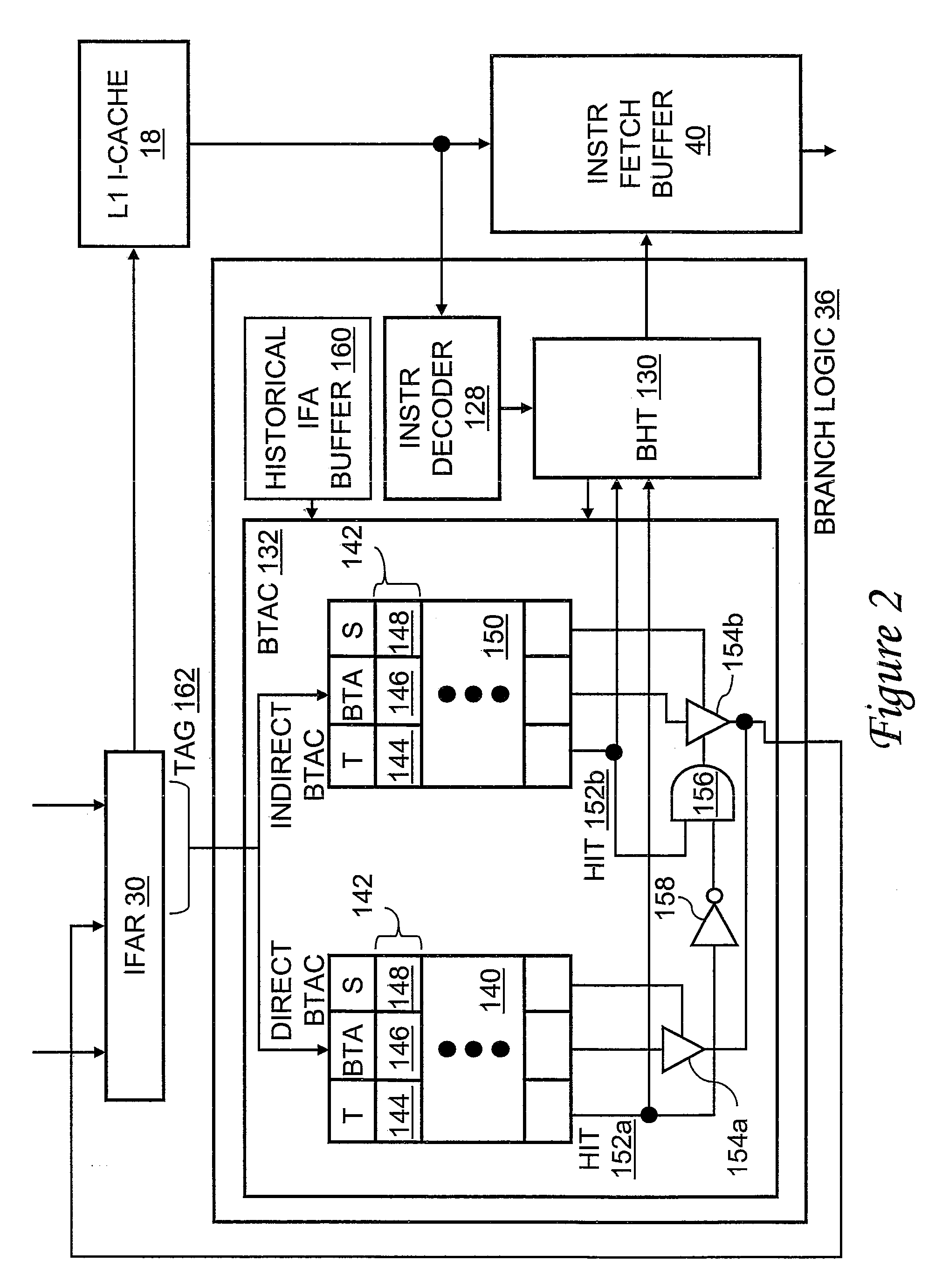

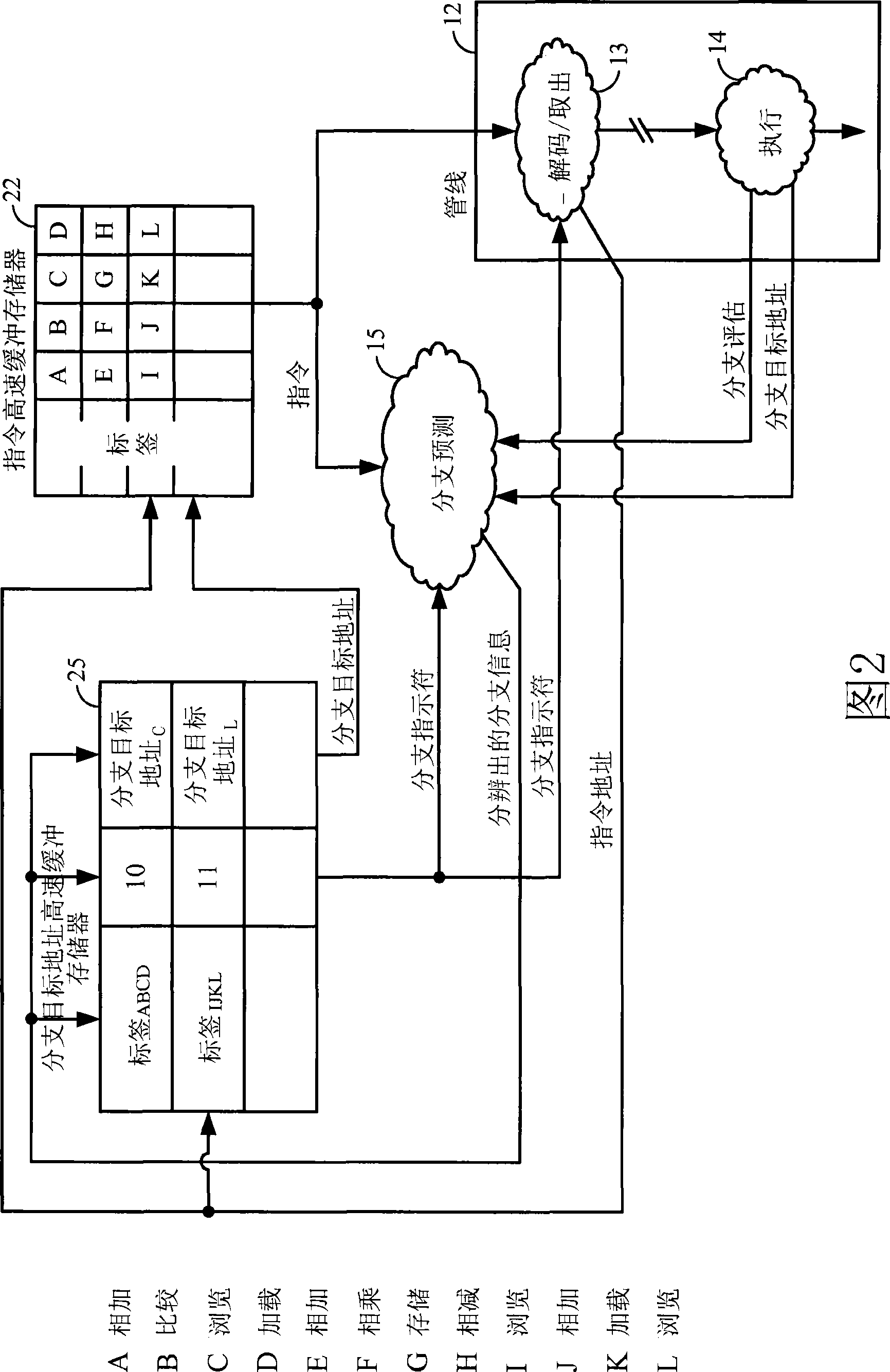

Speculative hybrid branch direction predictor

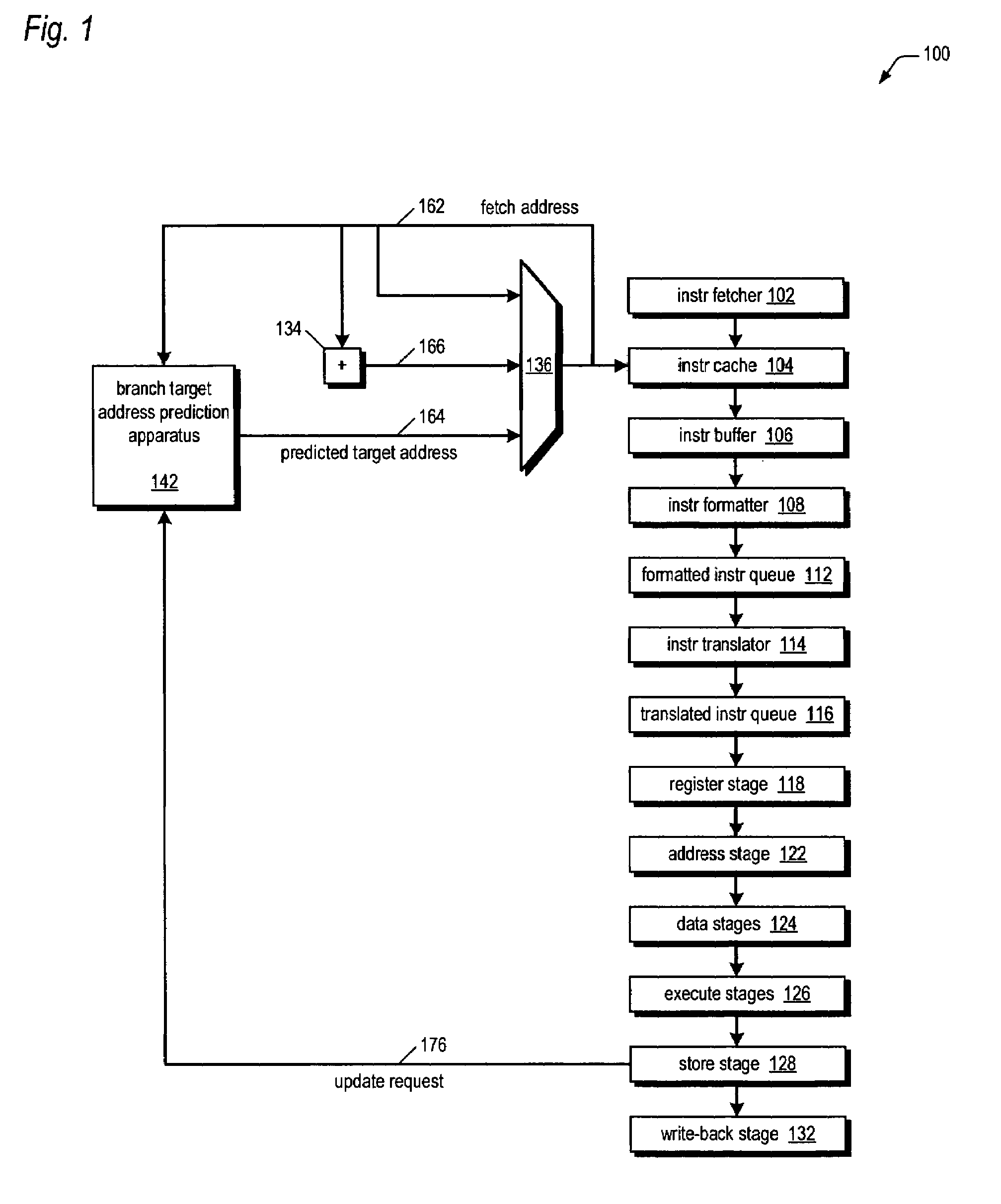

InactiveUS20050132175A1Improve accuracyReducing overall branch penaltyInstruction analysisDigital computer detailsCache accessParallel computing

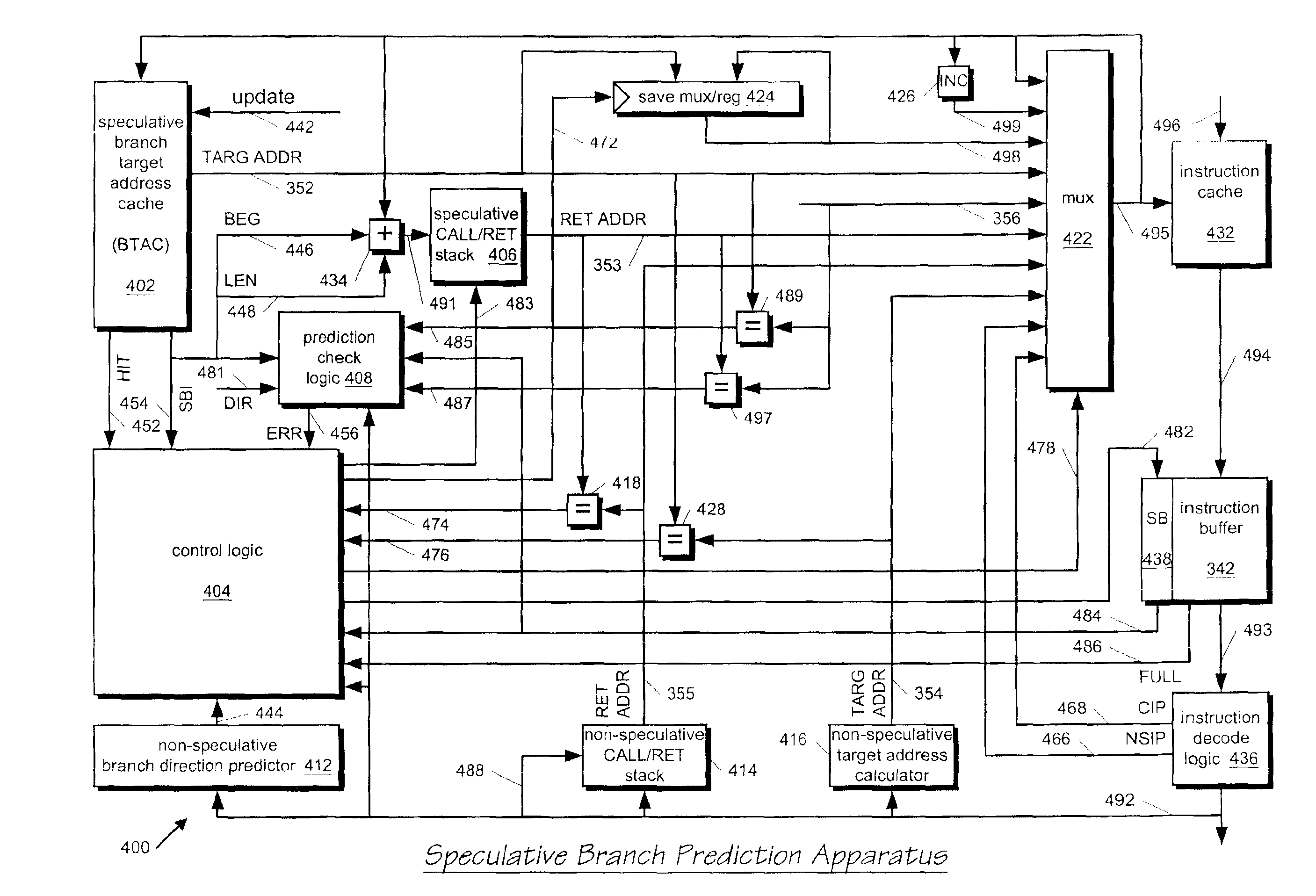

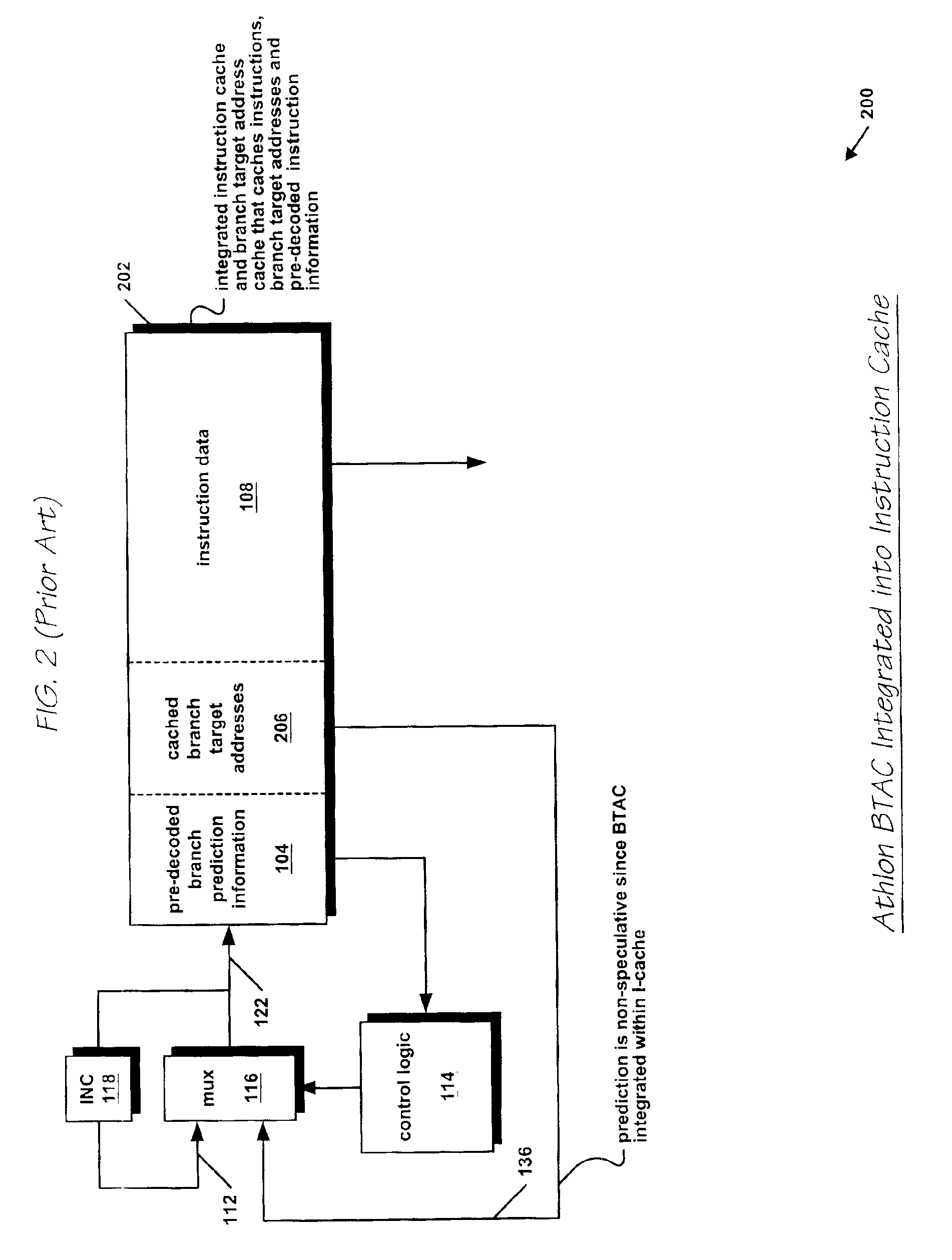

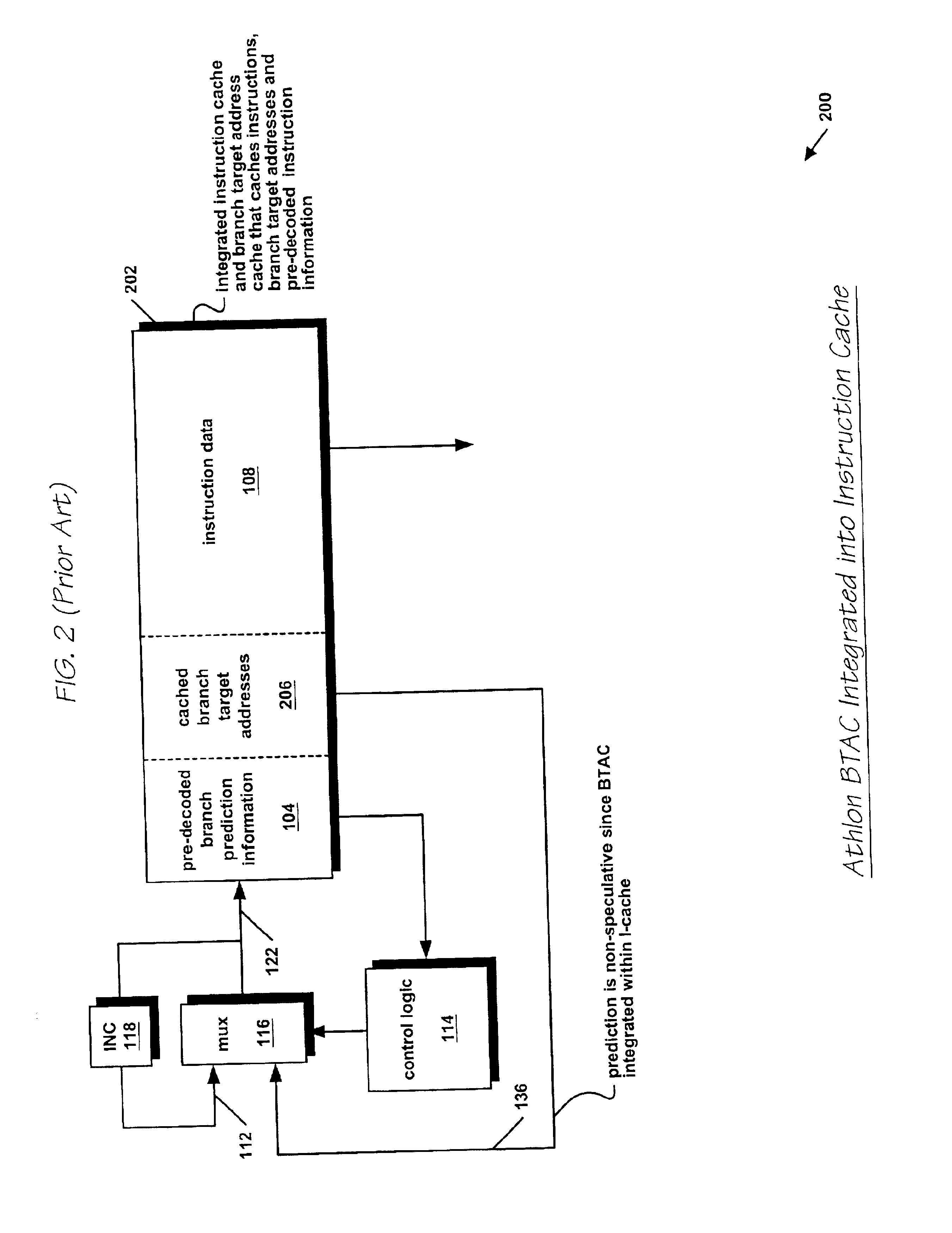

An apparatus for speculatively predicting the direction of a branch instruction in a pipelined microprocessor in a hybrid fashion. A branch target address cache (BTAC) stores a direction prediction about executed branch instructions. The BTAC is indexed by an instruction cache fetch address. The BTAC is accessed in parallel with the instruction cache access, such that the direction prediction is provided before the actual instruction is decoded which is presumed to be a branch instruction corresponding to the direction prediction stored in the BTAC. In parallel with the BTAC access, a branch history table (BHT) is accessed to provide a second speculative direction prediction. The BHT is indexed with a gshare function of the instruction cache fetch address and a global branch history stored in a global branch history register. The BTAC also provides a selector that selects between the two speculative direction predictions.

Owner:IP FIRST

Speculative hybrid branch direction predictor

InactiveUS6886093B2Improve accuracyReducing overall branch penaltyInstruction analysisDigital computer detailsCache accessProcessor register

An apparatus for speculatively predicting the direction of a branch instruction in a pipelined microprocessor in a hybrid fashion. A branch target address cache (BTAC) stores a direction prediction about executed branch instructions. The BTAC is indexed by an instruction cache fetch address. The BTAC is accessed in parallel with the instruction cache access, such that the direction prediction is provided before the actual instruction is decoded which is presumed to be a branch instruction corresponding to the direction prediction stored in the BTAC. In parallel with the BTAC access, a branch history table (BHT) is accessed to provide a second speculative direction prediction. The BHT is indexed with a gshare function of the instruction cache fetch address and a global branch history stored in a global branch history register. The BTAC also provides a selector that selects between the two speculative direction predictions.

Owner:IP FIRST

Apparatus and method for target address replacement in speculative branch target address cache

InactiveUS6895498B2Easy to useMemory adressing/allocation/relocationDigital computer detailsProcessor registerBranch target address cache

An apparatus and method in a pipelined microprocessor for replacing one of two target addresses in a branch target address cache (BTAC) line. If only one of the two entries is invalid, the invalid entry is replaced. If both entries are valid, the least recently used entry is replaced. If both entries are invalid, the entry is replaced corresponding to the side of the BTAC, indicated by a global status register, not last written to with an invalid entry. In one embodiment, the global status is updated only if a side is written when both entries are invalid. In another embodiment, the BTAC stores N entries per line, where N is greater than 1. The status register maintains information for determining which of the N sides is least recently written. The least recently written side is chosen for replacement.

Owner:IP FIRST

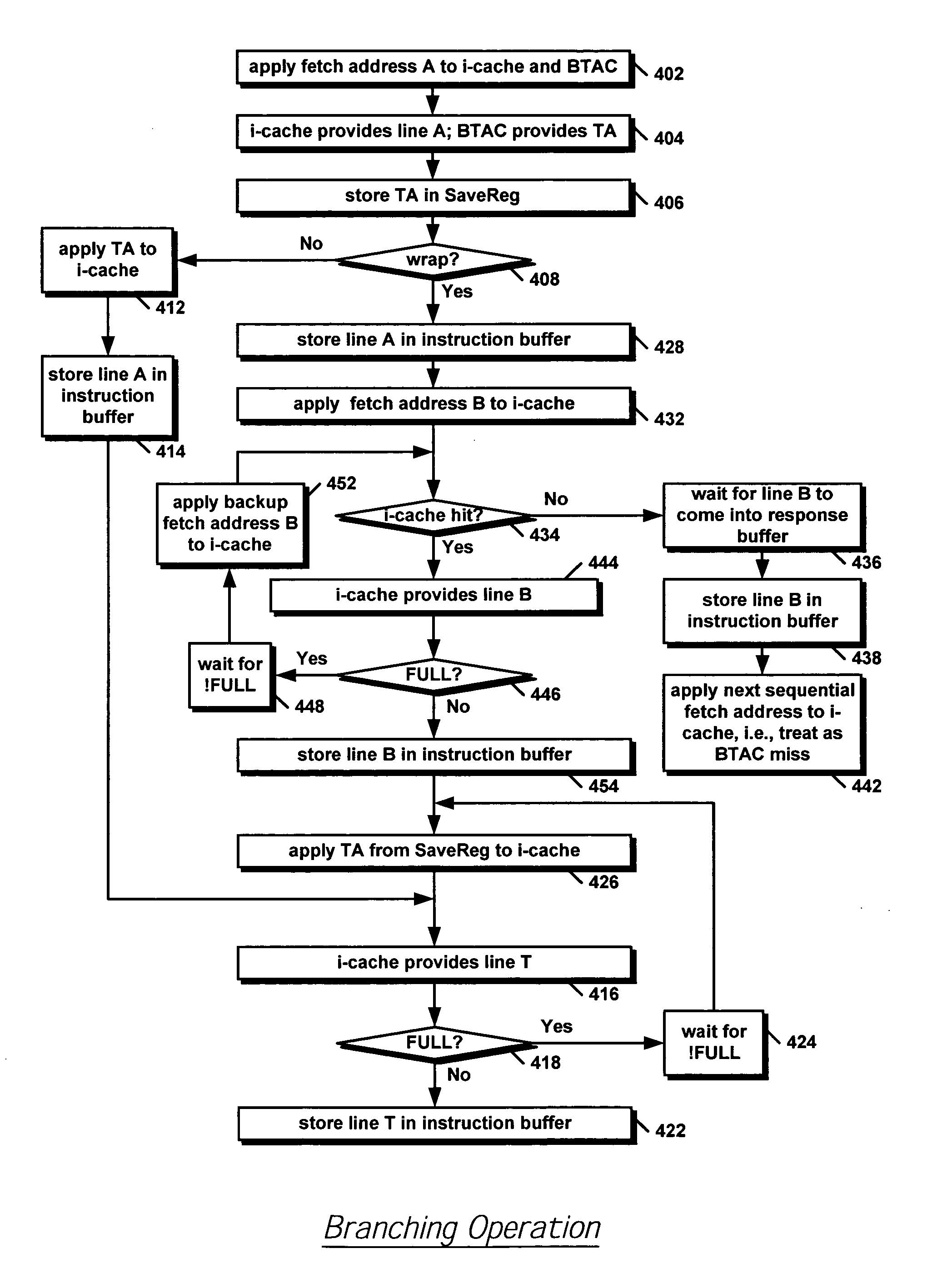

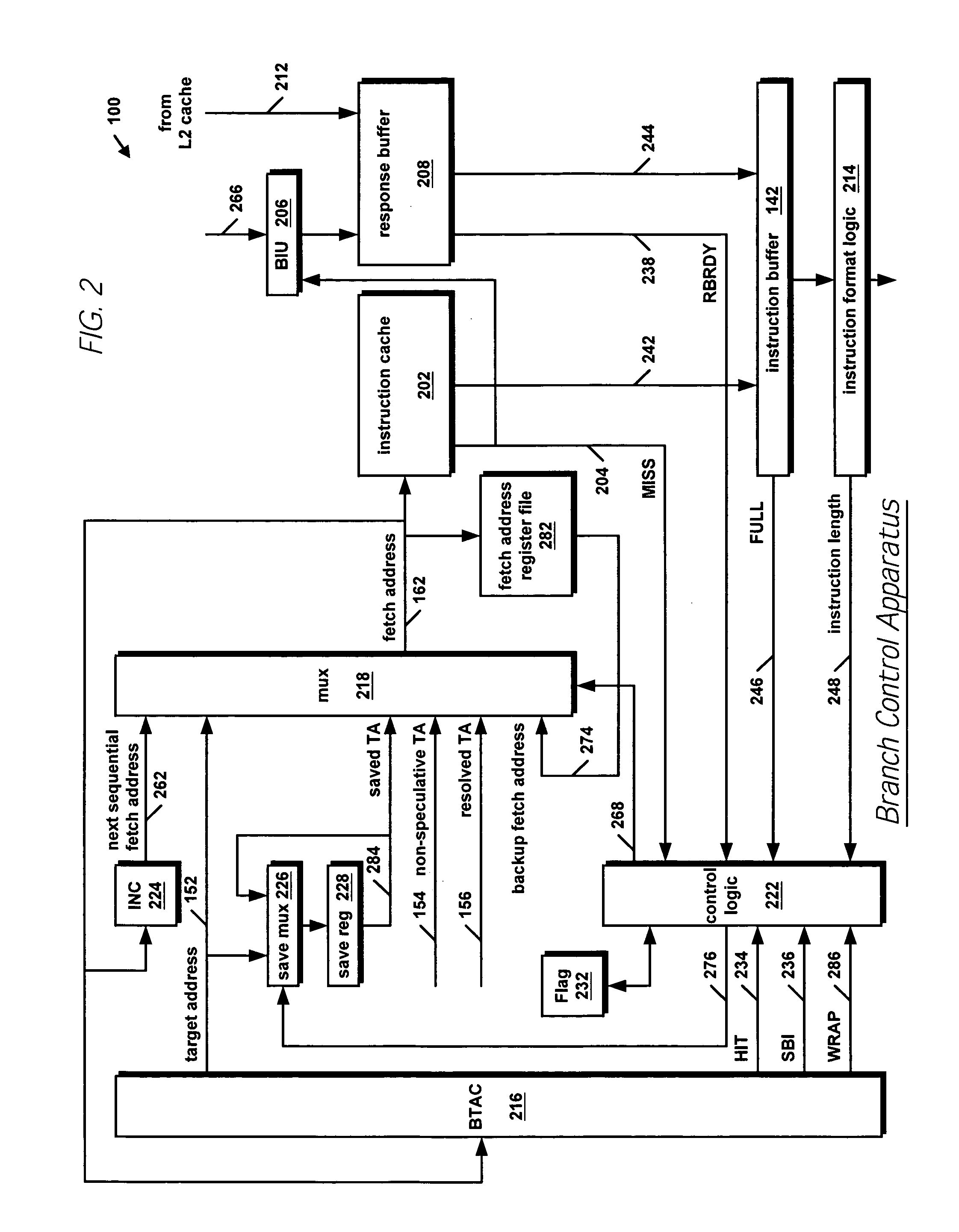

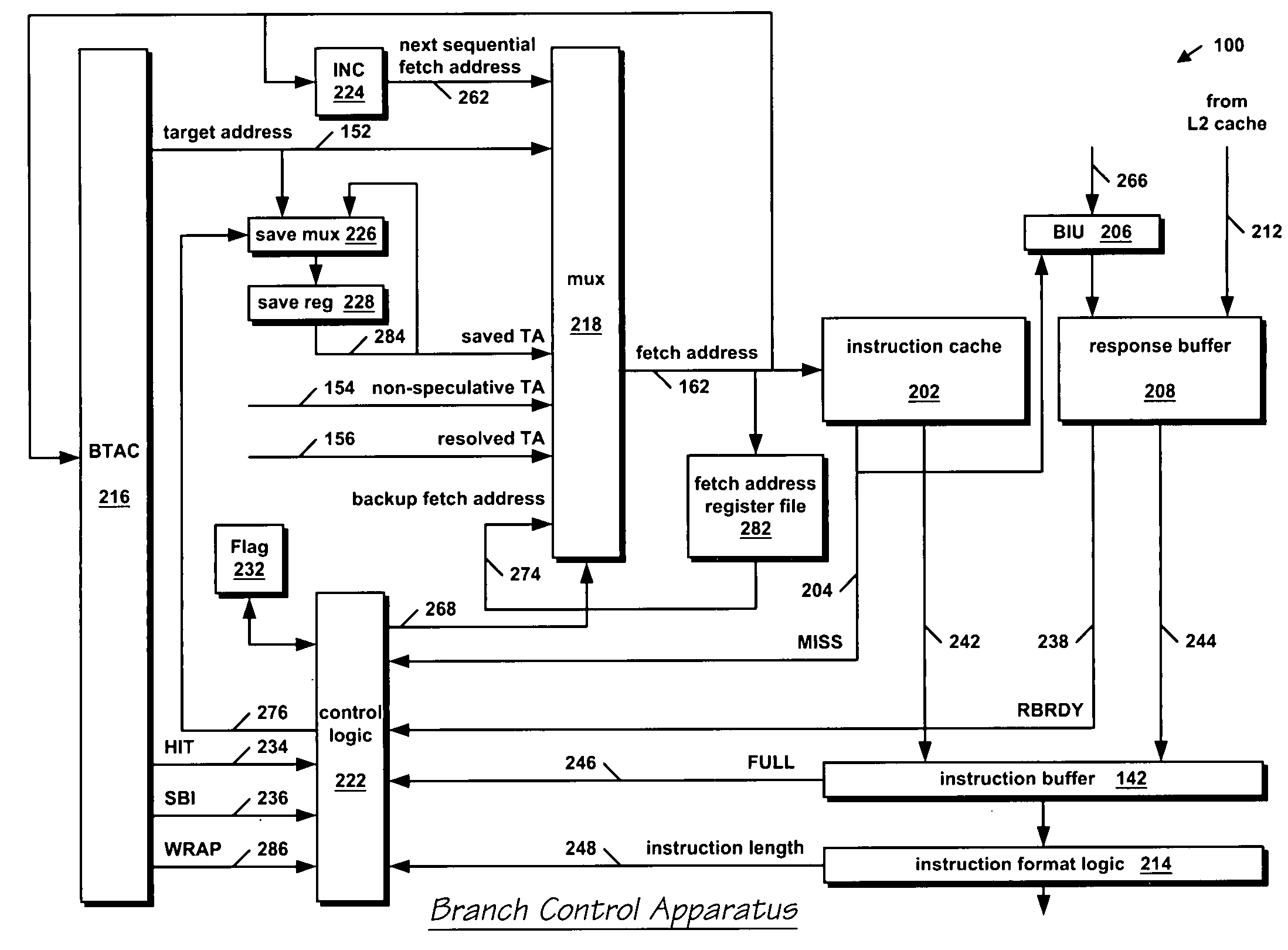

Apparatus and method for handling BTAC branches that wrap across instruction cache lines

InactiveUS20050198479A1Improves branch performanceAvoiding branch penaltyInstruction analysisRuntime instruction translationProcessor registerBranch target address cache

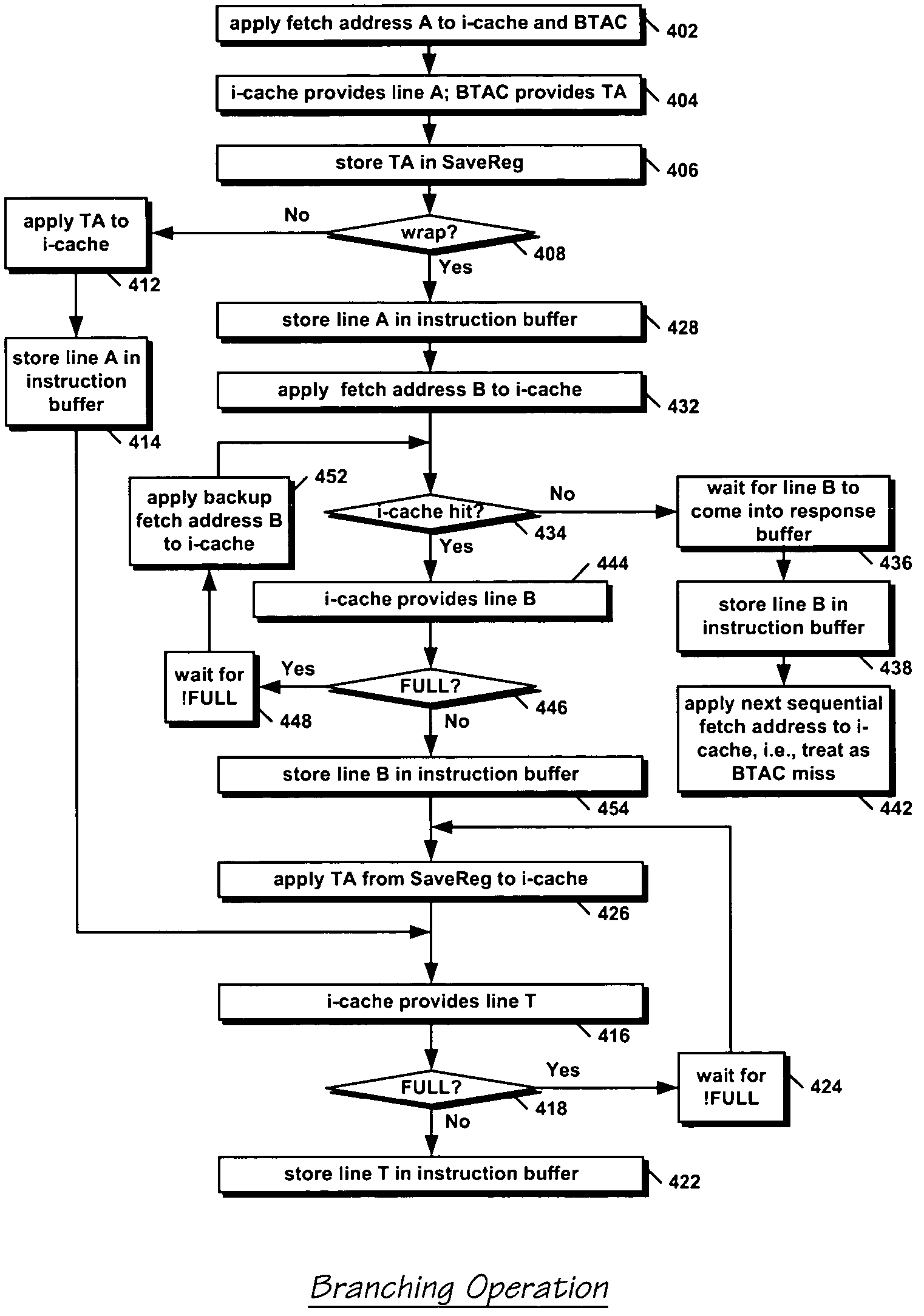

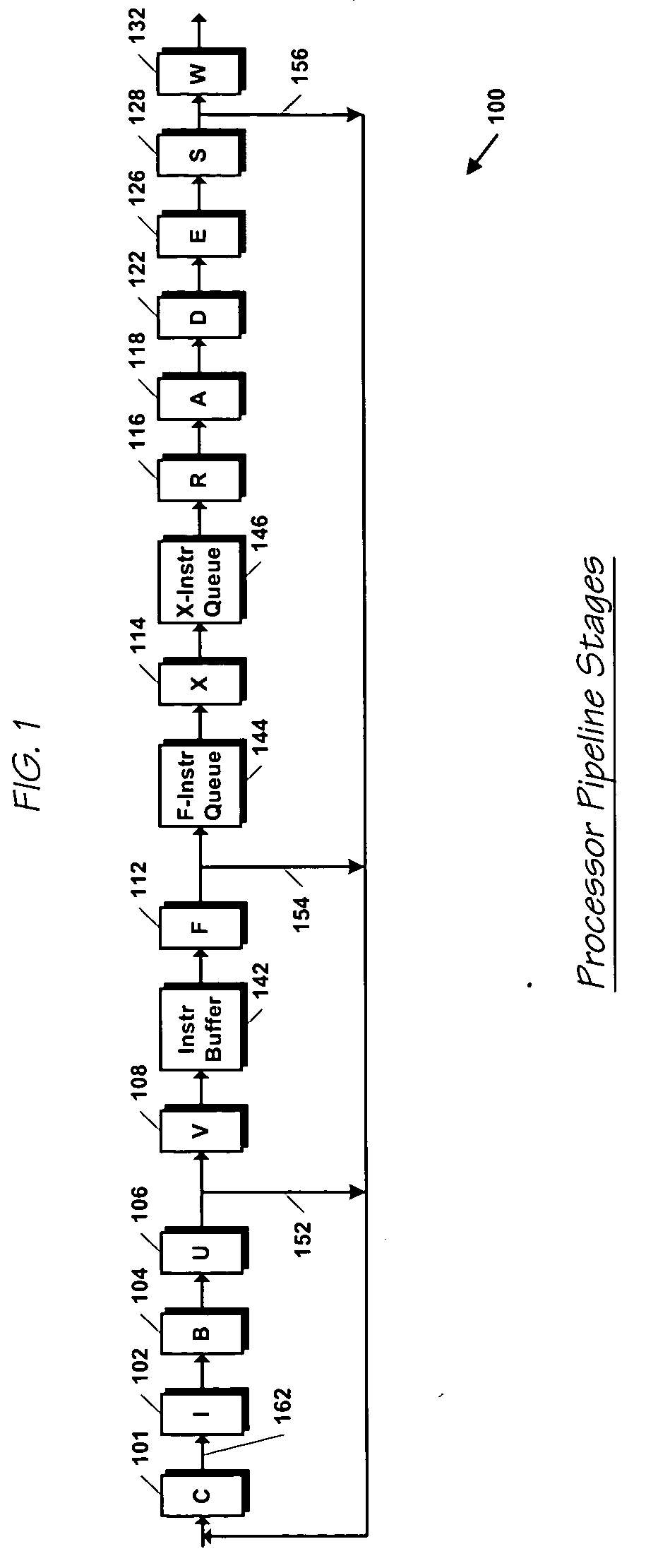

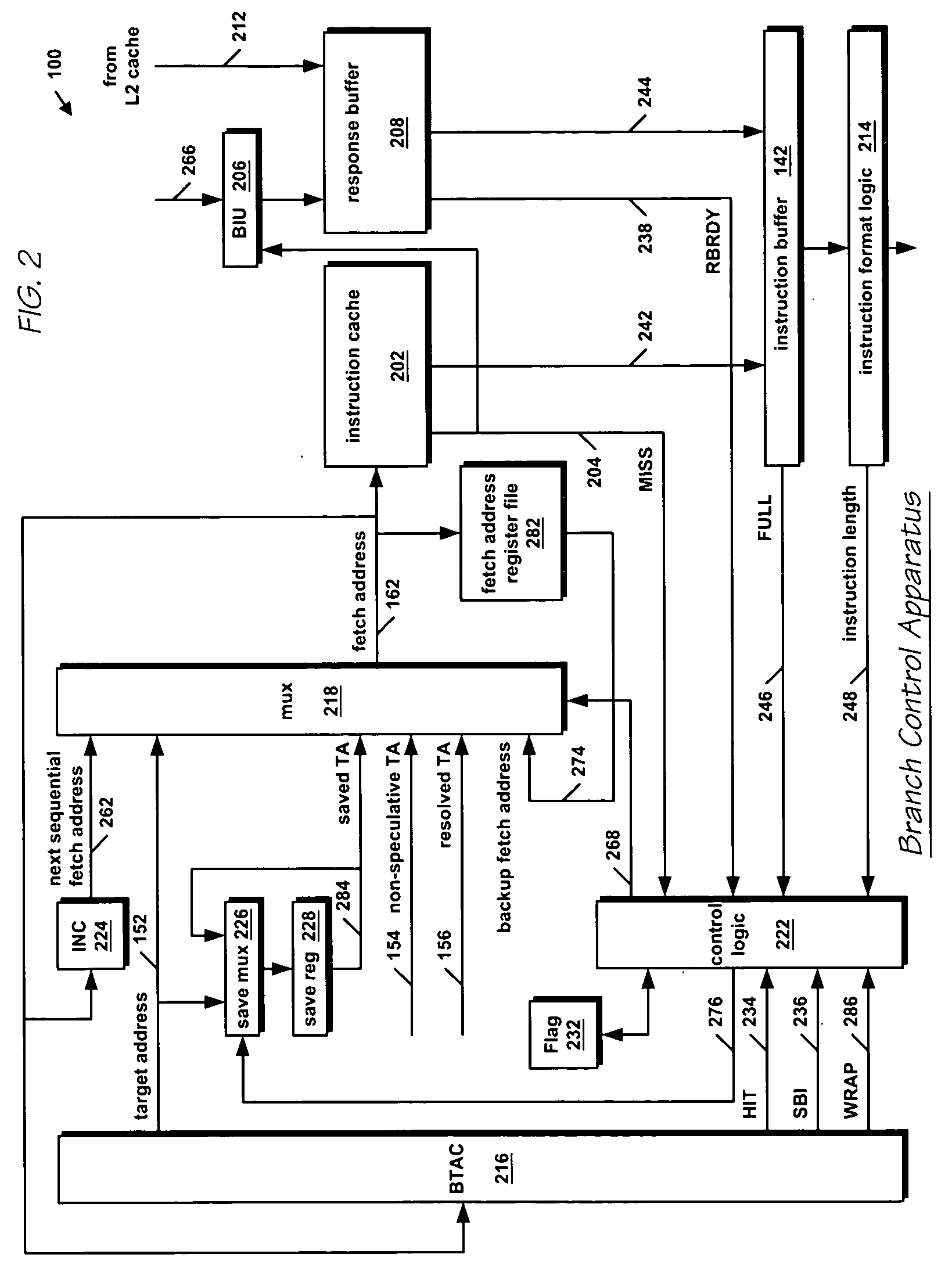

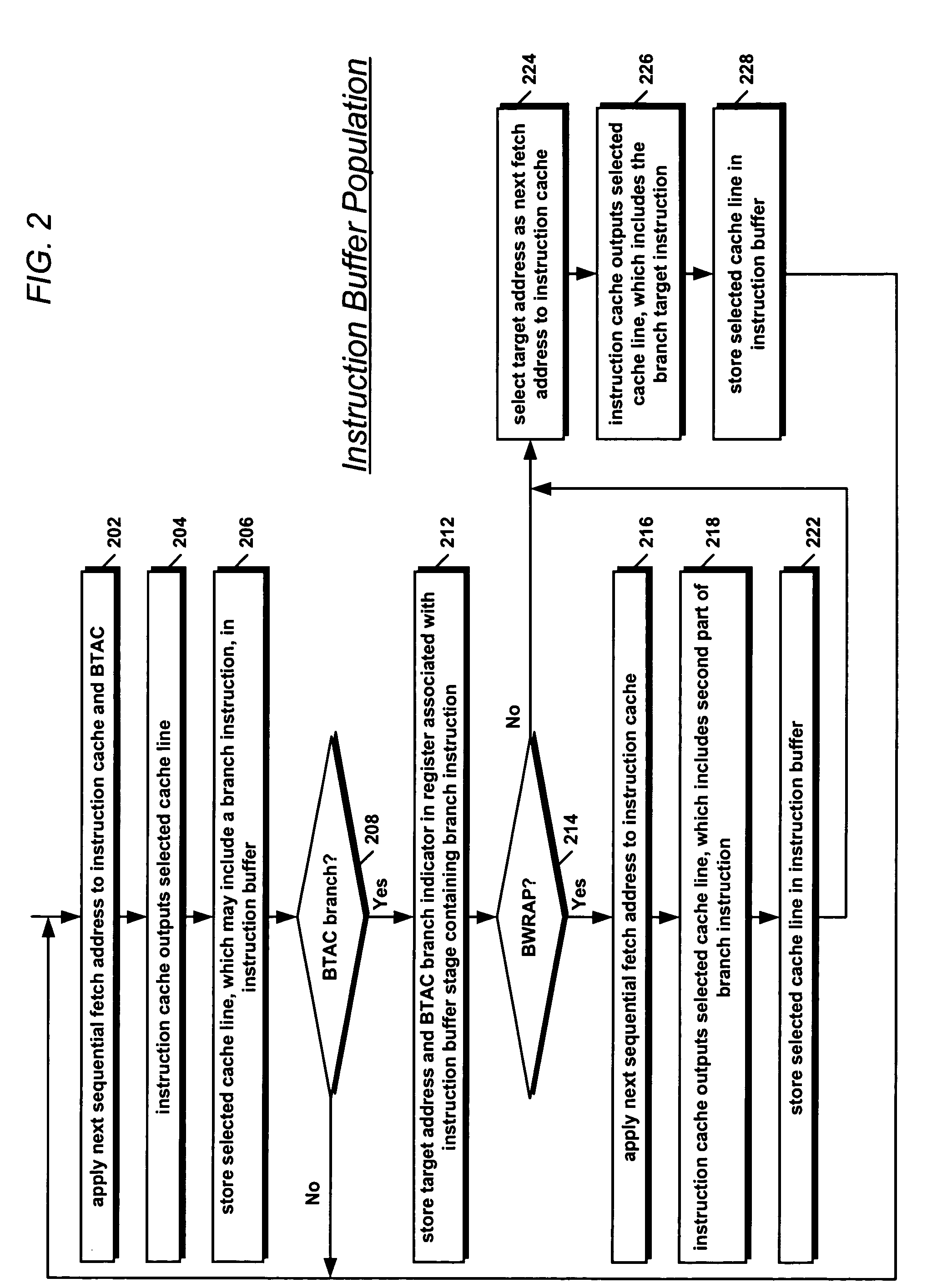

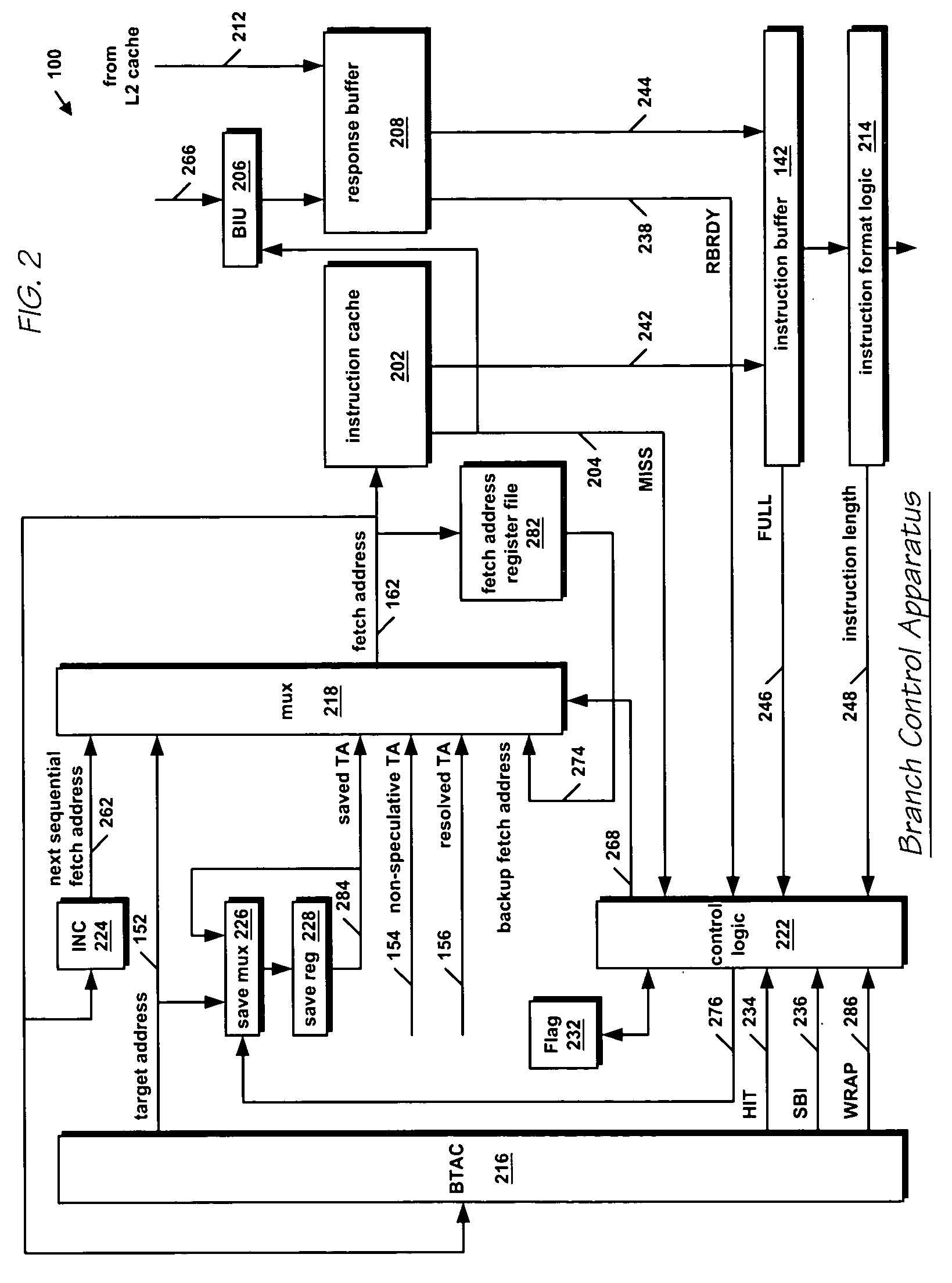

A branch control apparatus in a microprocessor. The apparatus includes a branch target address cache (BTAC) that caches indications of whether a branch instruction wraps across two cache lines. When an instruction cache fetch address of a first cache line containing the first part of the branch instruction hits in the BTAC, the BTAC outputs a target address of the branch instruction and indicates the wrap condition. The target address is stored in a register. The next sequential fetch address selects a second cache line containing the second part of the branch instruction. After the two cache lines containing the branch instruction are fetched, the target address from the register is provided to the instruction cache in order to fetch a third cache line containing a target instruction of the branch. The three cache lines are stored in order in an instruction buffer for decoding.

Owner:IP FIRST

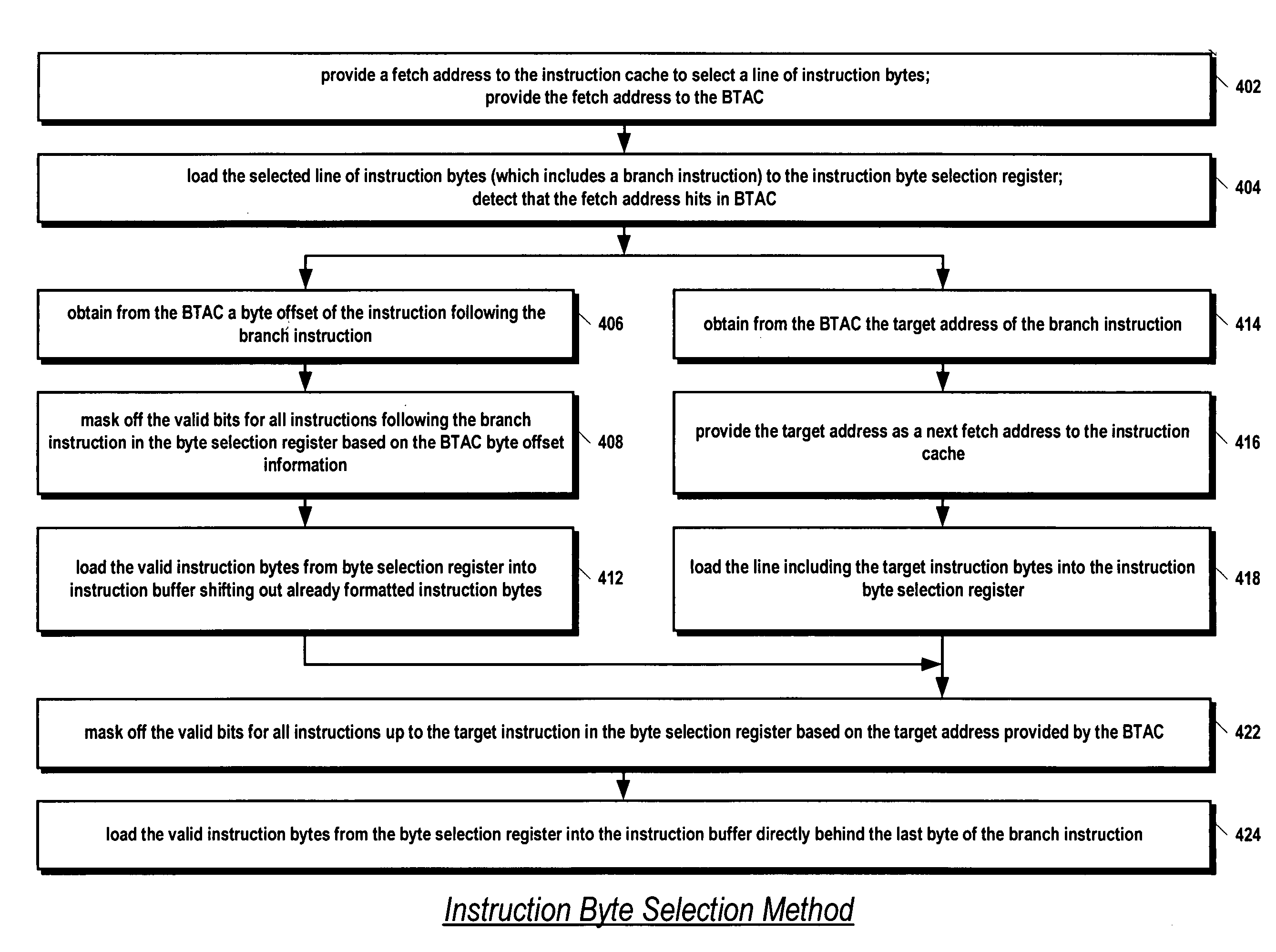

Apparatus and method for densely packing a branch instruction predicted by a branch target address cache and associated target instructions into a byte-wide instruction buffer

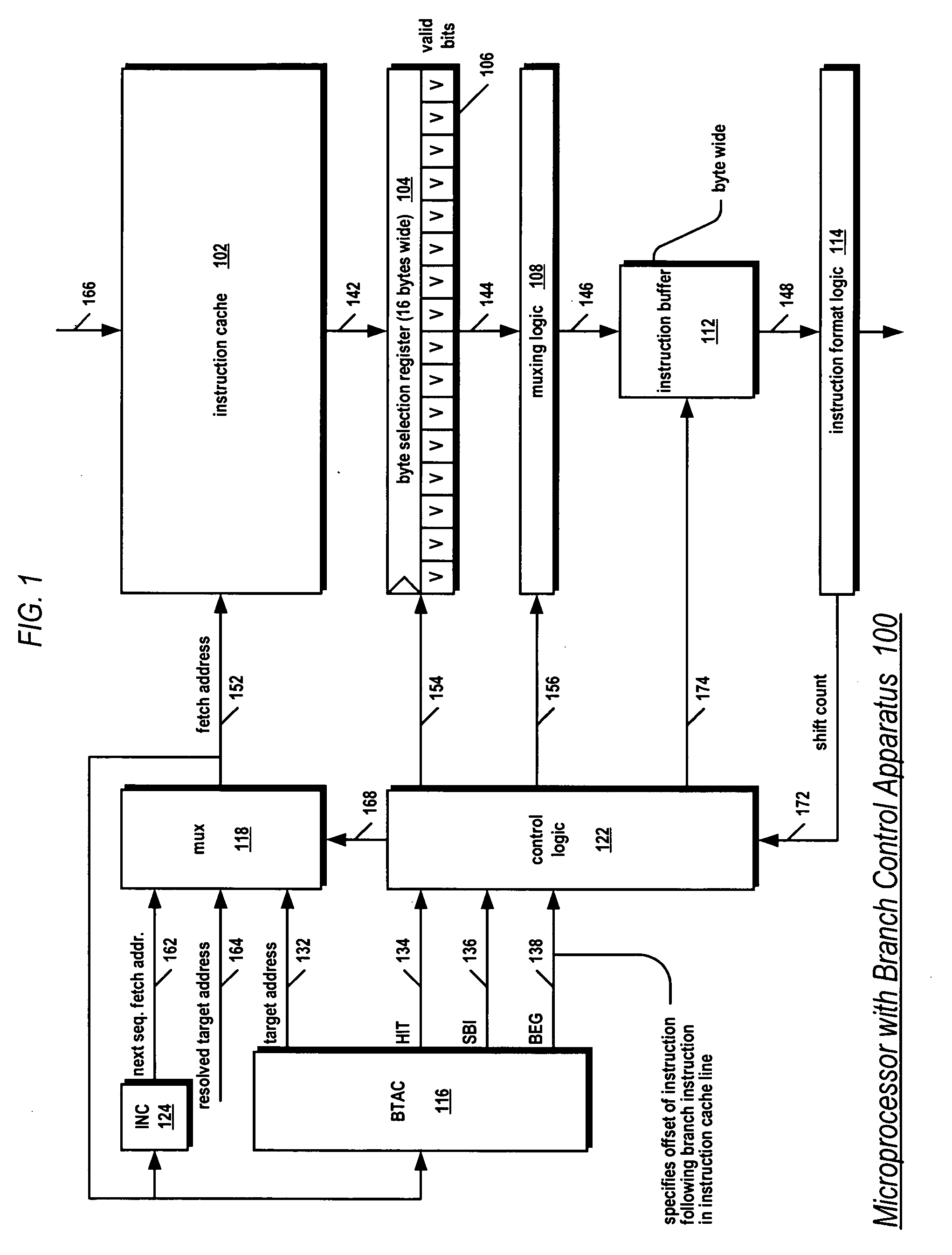

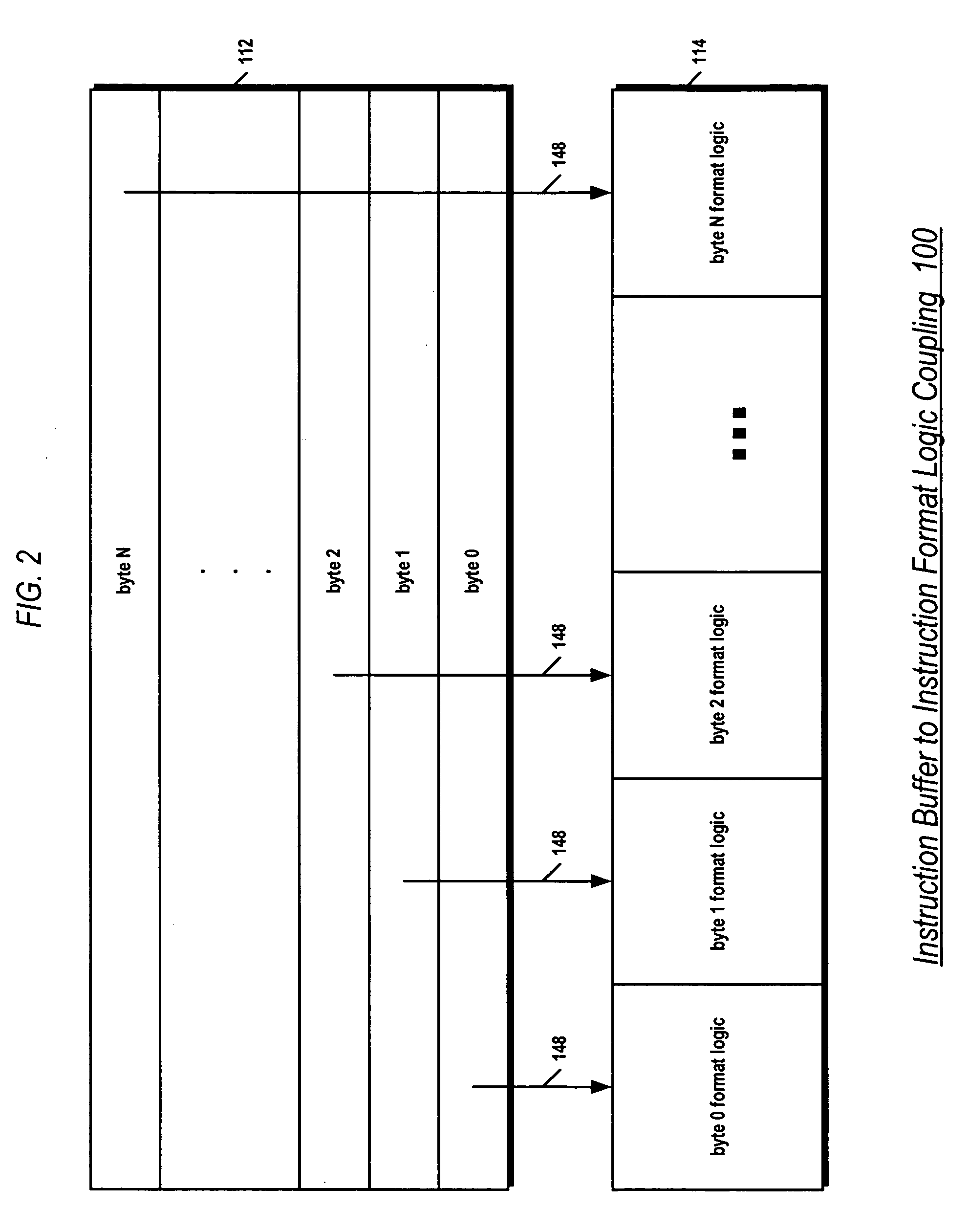

InactiveUS20050198481A1Alleviate Timing ConstraintsMemory adressing/allocation/relocationDigital computer detailsParallel computingBranch target address cache

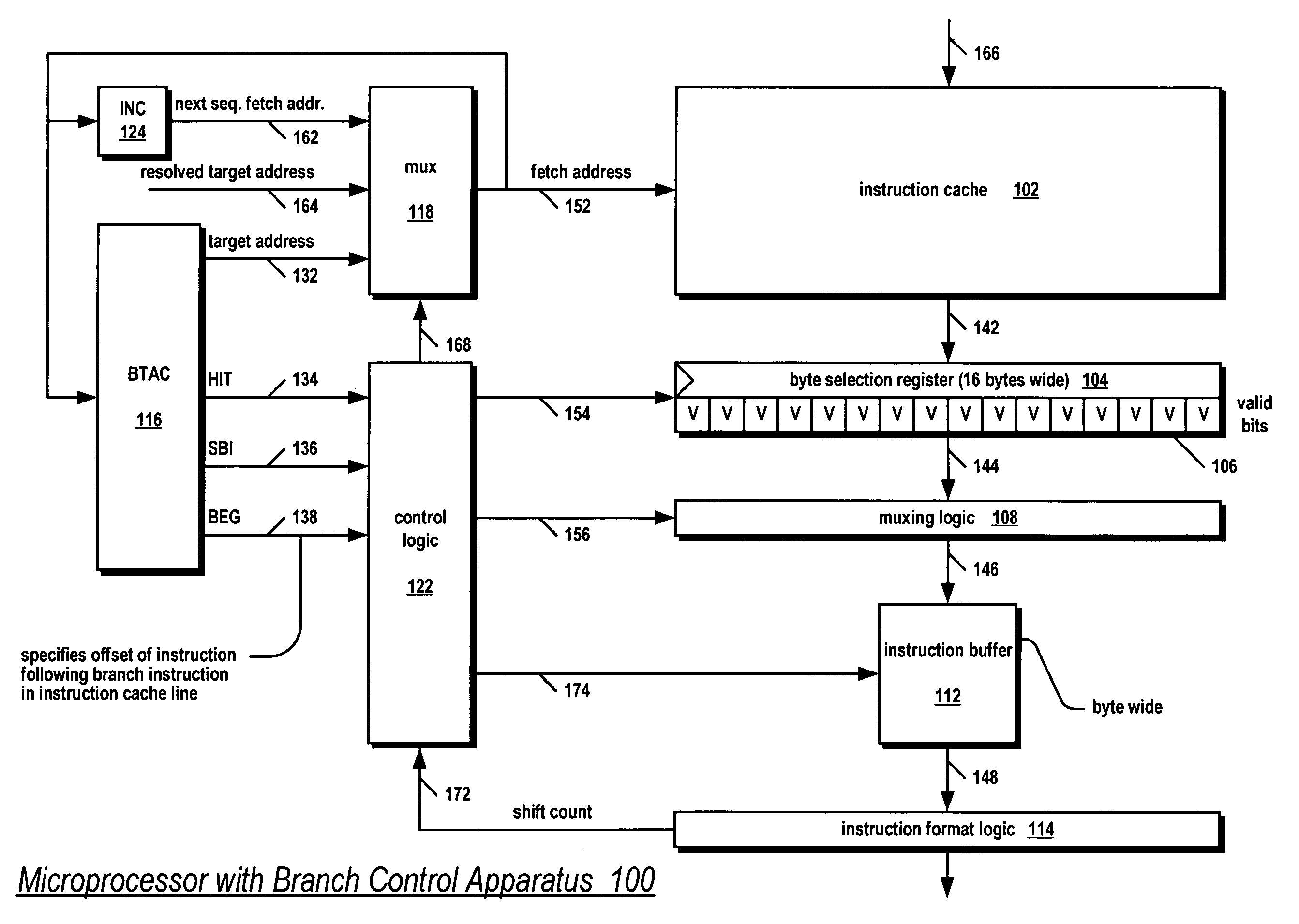

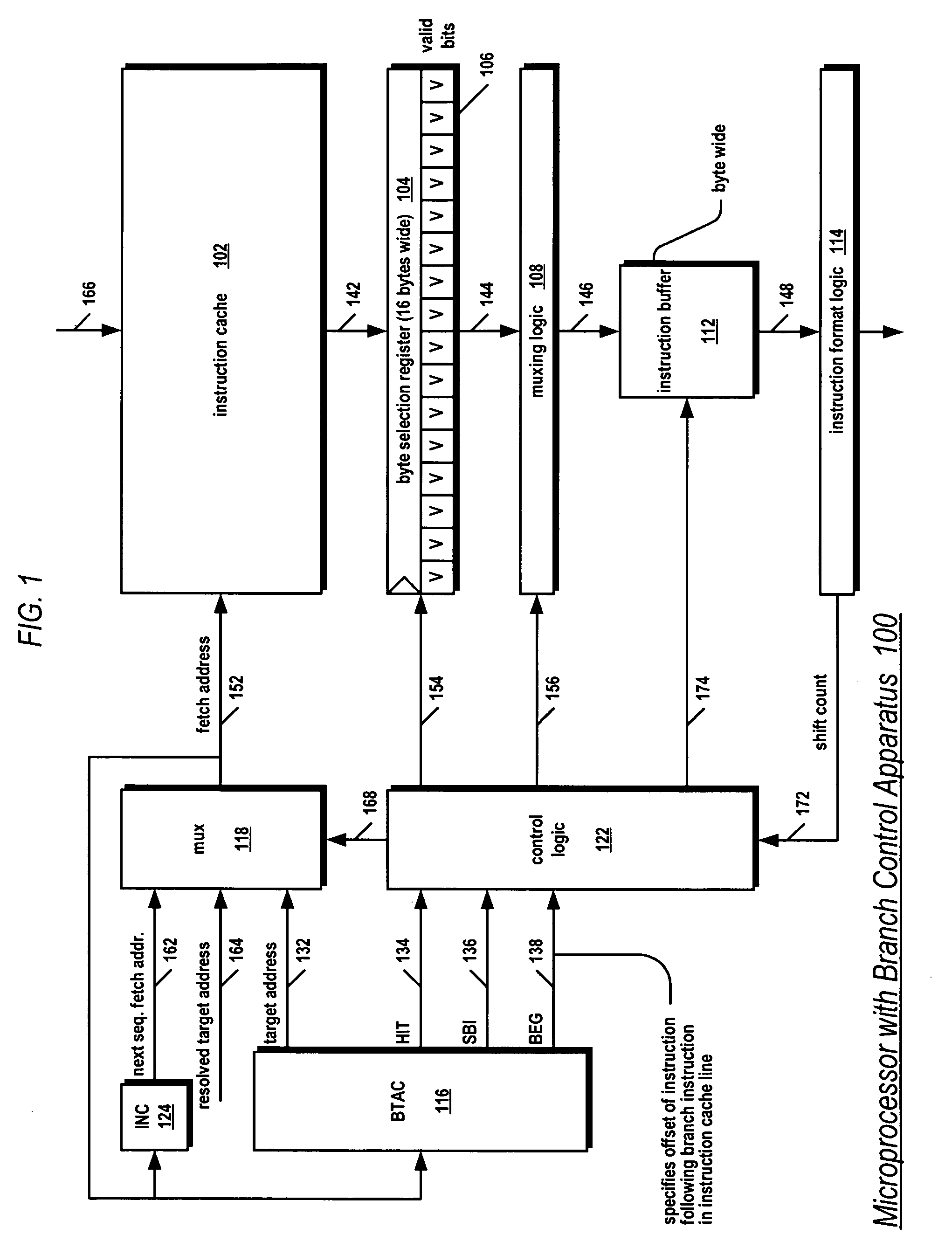

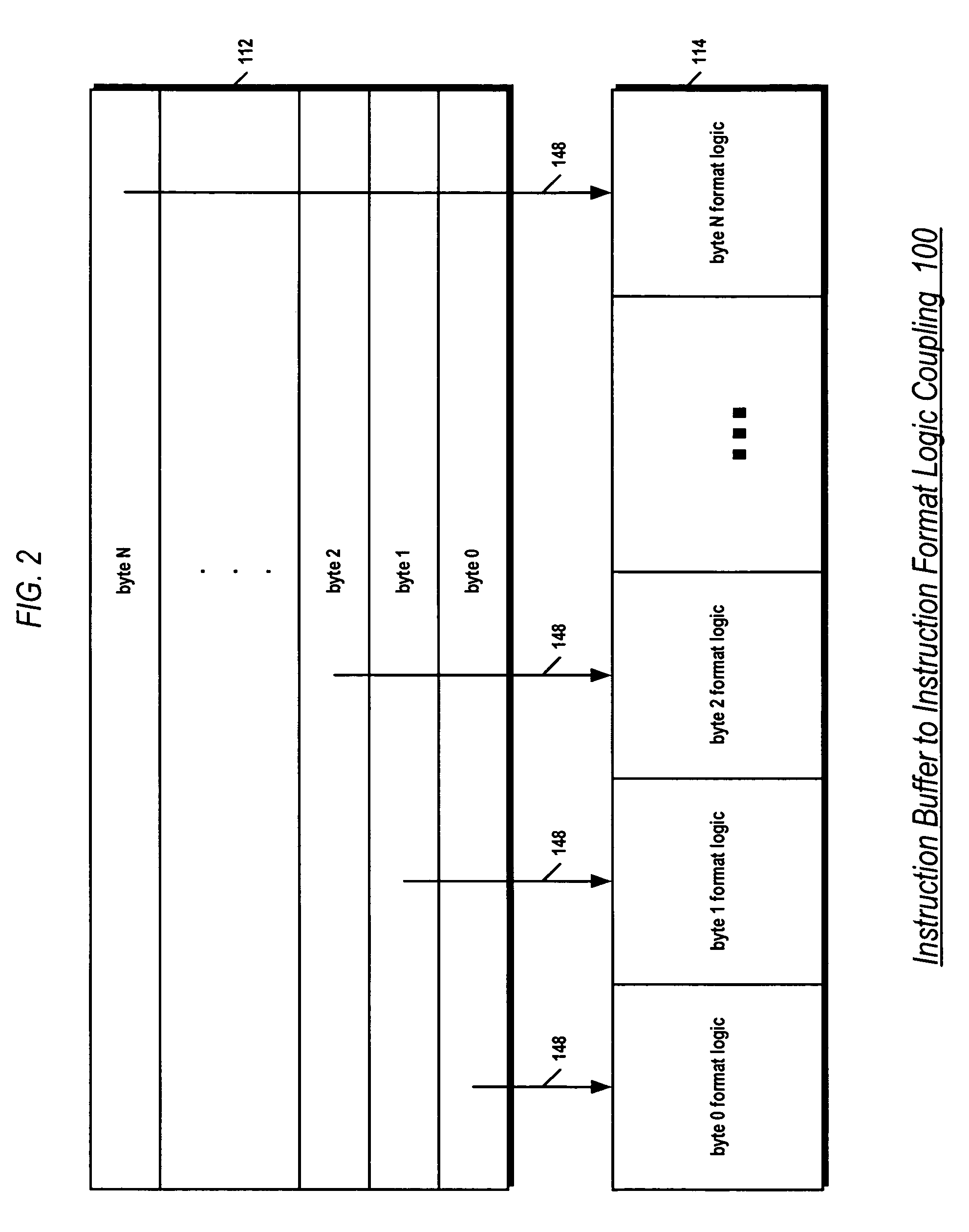

A branch control apparatus in a microprocessor. A register receives a first cache line containing a branch instruction from an instruction cache in response to a fetch address. The fetch address hits in a BTAC that provides a target address of the branch instruction. The BTAC also provides an offset of the instruction following the branch instruction. The instructions following the branch instruction are invalidated based on the offset. Muxing logic packs only the valid instructions into a byte-wide instruction buffer that is directly coupled to instruction format logic. The instruction cache provides a second cache line containing the target instructions to the register in response to the target address. The instructions preceding the target instructions are invalidated based on the lower bits of the target address. The muxing logic packs only the valid target instructions into the instruction buffer immediately adjacent to the branch instruction bytes.

Owner:IP FIRST

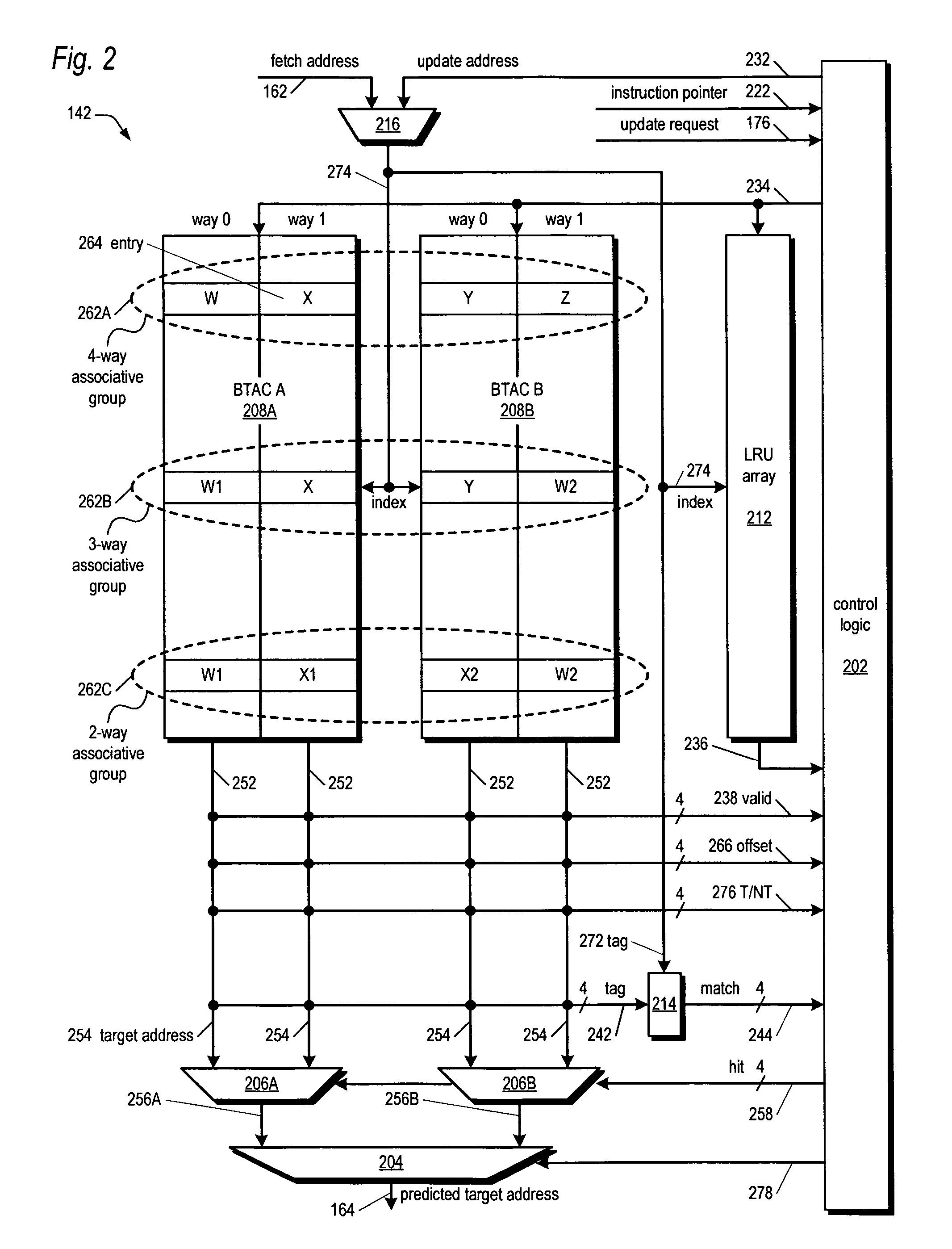

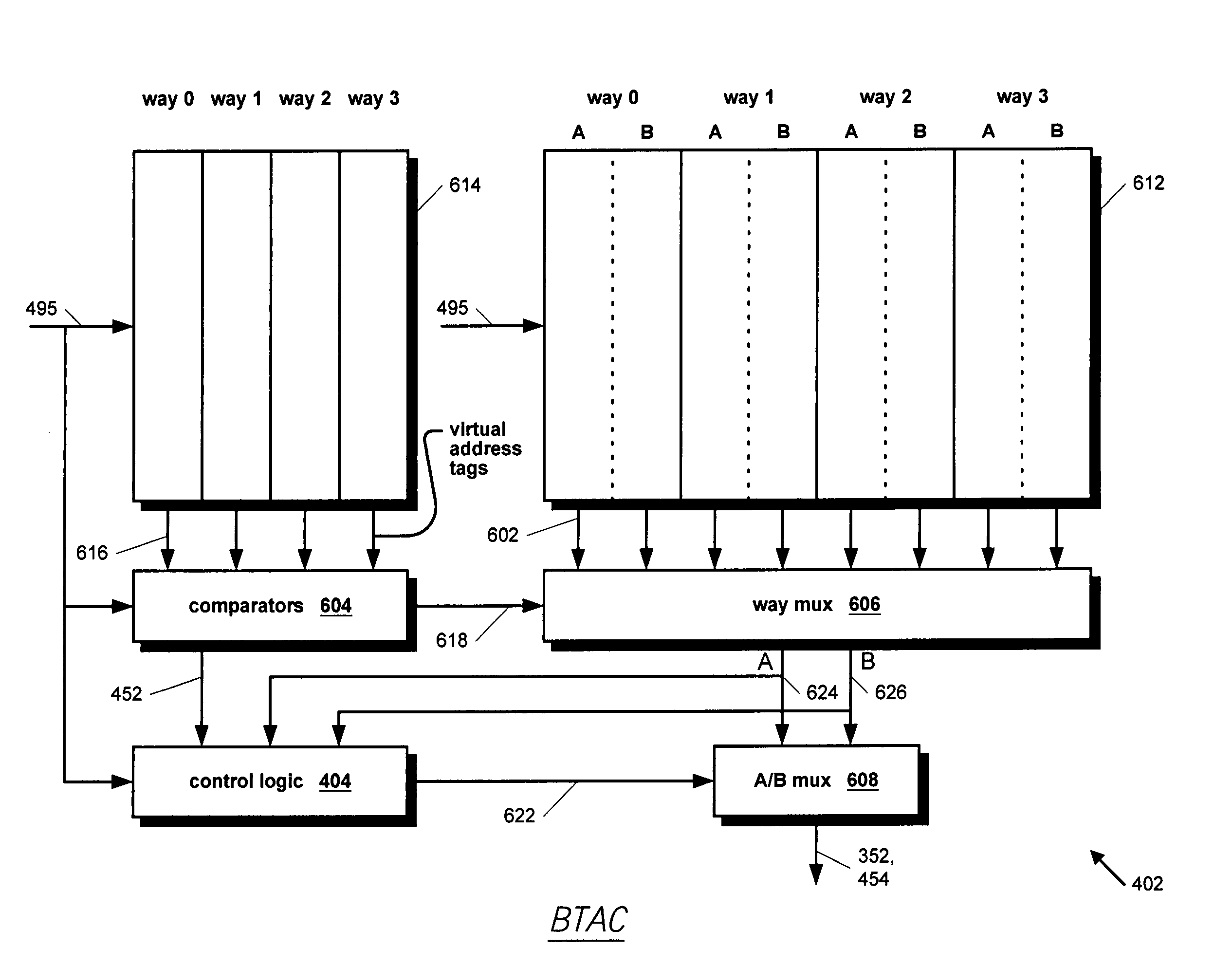

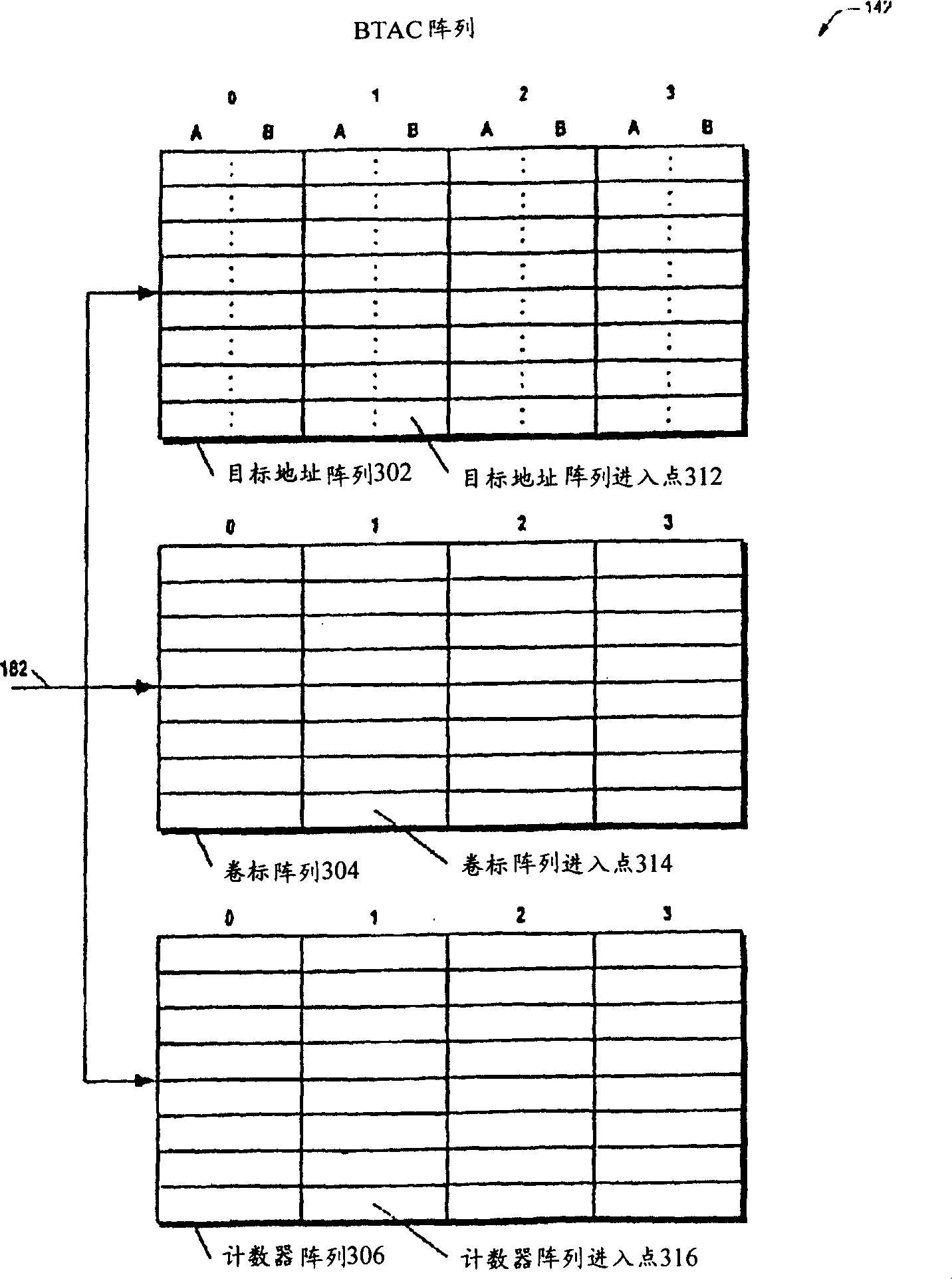

Variable group associativity branch target address cache delivering multiple target addresses per cache line

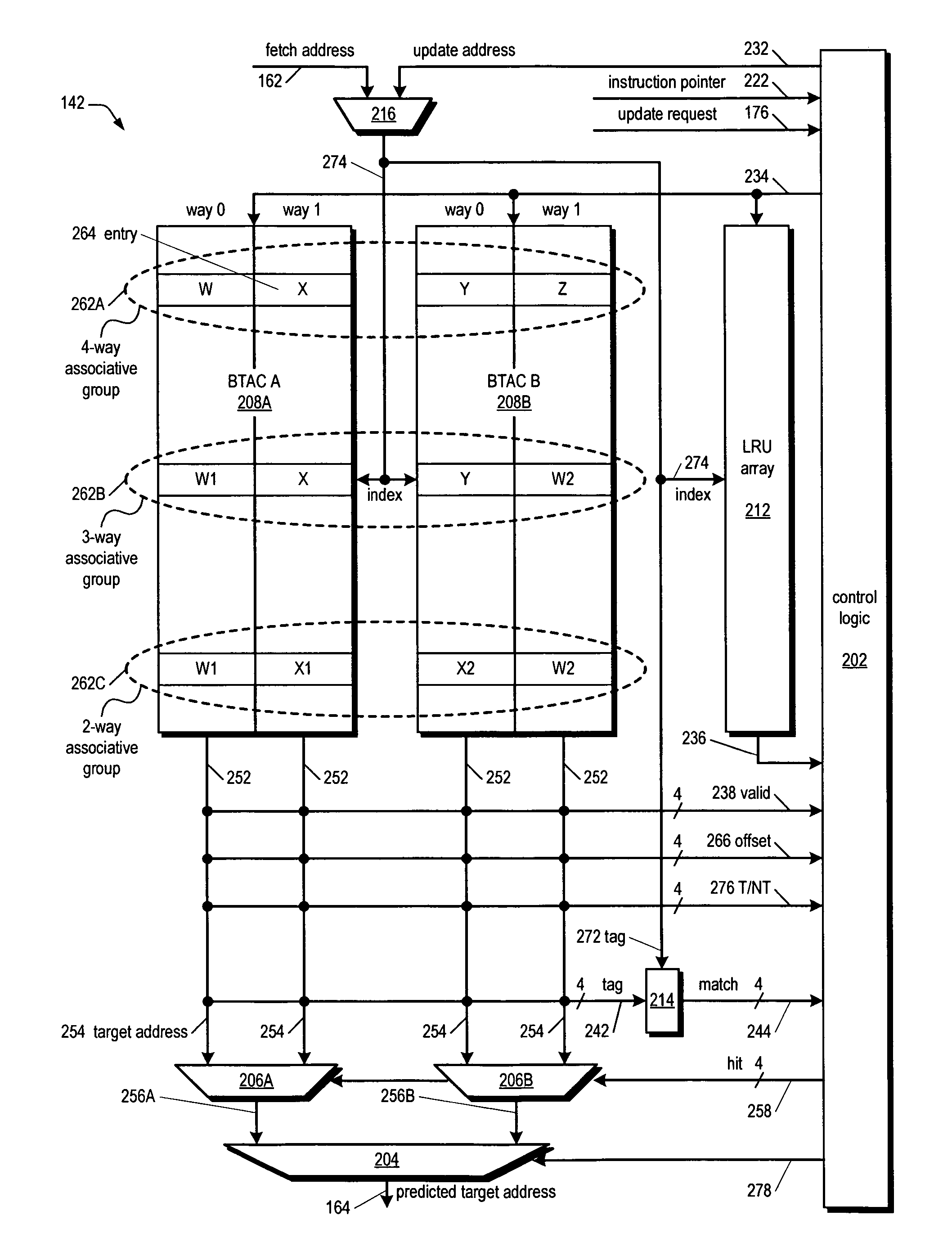

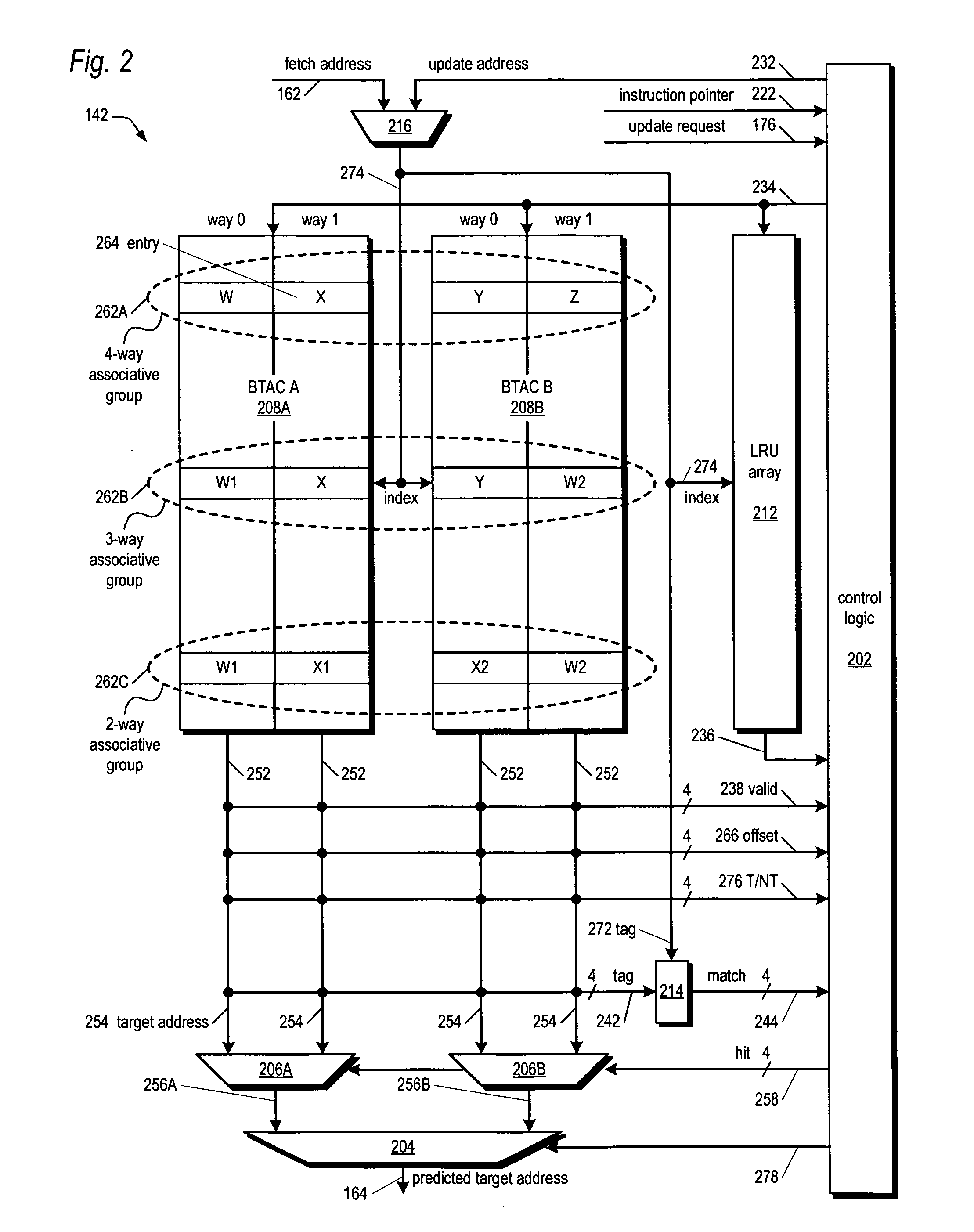

ActiveUS7707397B2Easy to useAchieving associativityComputation using non-contact making devicesDigital computer detailsBranch target address cacheParallel computing

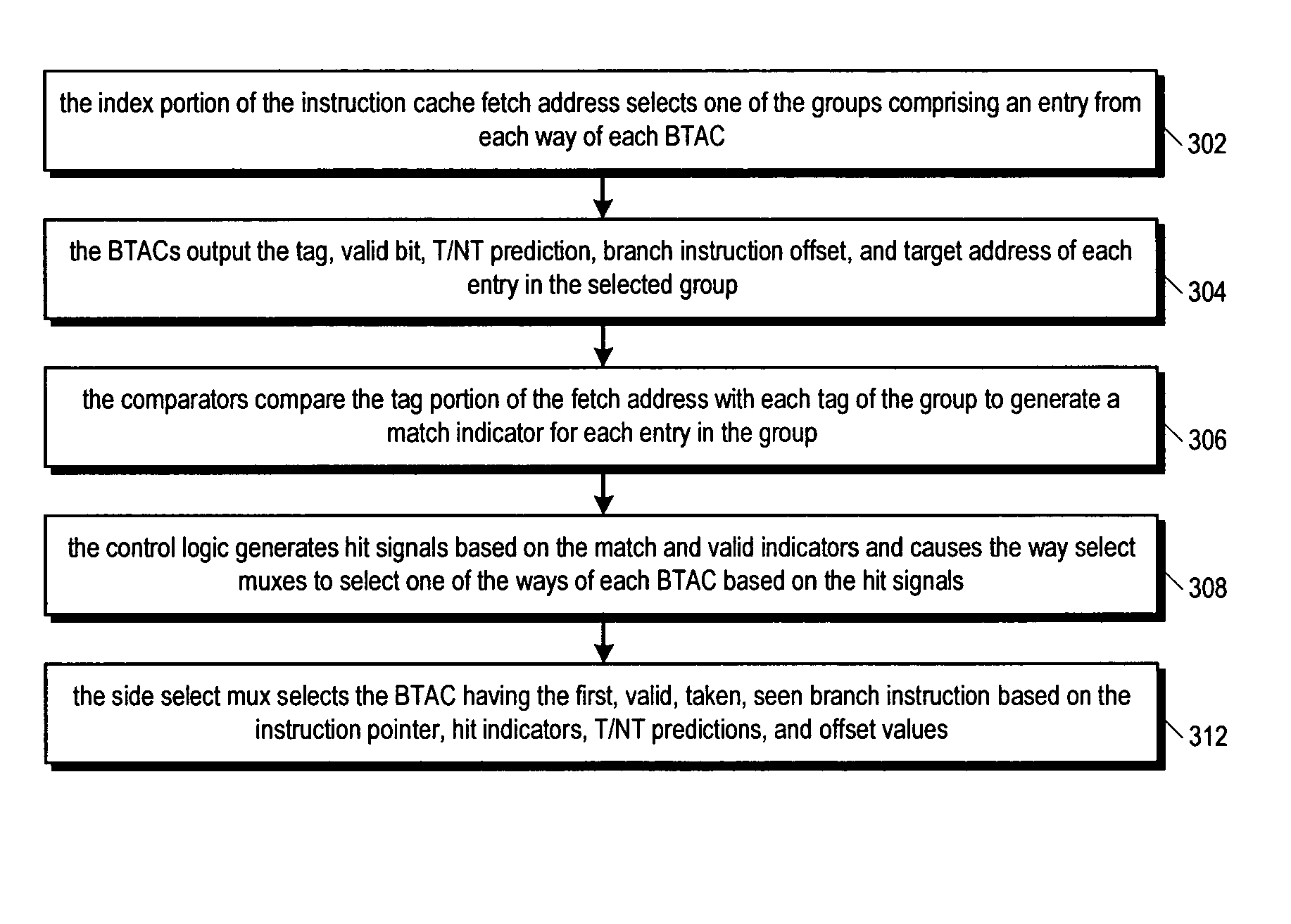

A branch prediction apparatus having two two-way set associative cache memories each indexed by a lower portion of an instruction cache fetch address is disclosed. The index selects a group of four entries, one from each way of each cache. Each entry stores a single target address of a different previously executed branch instruction. For some groups, the four entries cache target addresses for one branch instruction in each of four different cache lines, to obtain four-way group associativity; for other groups, the four entries cache target addresses for one branch instruction in each of two different cache lines and two branch instructions in a third different cache line, to effectively obtain three-way group associativity, depending on the distribution of the branch instructions in the program. The apparatus trades off associativity for number of predictable branches per cache line on an index-by-index basis to efficiently use storage space.

Owner:VIA TECH INC

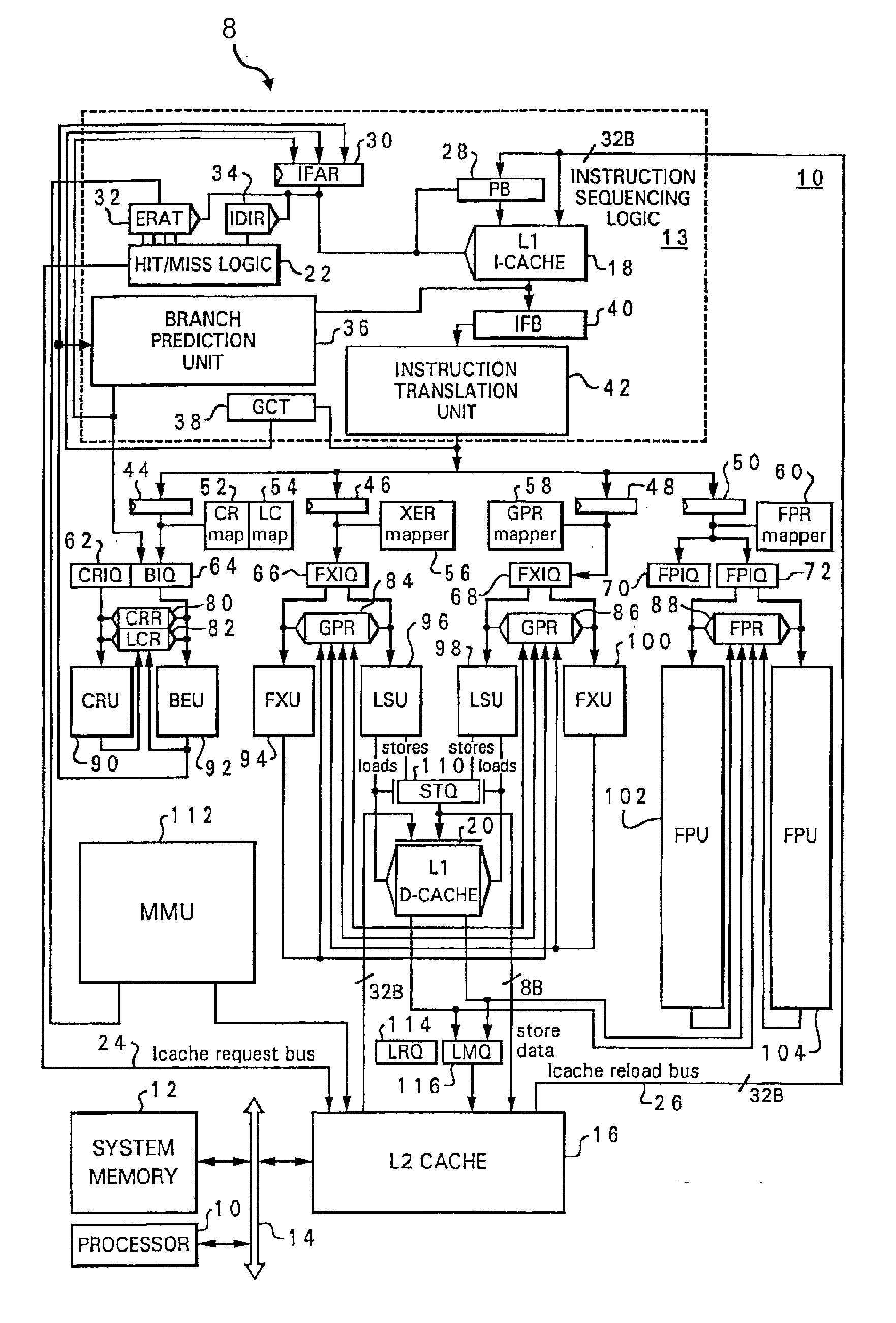

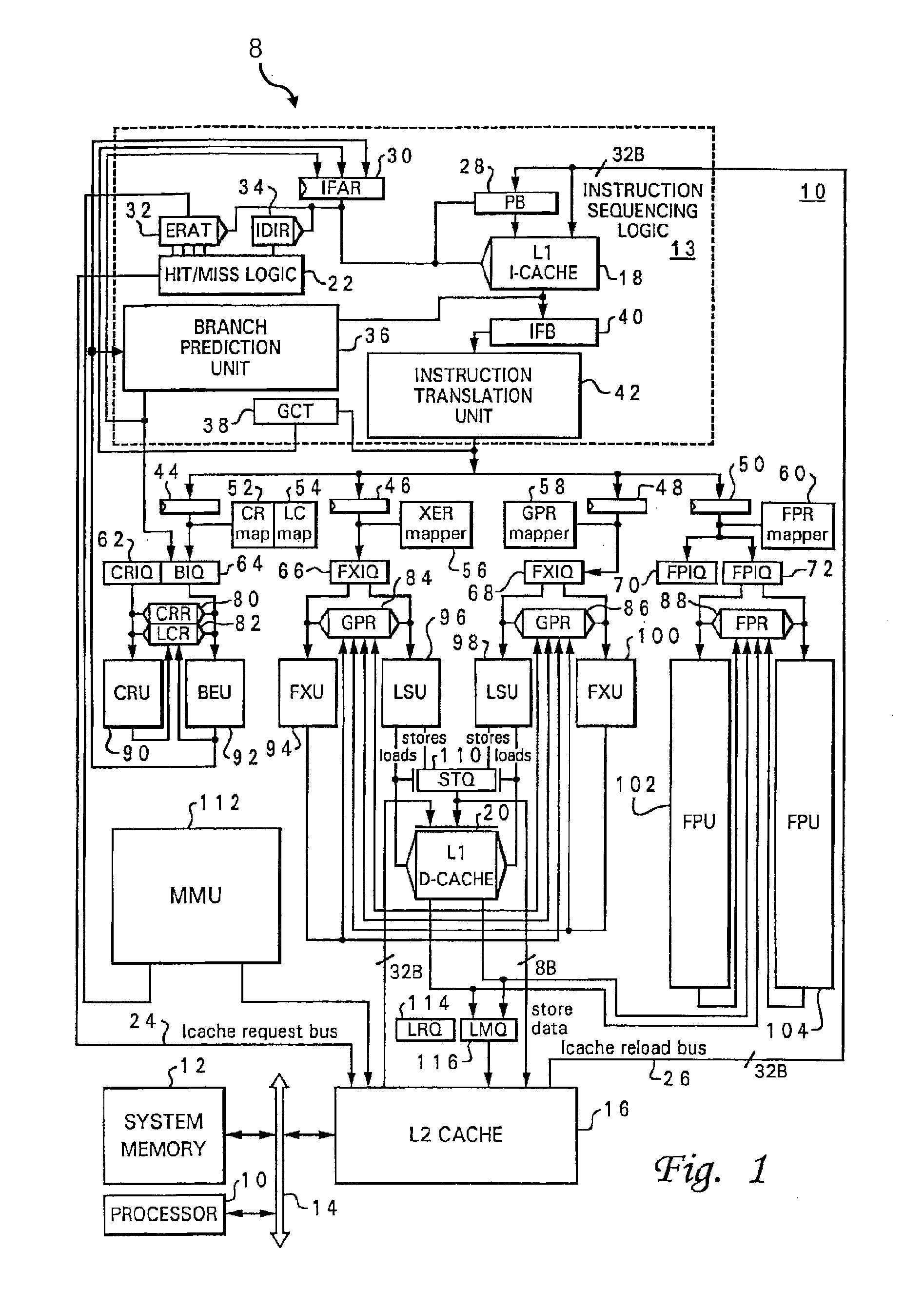

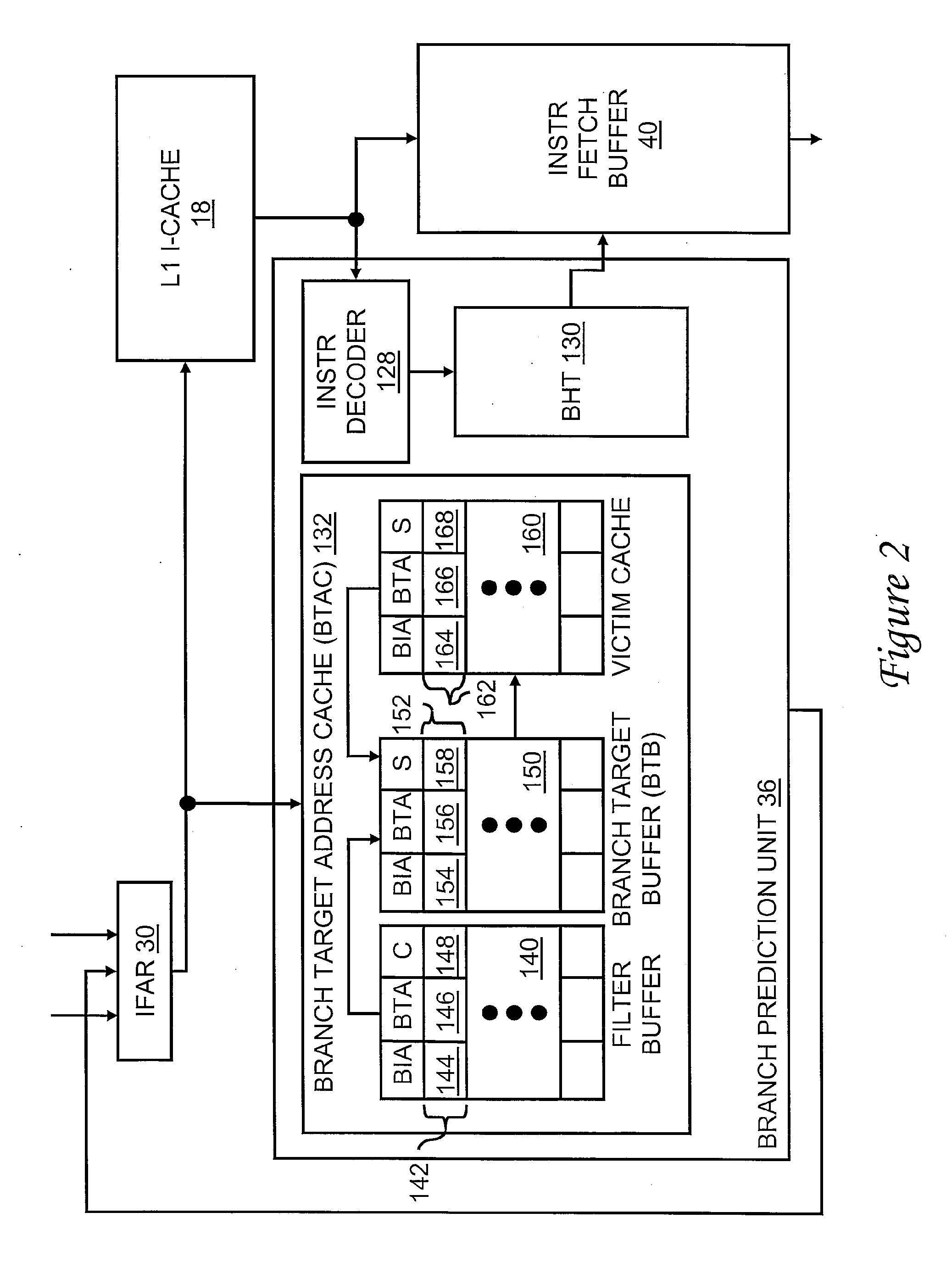

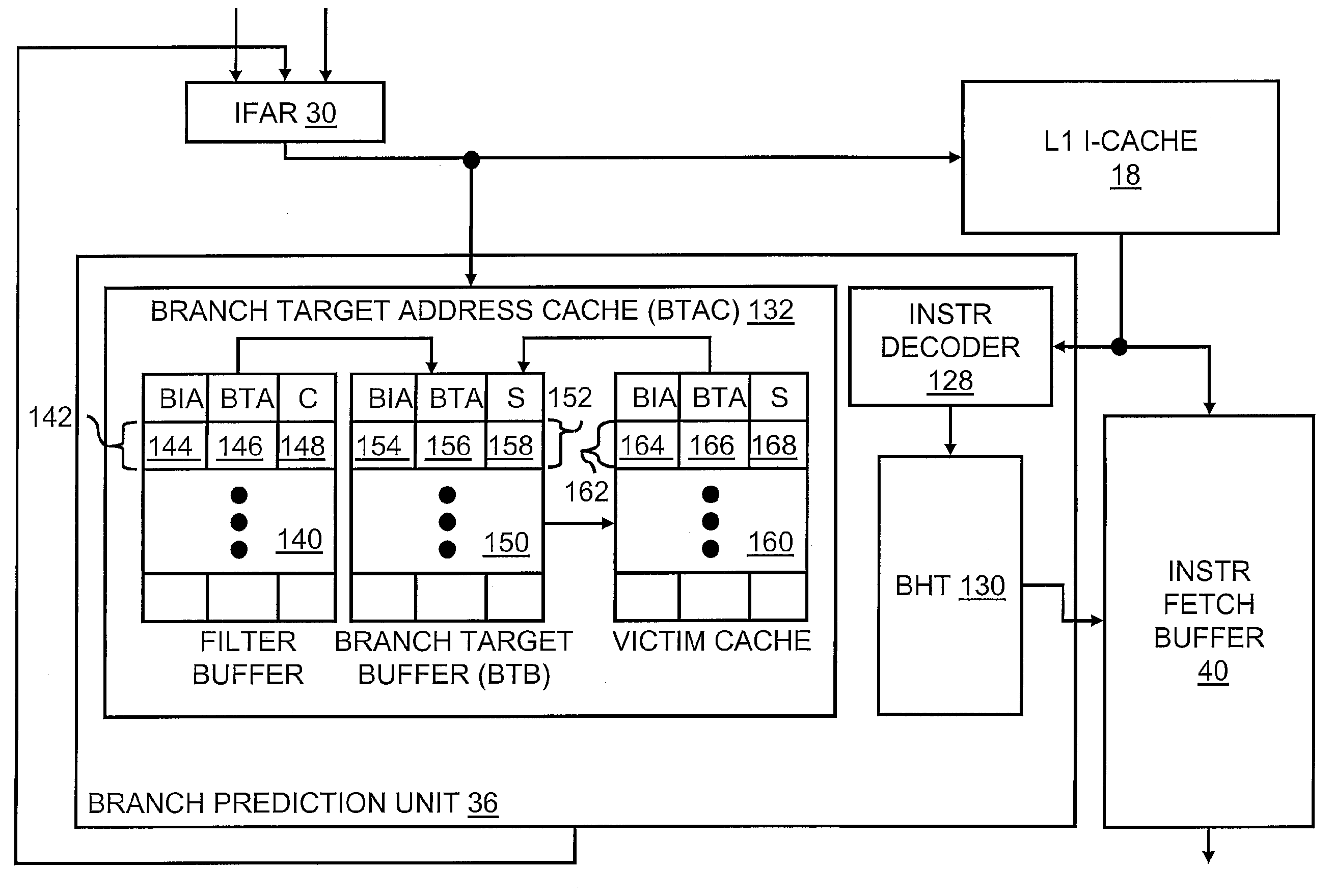

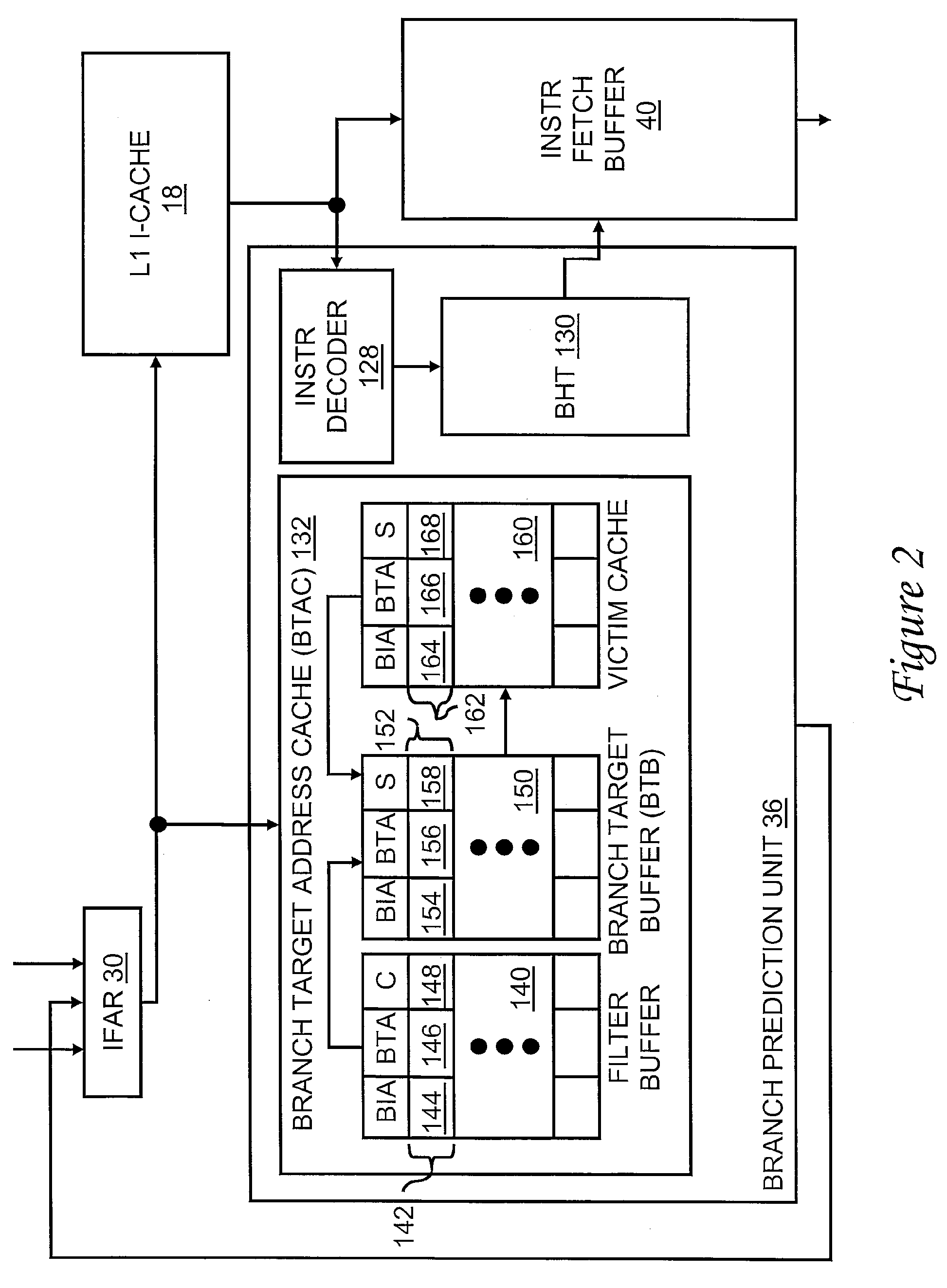

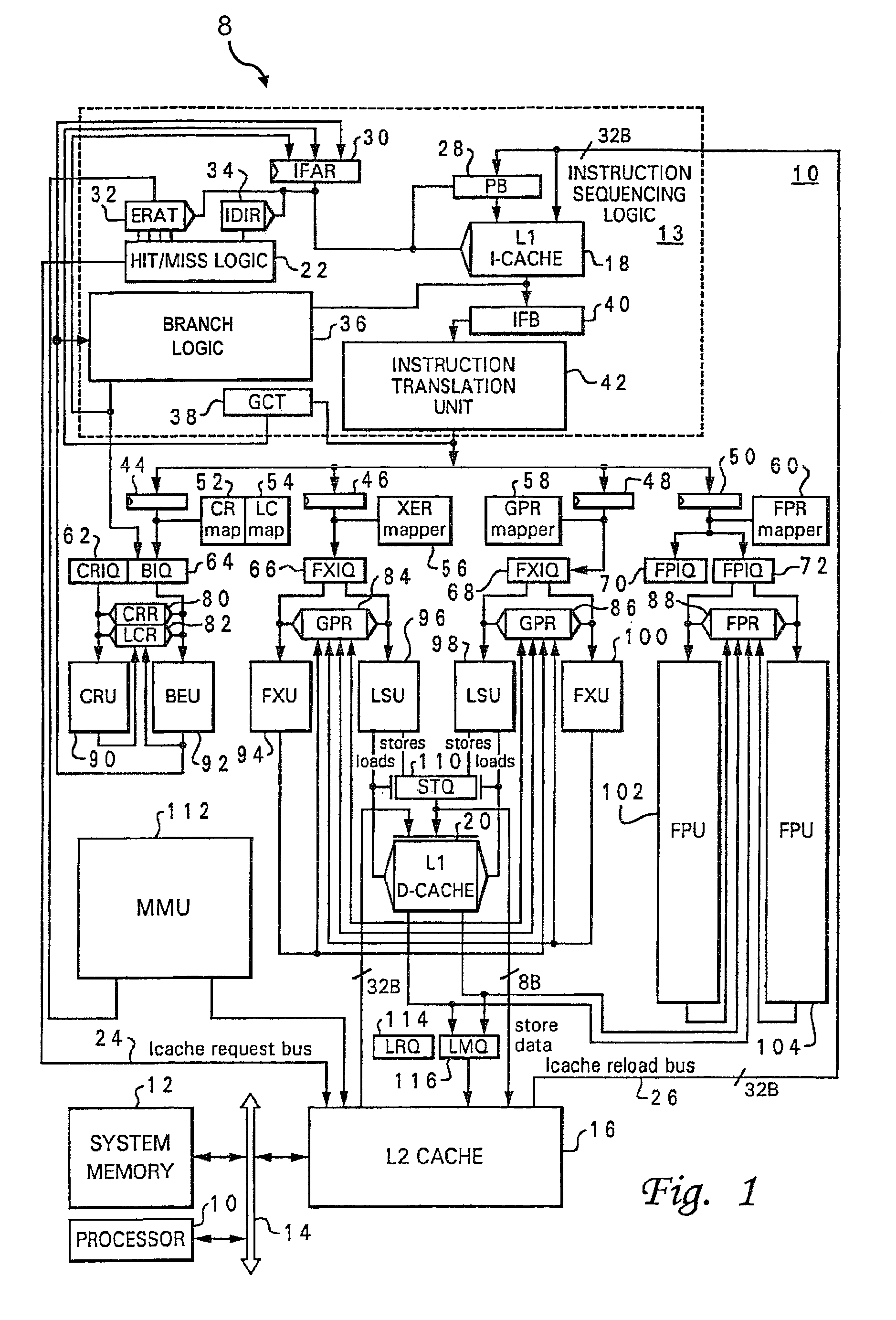

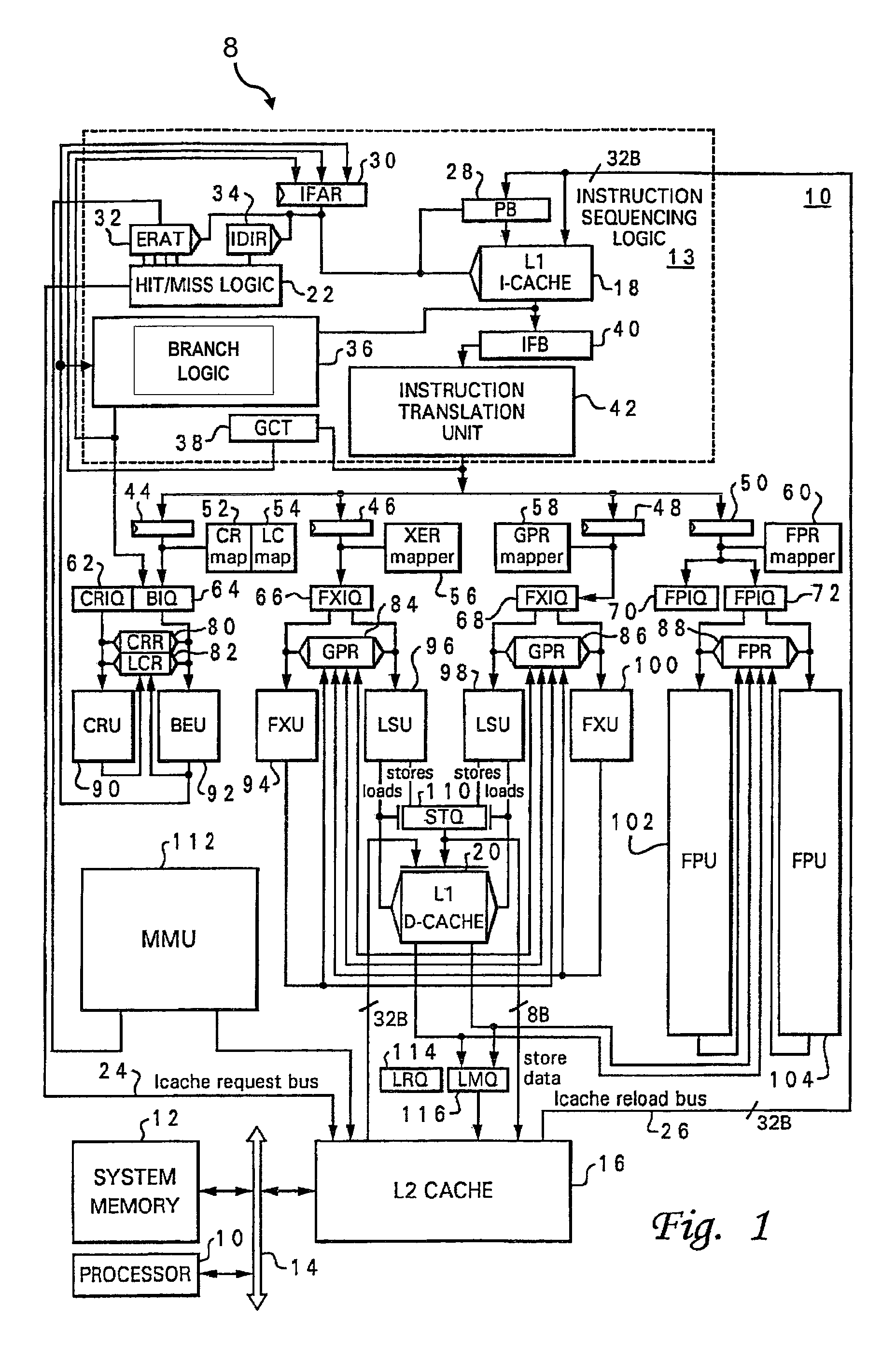

Data Processing System, Processor and Method of Data Processing Having Improved Branch Target Address Cache

InactiveUS20080120496A1Enhanced branch target address cacheConditional code generationRegister arrangementsData processing systemBranch target address cache

A processor includes an execution unit and instruction sequencing logic that fetches instructions for execution. The instruction sequencing logic includes a branch target address cache having a branch target buffer containing a plurality of entries each associating at least a portion of a branch instruction address with a predicted branch target address. The branch target address cache accesses the branch target buffer using a branch instruction address to obtain a predicted branch target address for use as an instruction fetch address. The branch target address cache also includes a filter buffer that buffers one or more candidate branch target address predictions. The filter buffer associates a respective confidence indication indicative of predictive accuracy with each candidate branch target address prediction. The branch target address cache promotes candidate branch target address predictions from the filter buffer to the branch target buffer based upon their respective confidence indications.

Owner:IBM CORP

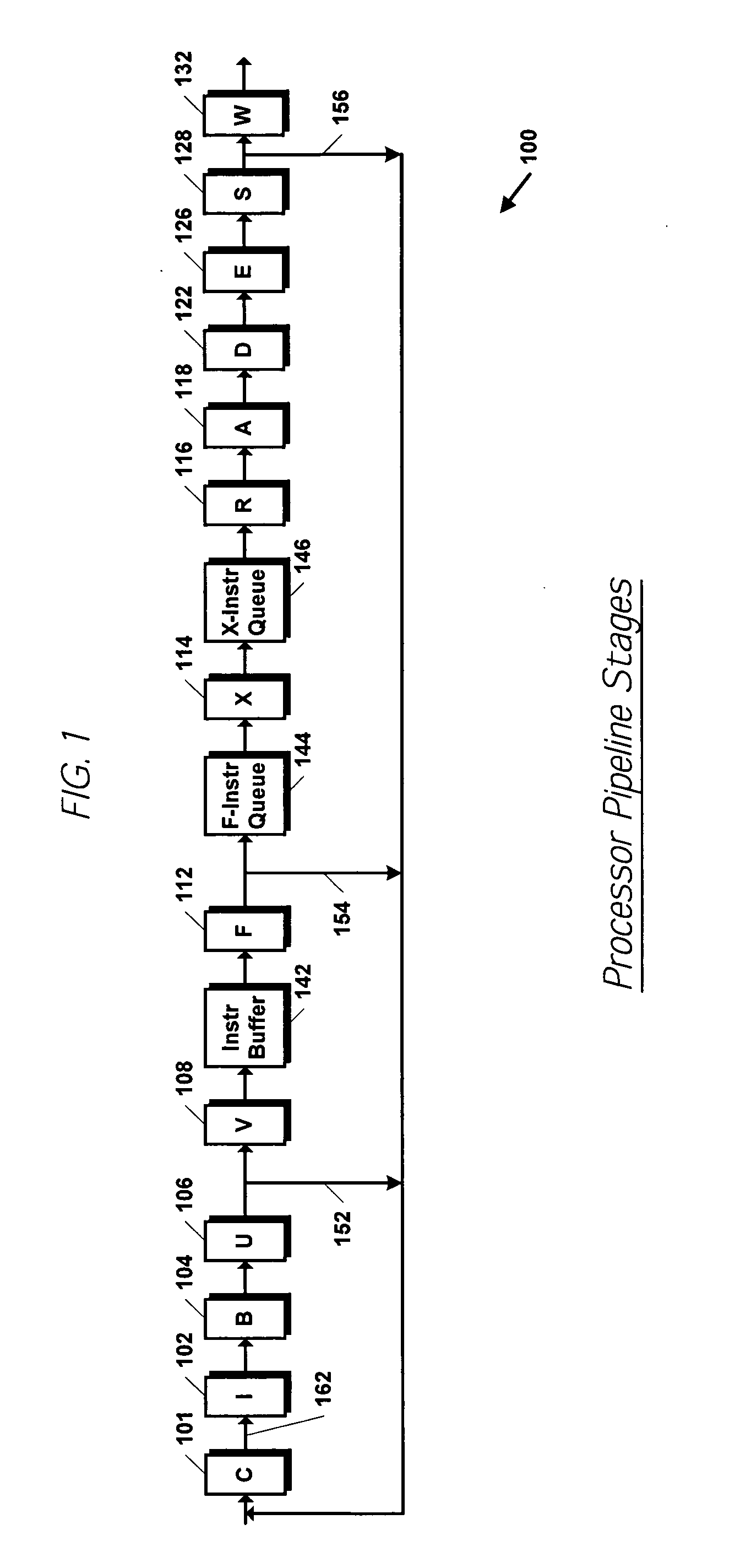

Apparatus and method for selectively accessing disparate instruction buffer stages based on branch target address cache hit and instruction stage wrap

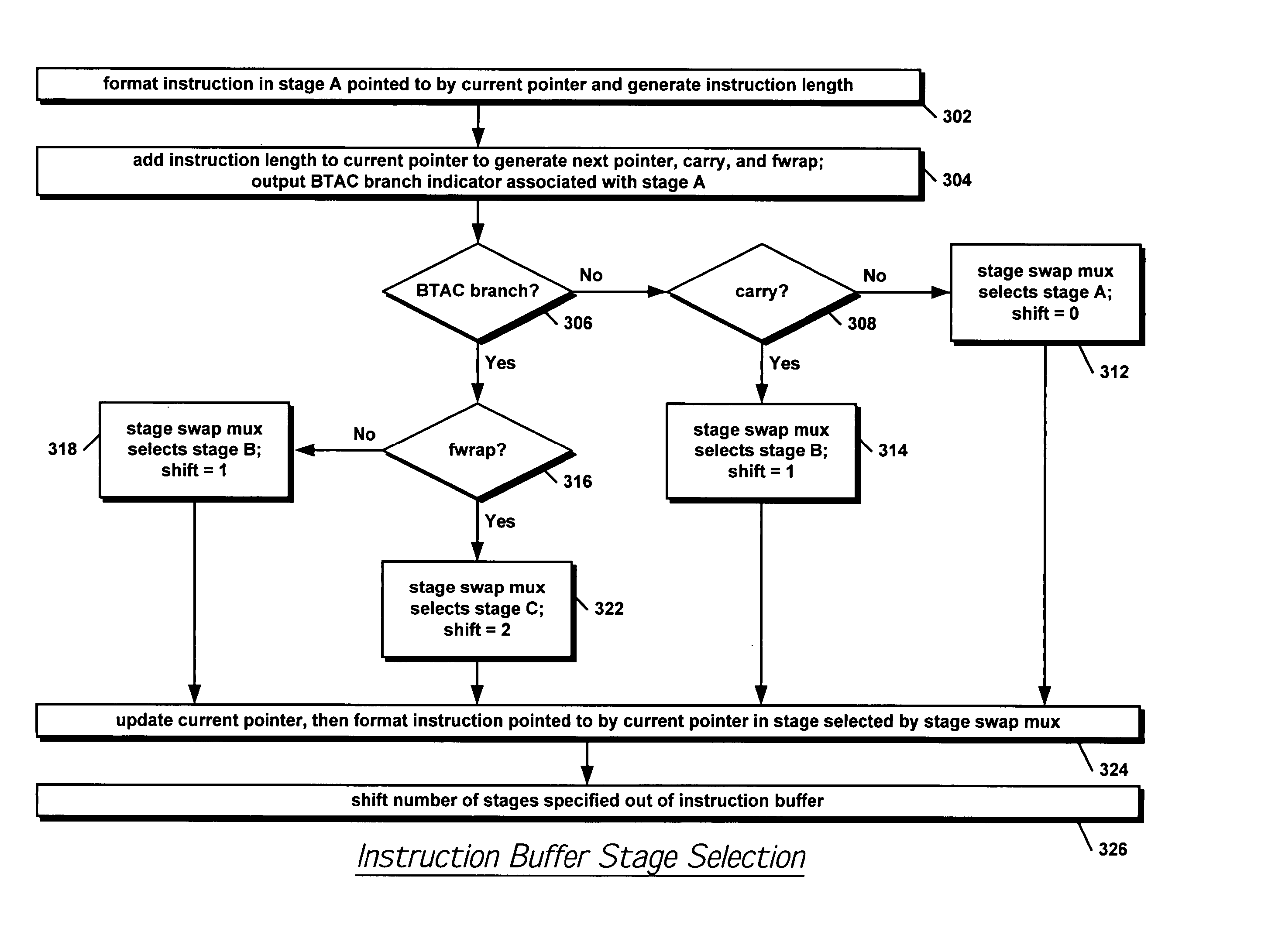

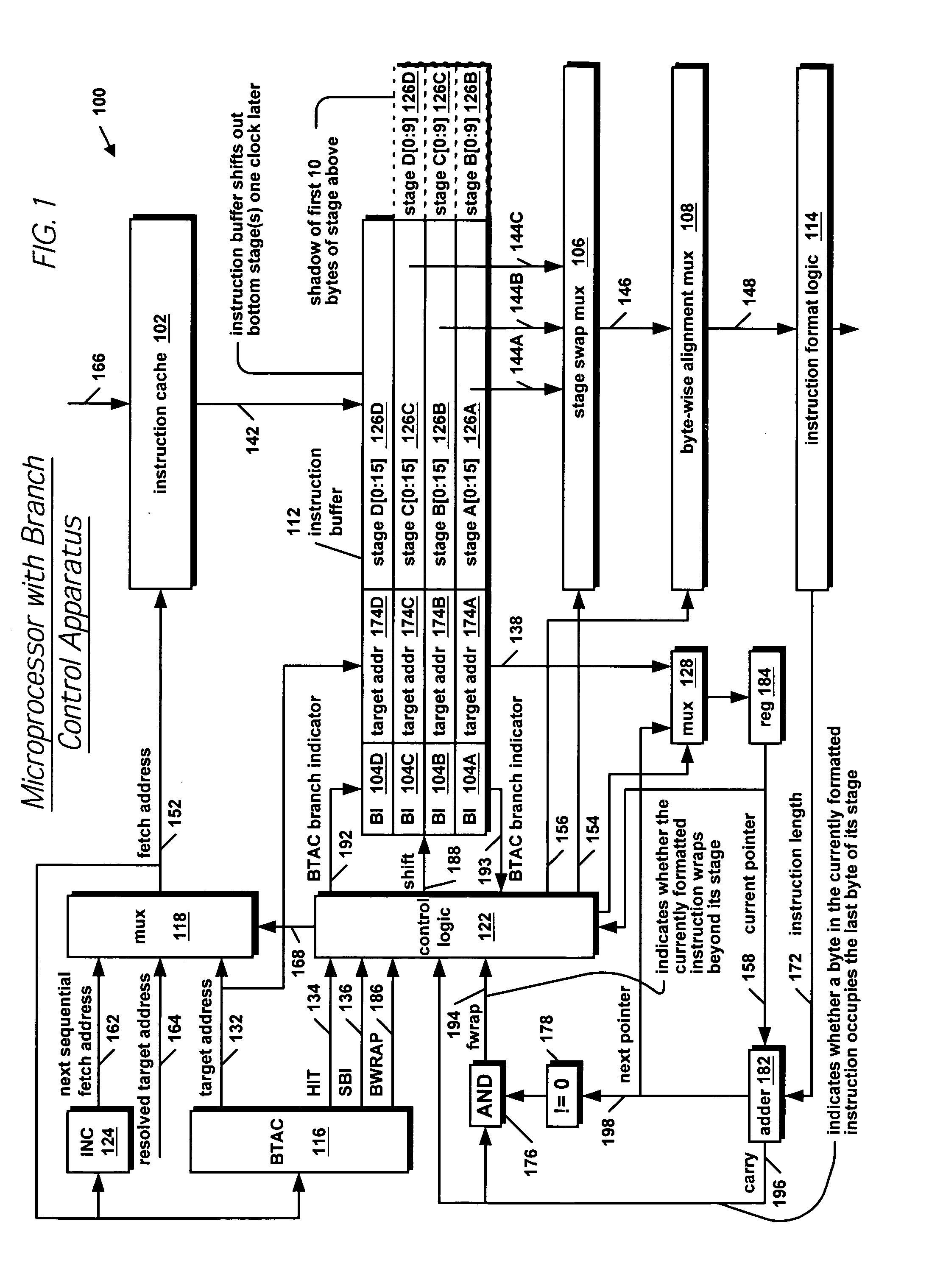

InactiveUS20050044343A1Increases the amount of cycle time availableZero penalty branchesInstruction analysisMemory adressing/allocation/relocationMultiplexerThree stage

A branch control apparatus in a microprocessor. The branch control apparatus includes an instruction buffer having a plurality of stages that buffer cache lines of instruction bytes received from an instruction cache. A multiplexer selects one of the bottom three stages in the instruction buffer to provide to instruction format logic. The multiplexer selects a stage based on a branch indicator, an instruction wrap indicator, and a carry indicator. The branch indicator indicates whether the processor previously branched to a target address provided by a branch target address cache. The branch indicator and target address are previously stored in association with the stage containing the branch instruction for which the target address is cached. The wrap indicator indicates whether the currently formatted instruction wraps across two cache lines. The carry indicator indicates whether the current instruction being formatted occupies the last byte of the currently formatted instruction buffer stage.

Owner:IP FIRST +1

Apparatus and method for target address replacement in speculative branch target address cache

InactiveUS20050114636A1Easy to useDigital computer detailsConcurrent instruction executionProcessor registerBranch target address cache

An apparatus and method in a pipelined microprocessor for replacing one of two target addresses in a branch target address cache (BTAC) line. If only one of the two entries is invalid, the invalid entry is replaced. If both entries are valid, the least recently used entry is replaced. If both entries are invalid, the entry is replaced corresponding to the side of the BTAC, indicated by a global status register, not last written to with an invalid entry. In one embodiment, the global status is updated only if a side is written when both entries are invalid. In another embodiment, the BTAC stores N entries per line, where N is greater than 1. The status register maintains information for determining which of the N sides is least recently written. The least recently written side is chosen for replacement.

Owner:IP FIRST

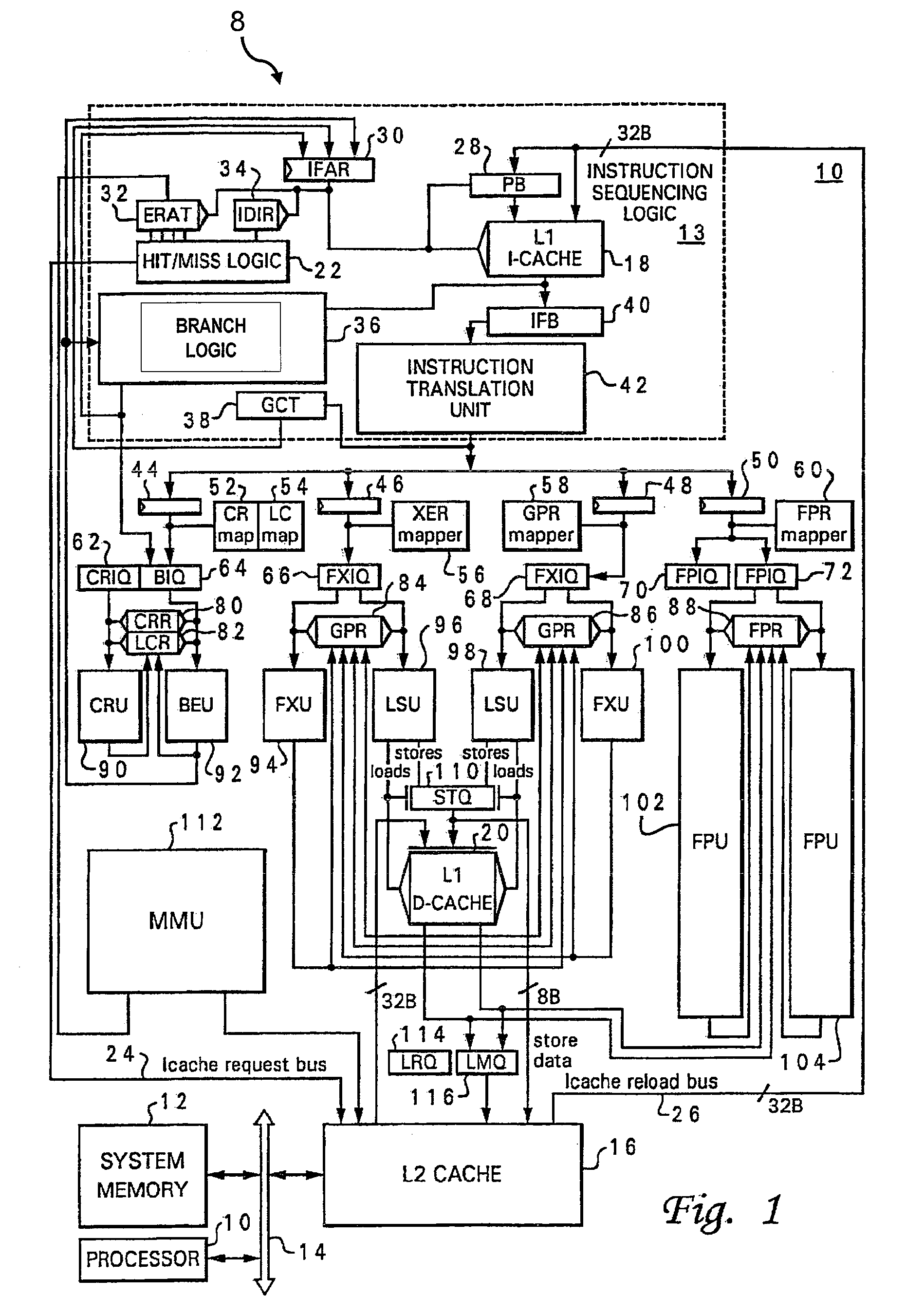

Data processing system, processor and method of data processing having improved branch target address cache

InactiveUS7707396B2Conditional code generationRegister arrangementsData processing systemBranch target address cache

A processor includes an execution unit and instruction sequencing logic that fetches instructions for execution. The instruction sequencing logic includes a branch target address cache having a branch target buffer containing a plurality of entries each associating at least a portion of a branch instruction address with a predicted branch target address. The branch target address cache accesses the branch target buffer using a branch instruction address to obtain a predicted branch target address for use as an instruction fetch address. The branch target address cache also includes a filter buffer that buffers one or more candidate branch target address predictions. The filter buffer associates a respective confidence indication indicative of predictive accuracy with each candidate branch target address prediction. The branch target address cache promotes candidate branch target address predictions from the filter buffer to the branch target buffer based upon their respective confidence indications.

Owner:IBM CORP

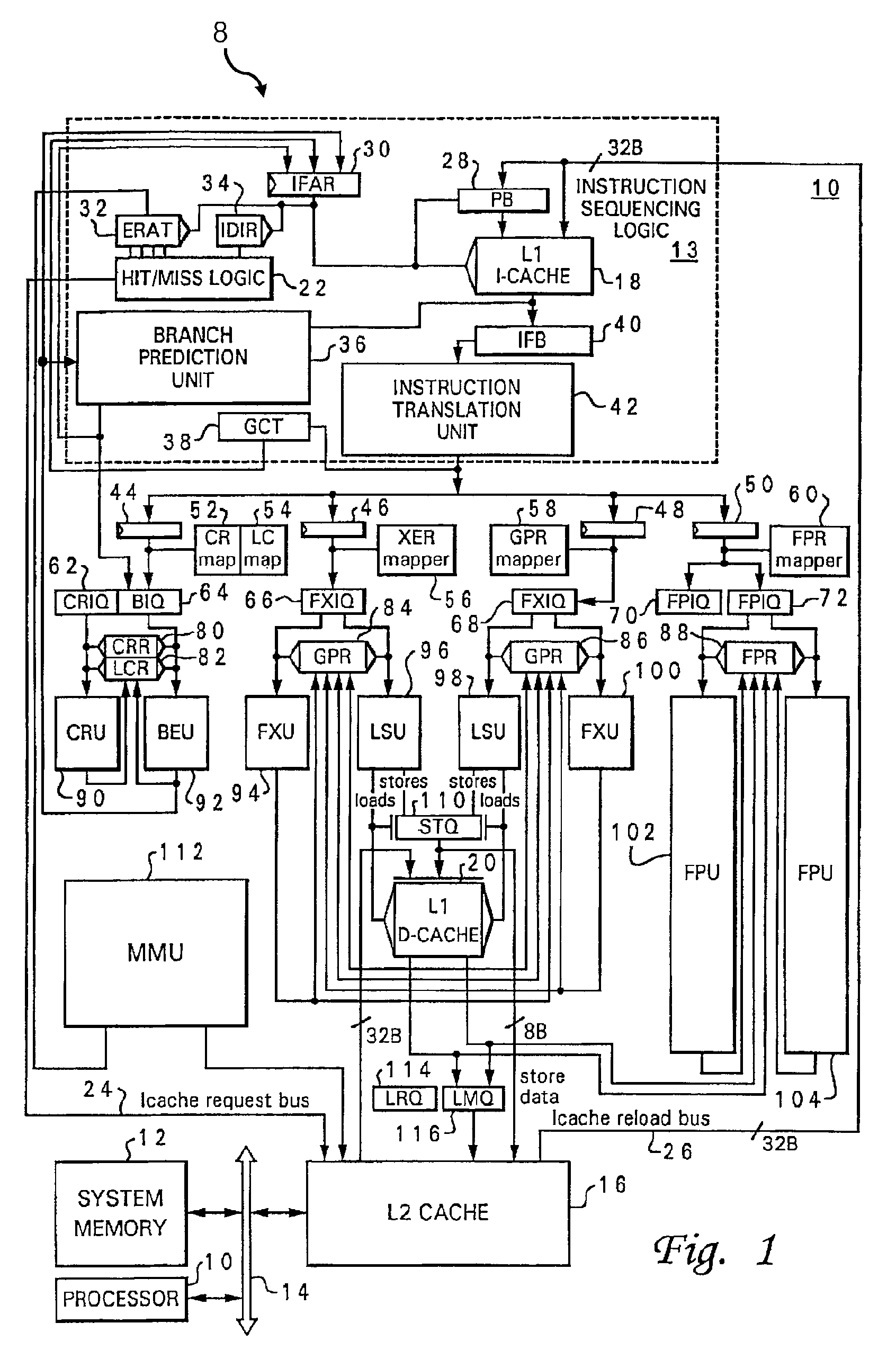

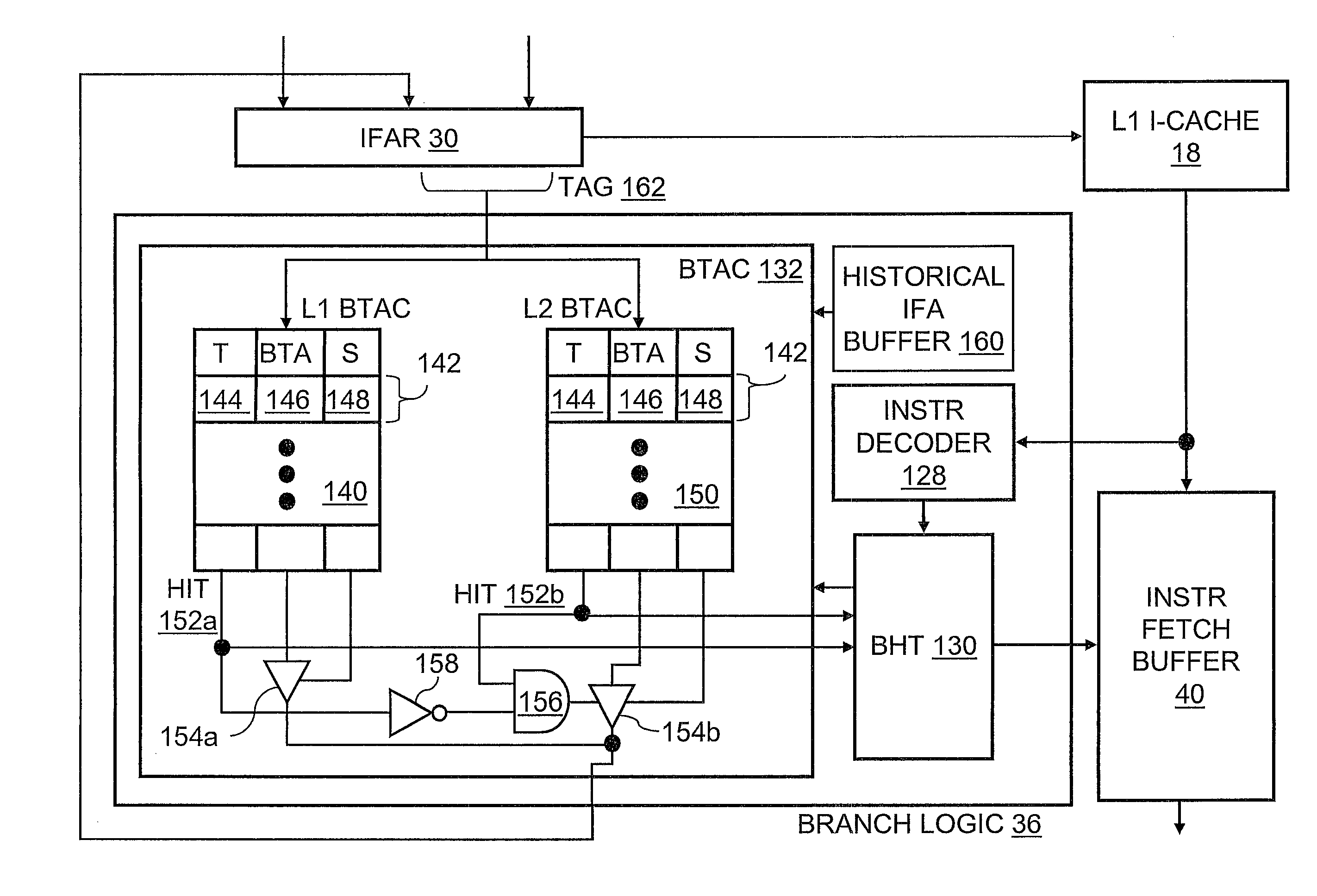

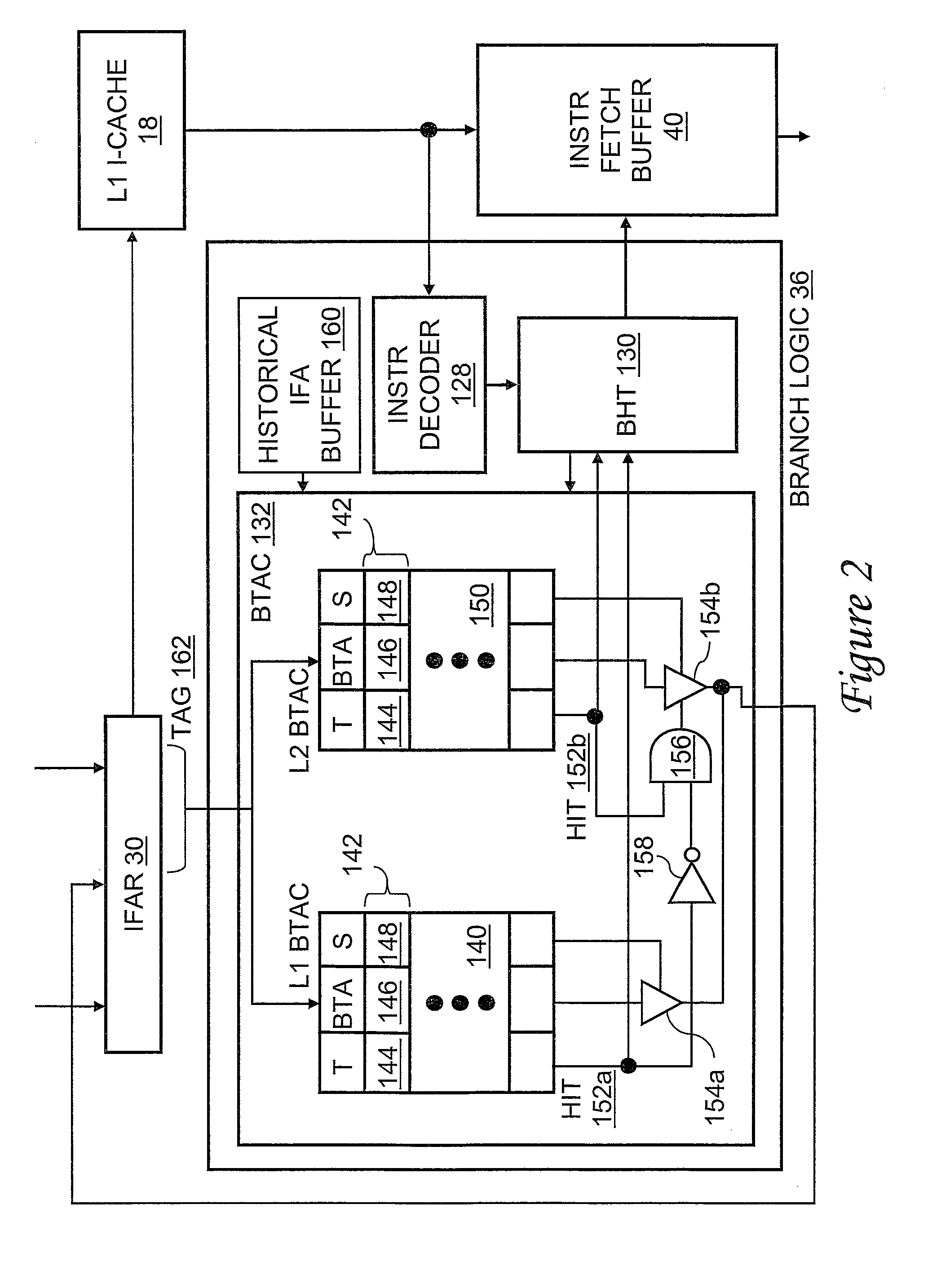

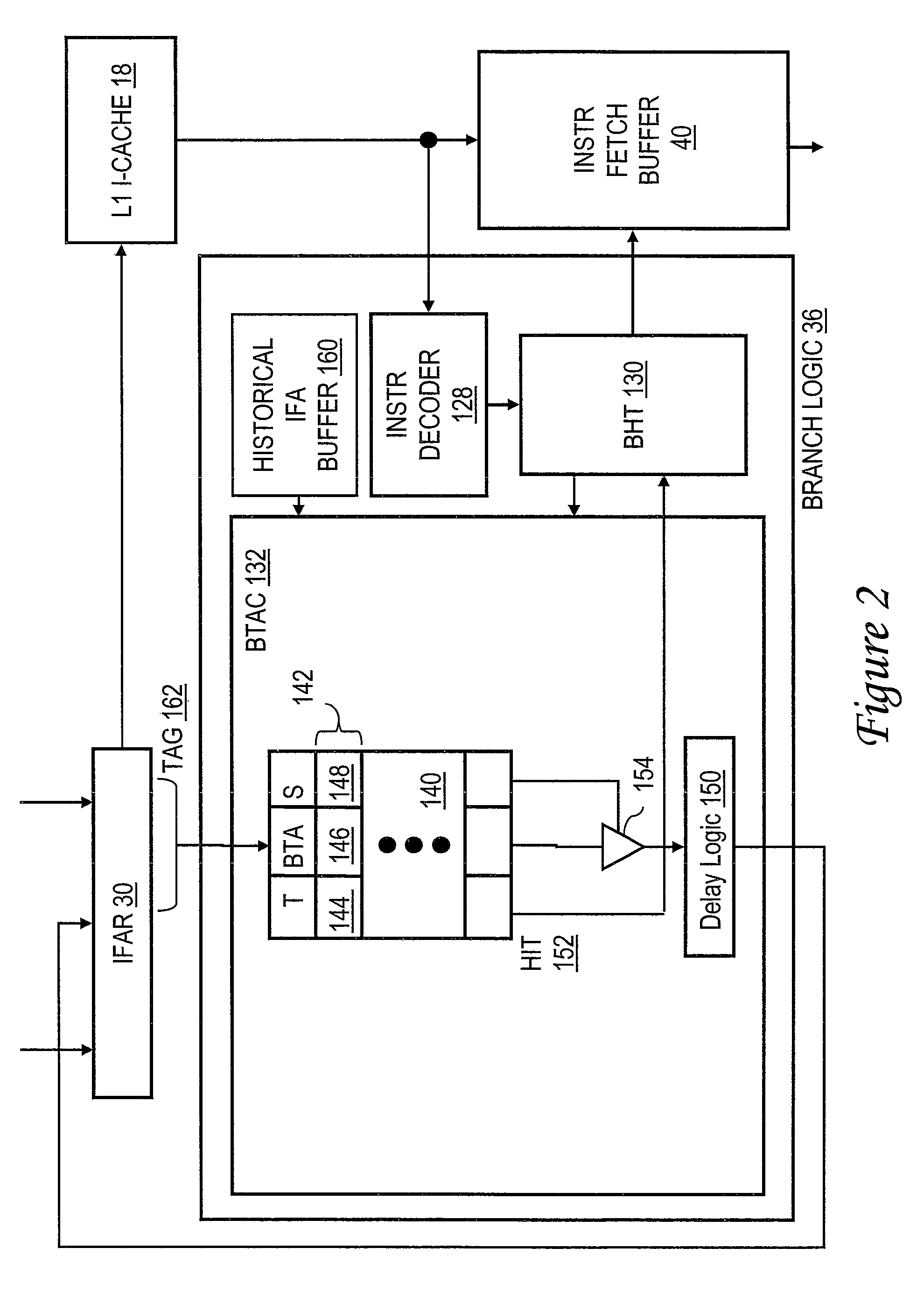

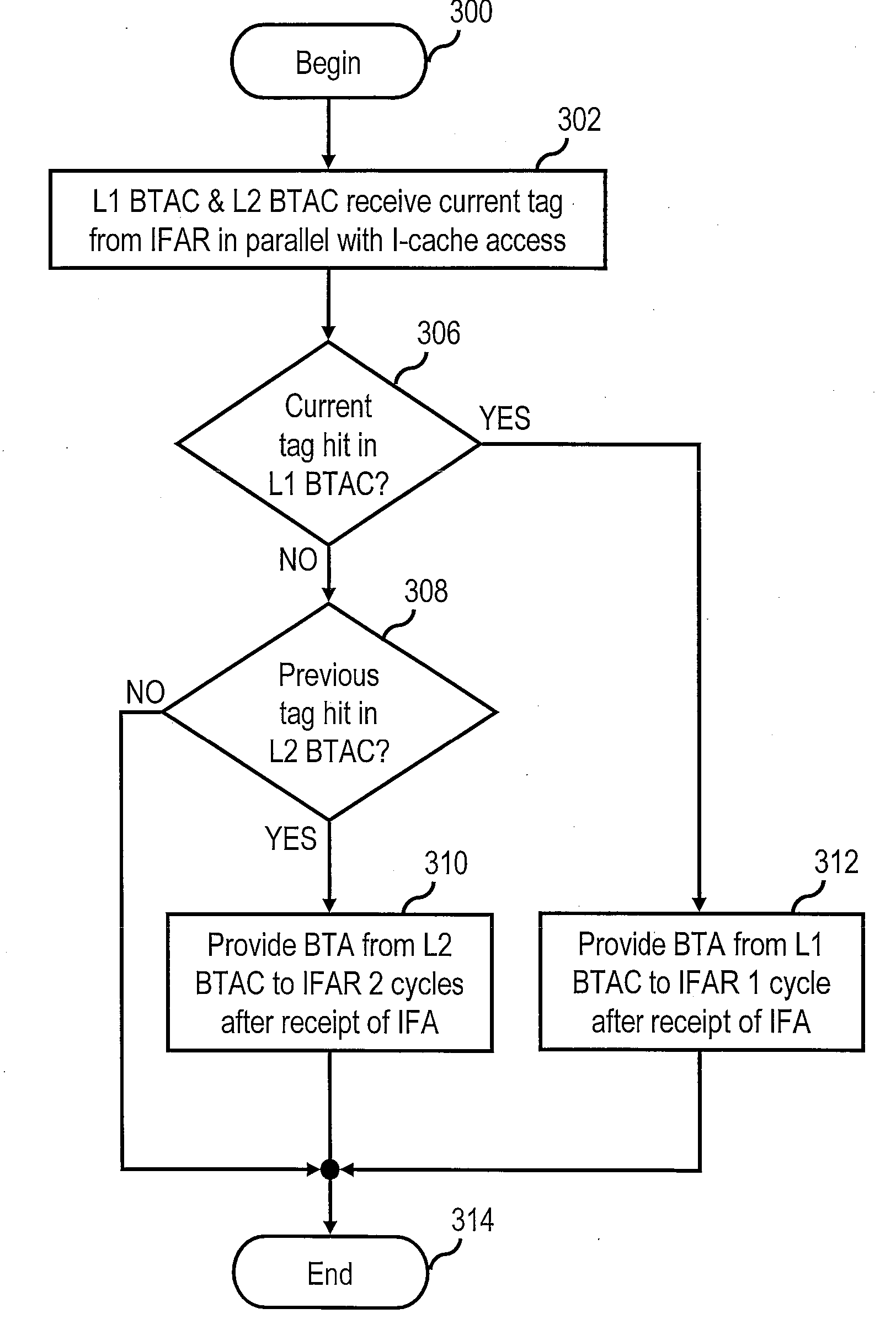

Branch target address cache

InactiveUS7783870B2Digital computer detailsNext instruction address formationBranch target address cacheParallel computing

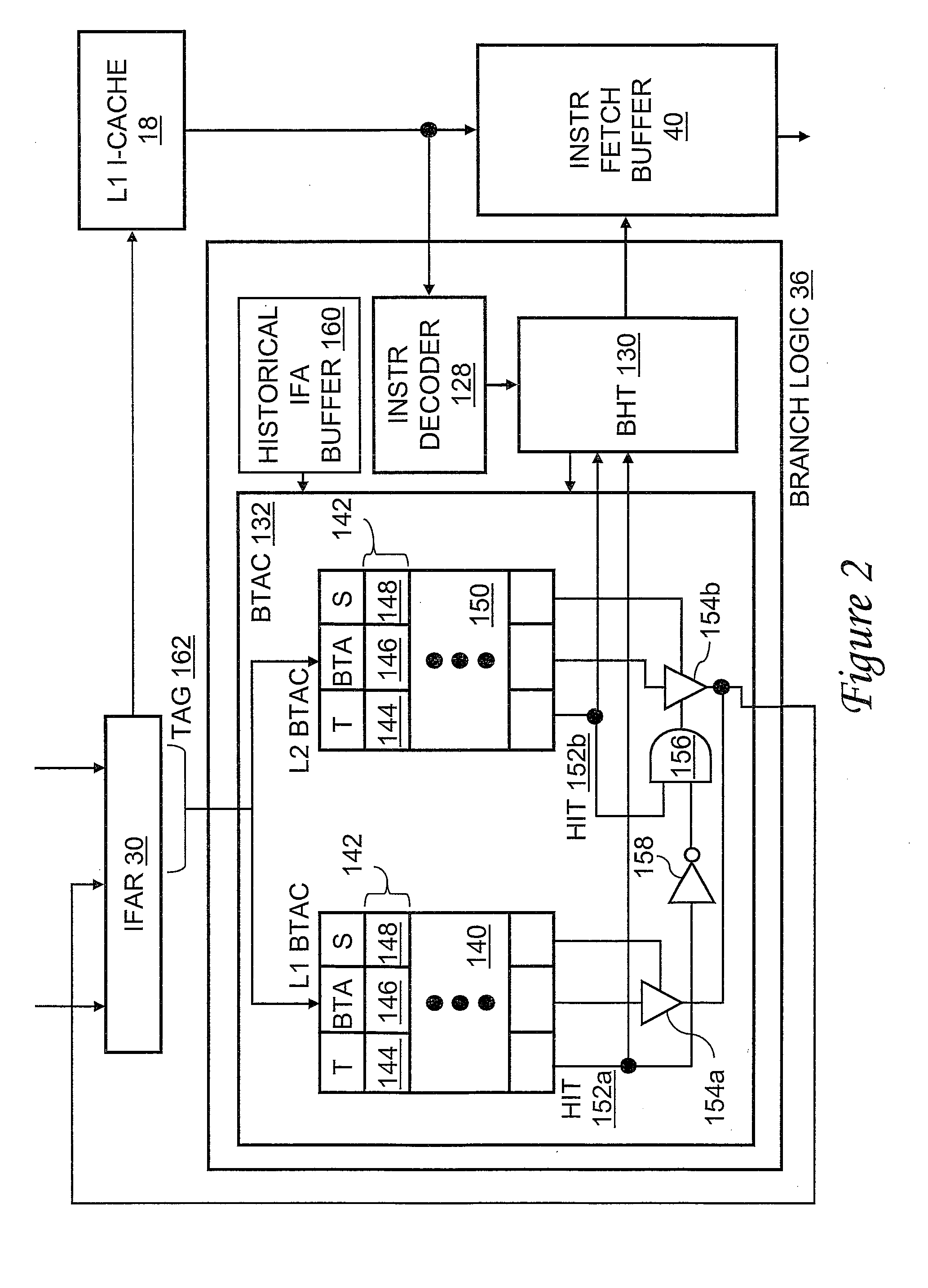

A processor includes an execution unit and instruction sequencing logic that fetches instructions from a memory system for execution. The instruction sequencing logic includes branch logic that outputs predicted branch target addresses for use as instruction fetch addresses. The branch logic includes a level one branch target address cache (BTAC) and a level two BTAC each having a respective plurality of entries each associating at least a tag with a predicted branch target address. The branch logic accesses the level one and level two BTACs in parallel with a tag portion of a first instruction fetch address to obtain a first predicted branch target address from the level one BTAC for use as a second instruction fetch address in a first processor clock cycle and a second predicted branch target address from the level two BTAC for use as a third instruction fetch address in a later second processor clock cycle.

Owner:IBM CORP

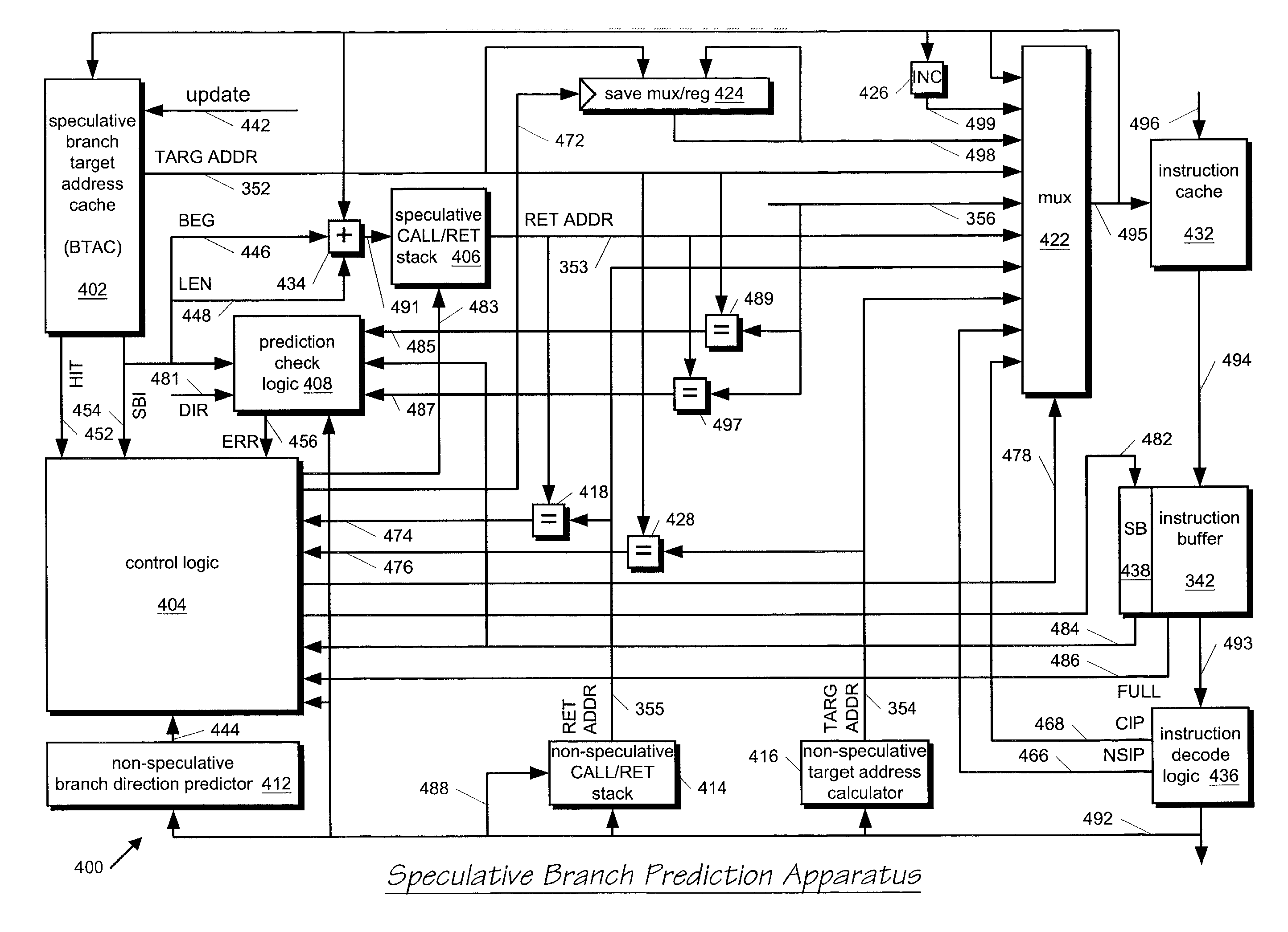

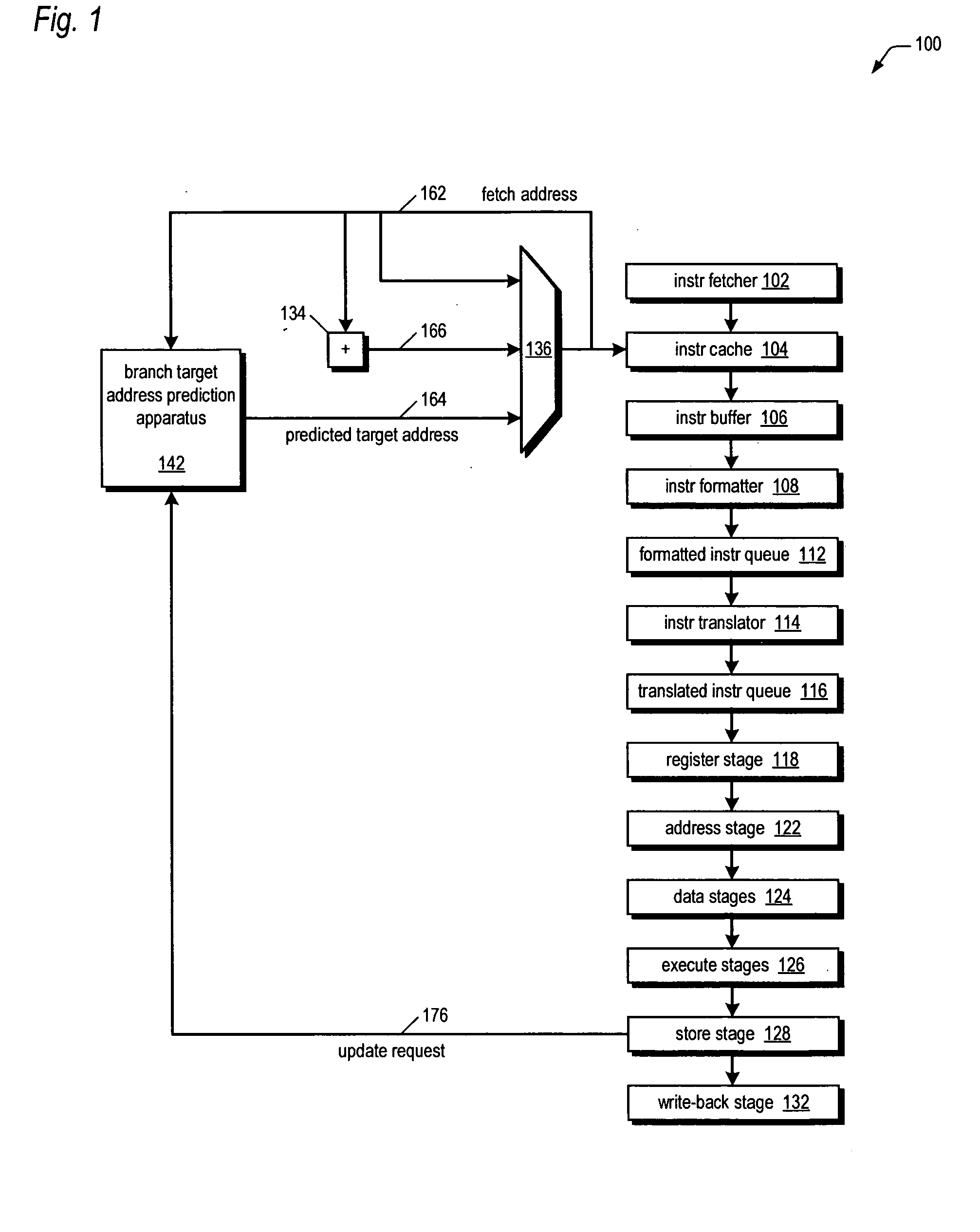

Speculative branch target address cache with selective override by secondary predictor based on branch instruction type

InactiveUS7165169B2Reduce negative impactAccurate predictionDigital computer detailsConcurrent instruction executionBranch target address cacheProgram counter

A branch prediction apparatus having a primary predictor and a secondary predictor that selectively overrides the primary predictor based on the type of branch instruction decoded. A branch target address cache in the primary branch predictor speculatively predicts a branch target address and direction based on an instruction cache fetch address prior to decoding the instruction, and the processor branches to the speculative target address if the speculative direction is predicted taken. Later in the pipeline, decode logic decodes the instruction and determines the branch instruction type, such as whether the branch instruction is a conditional branch, a return instruction, a program counter-relative type branch, an indirect branch, etc. Depending upon the branch type, if the primary and secondary predictions do not match, the processor branches based on the secondary prediction to override the branch taken based on the primary prediction.

Owner:IP FIRST

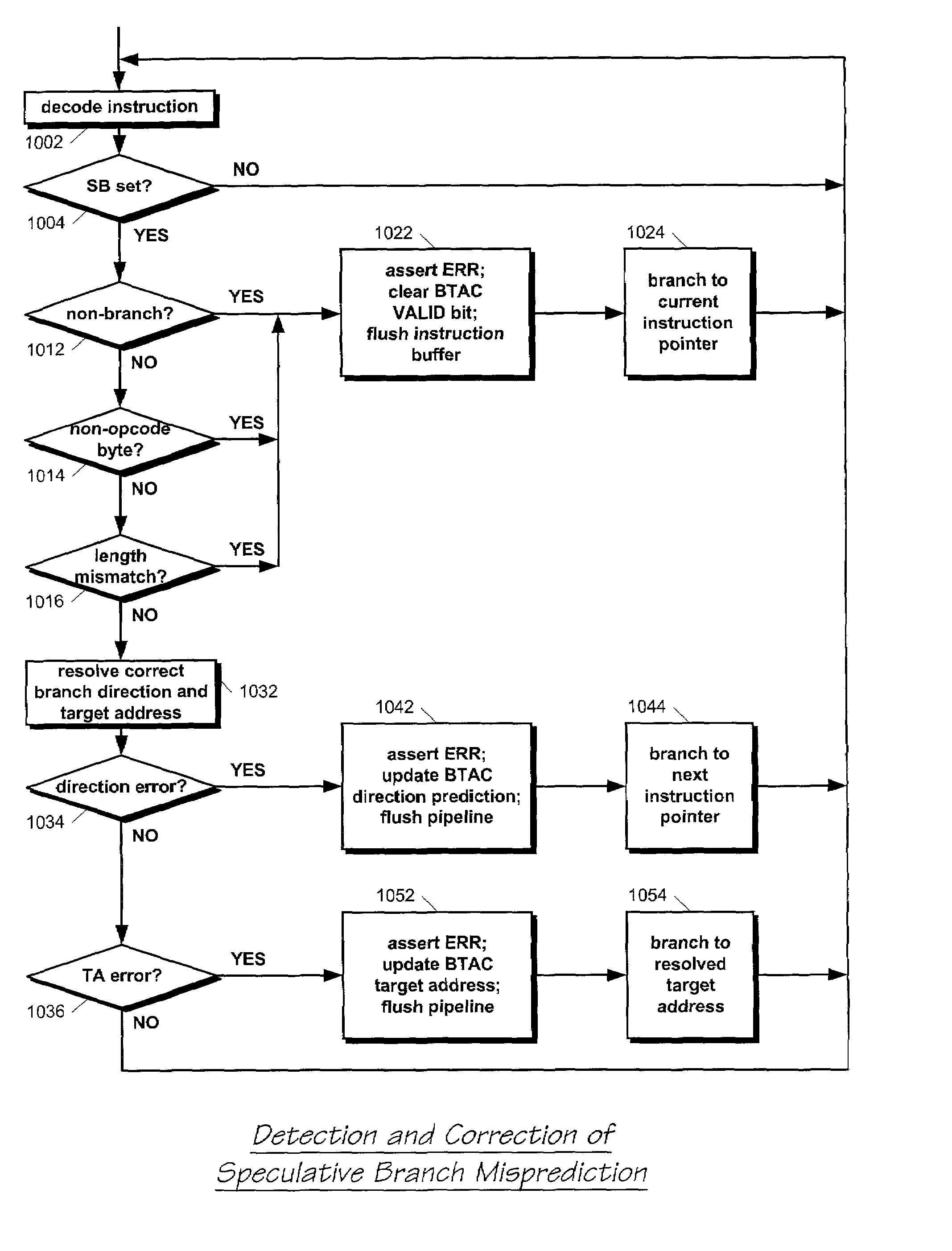

Microprocessor that detects erroneous speculative prediction of branch instruction opcode byte

InactiveUS7134005B2Easy to useImproved processor cycle timeDigital computer detailsConcurrent instruction executionParallel computingBranch target address cache

A microprocessor caches in a branch target address cache (BTAC), for each of a plurality of previously executed branch instructions: a prediction of whether the branch instruction will be taken and is present in a cache line of instruction bytes provided by an instruction cache in response to a fetch address, a target address of the branch instruction, and a location of an opcode byte of the branch instruction within the cache line. The instruction cache provides the cache line to an instruction buffer and the BTAC provides the prediction, the target address, and the location in response to the fetch address. The microprocessor branches to the target address. A byte in the cache line within the instruction buffer indicated by the location provided by the BTAC is marked. An instruction decoder formats the instruction bytes in the cache line. The microprocessor erroneously branched to the target address if the instruction decoder indicates the marked byte is in a non-opcode location within one of the formatted instructions.

Owner:IP FIRST

Apparatus and method for handling BTAC branches that wrap across instruction cache lines

InactiveUS20060010310A1Improves branch performanceAvoiding branch penaltyDigital computer detailsSpecific program execution arrangementsProcessor registerBranch target address cache

A branch control apparatus in a microprocessor. The apparatus includes a branch target address cache (BTAC) that caches indications of whether a branch instruction wraps across two cache lines. When an instruction cache fetch address of a first cache line containing the first part of the branch instruction hits in the BTAC, the BTAC outputs a target address of the branch instruction and indicates the wrap condition. The target address is stored in a register. The next sequential fetch address selects a second cache line containing the second part of the branch instruction. After the two cache lines containing the branch instruction are fetched, the target address from the register is provided to the instruction cache in order to fetch a third cache line containing a target instruction of the branch. The three cache lines are stored in order in an instruction buffer for decoding.

Owner:IP FIRST

Variable group associativity branch target address cache delivering multiple target addresses per cache line

ActiveUS20050268076A1Easy to useAchieving associativityDigital computer detailsNext instruction address formationParallel computingBranch target address cache

A branch prediction apparatus having two two-way set associative cache memories each indexed by a lower portion of an instruction cache fetch address is disclosed. The index selects a group of four entries, one from each way of each cache. Each entry stores a single target address of a different previously executed branch instruction. For some groups, the four entries cache target addresses for one branch instruction in each of four different cache lines, to obtain four-way group associativity; for other groups, the four entries cache target addresses for one branch instruction in each of two different cache lines and two branch instructions in a third different cache line, to effectively obtain three-way group associativity, depending on the distribution of the branch instructions in the program. The apparatus trades off associativity for number of predictable branches per cache line on an index-by-index basis to efficiently use storage space.

Owner:VIA TECH INC

Apparatus and method for handling BTAC branches that wrap across instruction cache lines

InactiveUS7203824B2Improves branch performanceAvoiding the branch penaltyInstruction analysisRuntime instruction translationProcessor registerBranch target address cache

A branch control apparatus in a microprocessor. The apparatus includes a branch target address cache (BTAC) that caches indications of whether a branch instruction wraps across two cache lines. When an instruction cache fetch address of a first cache line containing the first part of the branch instruction hits in the BTAC, the BTAC outputs a target address of the branch instruction and indicates the wrap condition. The target address is stored in a register. The next sequential fetch address selects a second cache line containing the second part of the branch instruction. After the two cache lines containing the branch instruction are fetched, the target address from the register is provided to the instruction cache in order to fetch a third cache line containing a target instruction of the branch. The three cache lines are stored in order in an instruction buffer for decoding.

Owner:IP FIRST

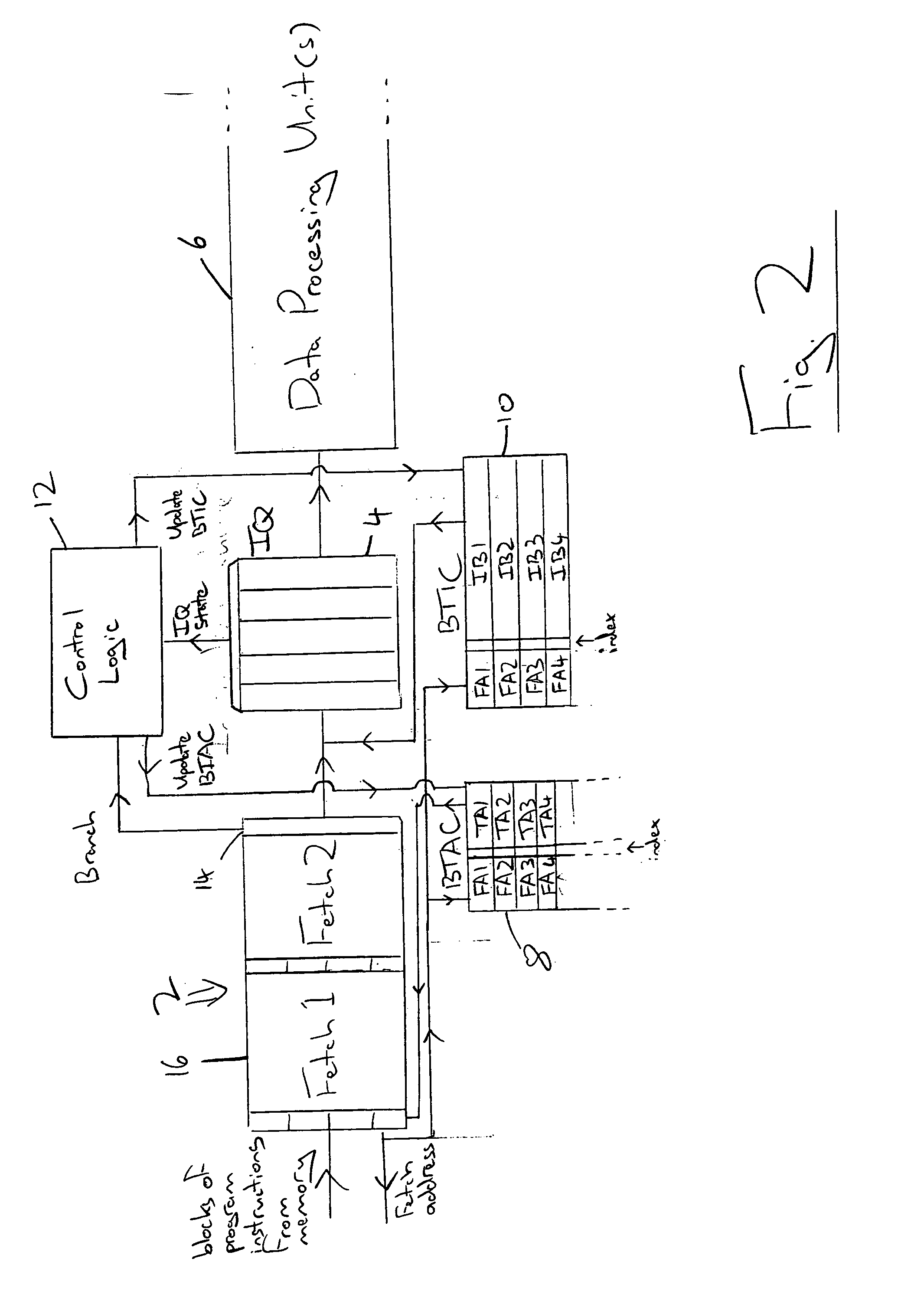

Control of a branch target cache within a data processing system

InactiveUS20080040592A1Improve accuracyImprove efficiencyMemory architecture accessing/allocationEnergy efficient ICTData processing systemProgram instruction

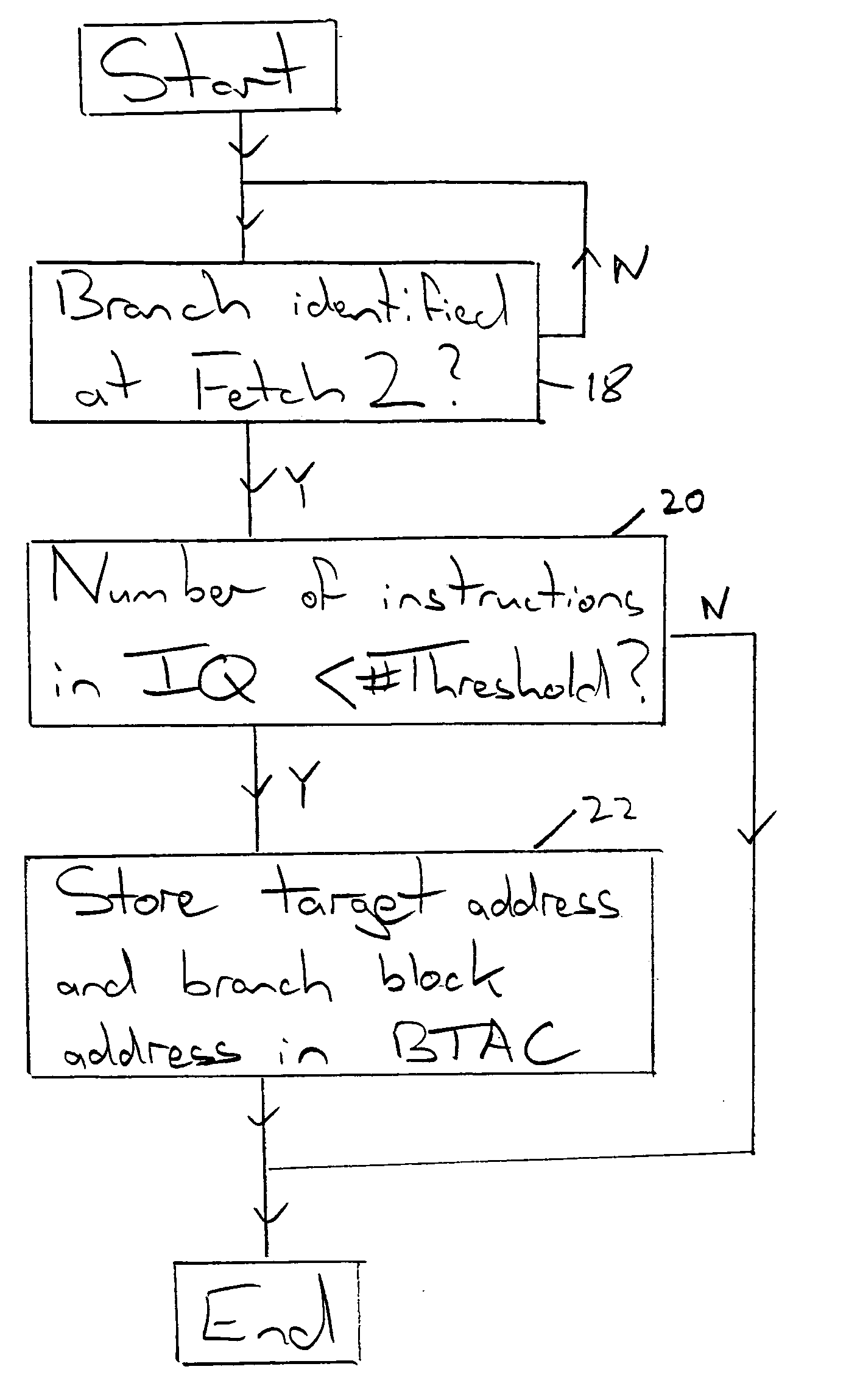

A data processing system includes an instruction fetching circuit 2, an instruction queue 4 and further processing circuits 6. A branch target cache, which maybe a branch target address cache 8, a branch target instruction cache 10 or both, is used to store branch target addresses or blocks of instructions starting at the branch target respectively. A control circuit 12 is responsive to the contents of the instruction queue 4 when a branch instruction is encountered to determine whether or not storage resources within the branch target cache 8, 10 should be allocated to that branch instruction. Storage resources within the branch target cache 8, 10 will be allocated when the number of program instructions within the instruction queue is below a threshold number and / or the estimated execution time of the program instructions is below a threshold time.

Owner:ARM LTD

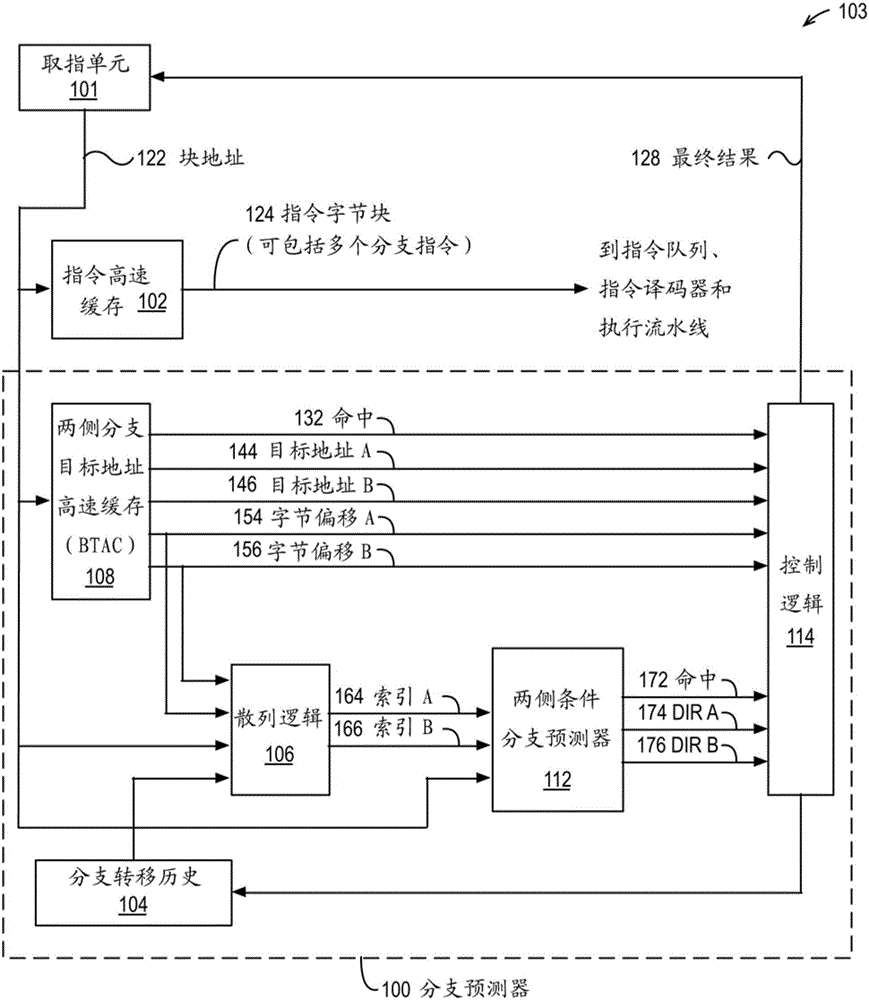

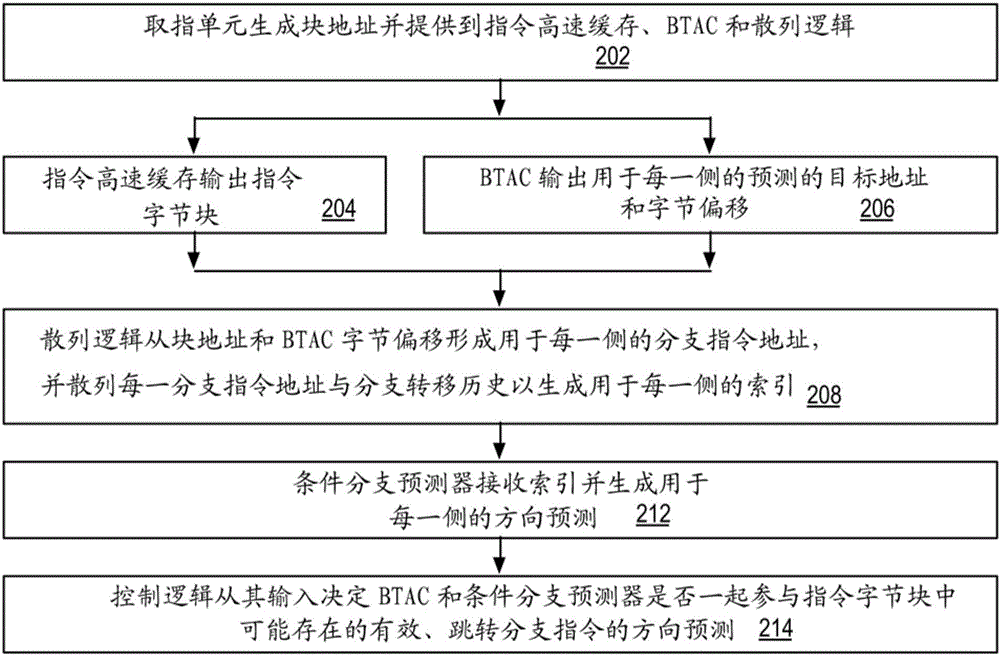

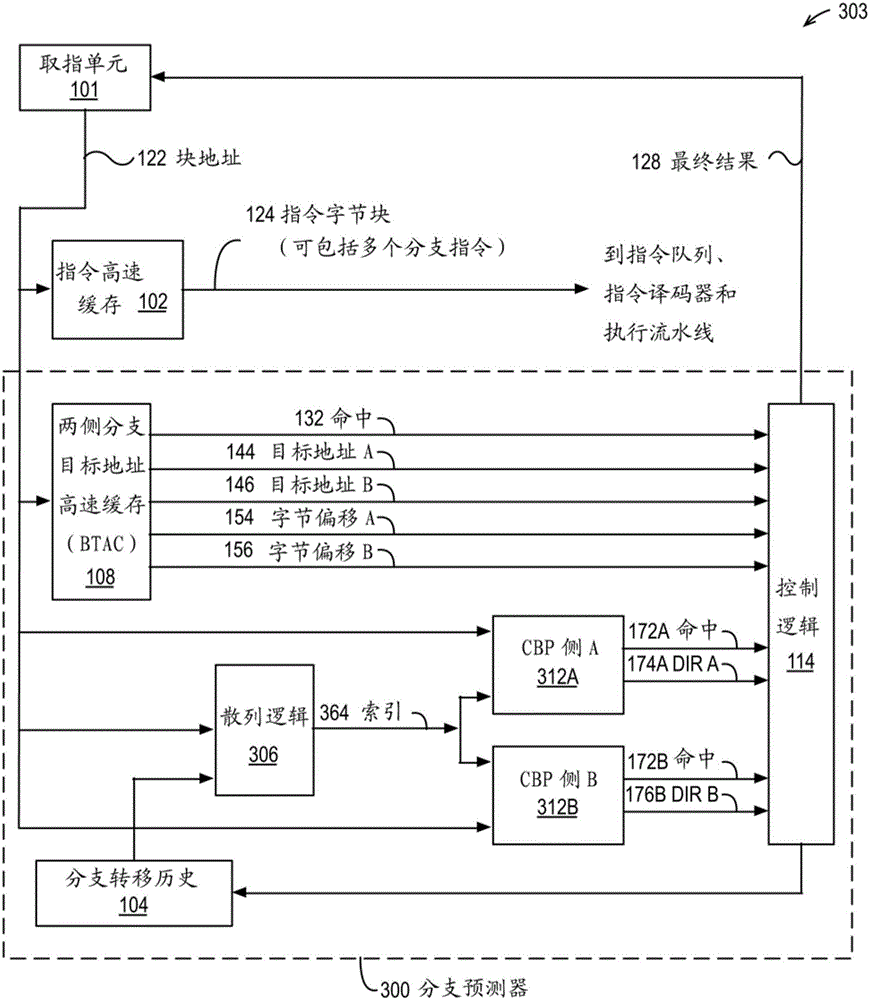

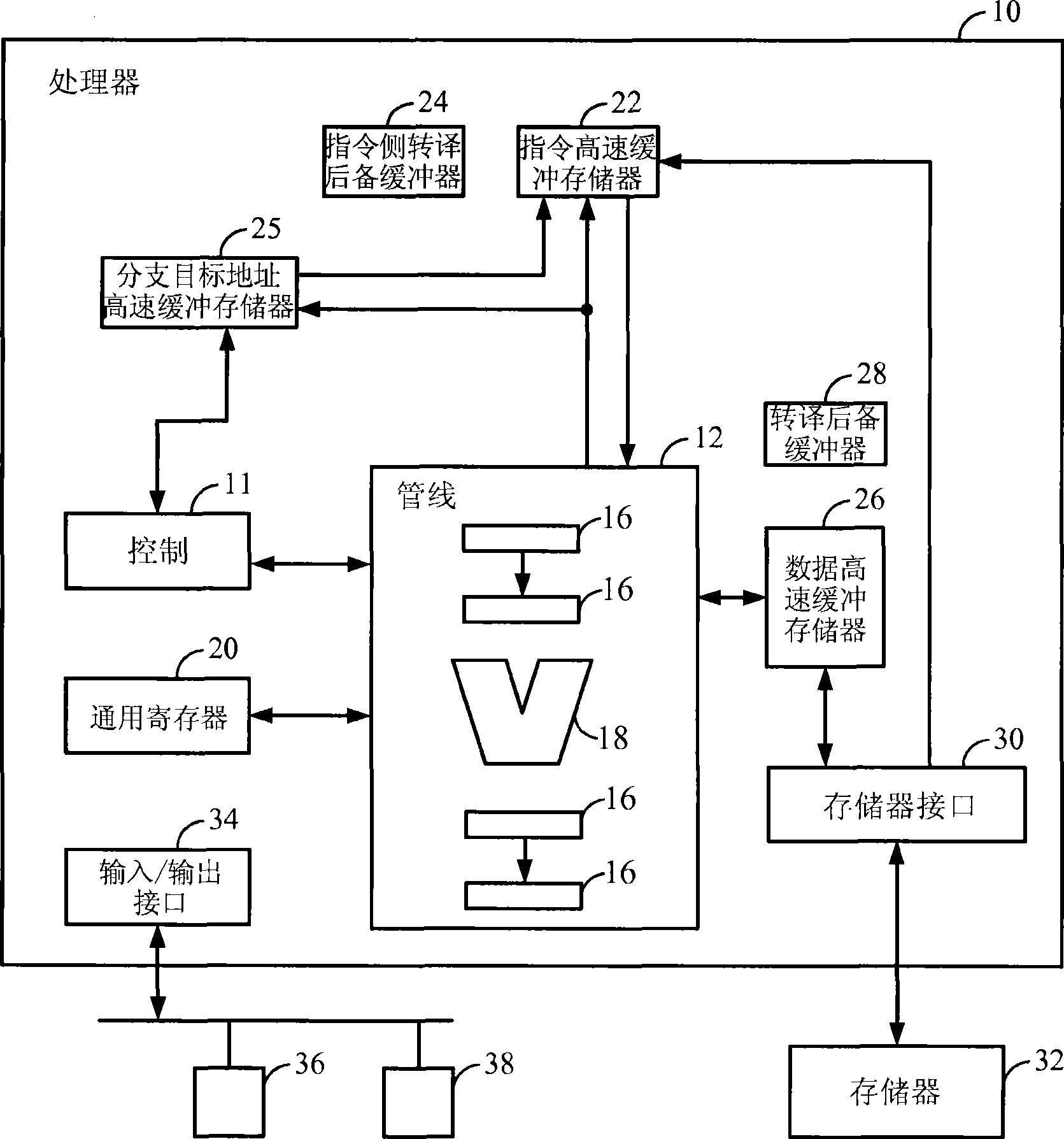

Branch predictor and method used for operating same

ActiveCN106406823AMemory architecture accessing/allocationConcurrent instruction executionBranch target address cacheByte

The invention provides a branch predictor and a method for operating the same. The branch predictor contains a block address capable of being used for accessing an instruction byte block of an instruction cache and a first / second byte offset in the instruction byte block. Hash logic performs hash operation on a branch pattern and a first / second address formed by the block address and the first / second byte offset to generate a first / second index. A condition branch predictor receives the first / second index and provides a first / second direction prediction of a first / second condition branch instruction in the instruction byte block in response to the first / second index. In an embodiment, a branch target address cache (BTAC) provides the byte offset, and the first / second direction prediction is statically associated with a first / second target address also provided by the BTAC. Instead, the byte offset is a predetermined value, and the first / second direction prediction is dynamically associated with the first / second target address based on the relative size of the byte offset provided by the BTAC.

Owner:VIA ALLIANCE SEMICON CO LTD

Microprocessor with multiple operating modes dynamically configurable by a device driver based on currently running applications

ActiveUS8566565B2Improve performanceReduce power consumptionDigital data processing detailsRuntime instruction translationBranch target address cacheApplication software

A computing system includes a microprocessor that receives values for configuring operating modes thereof. A device driver monitors which software applications currently running on the microprocessor are in a predetermined list and responsively dynamically writes the values to the microprocessor to configure its operating modes. Examples of the operating modes the device driver may configure relate to the following: data prefetching; branch prediction; instruction cache eviction; instruction execution suspension; sizes of cache memories, reorder buffer, store / load / fill queues; hashing algorithms related to data forwarding and branch target address cache indexing; number of instruction translation, formatting, and issuing per clock cycle; load delay mechanism; speculative page tablewalks; instruction merging; out-of-order execution extent; caching of non-temporal hinted data; and serial or parallel access of an L2 cache and processor bus in response to an instruction cache miss.

Owner:VIA TECH INC

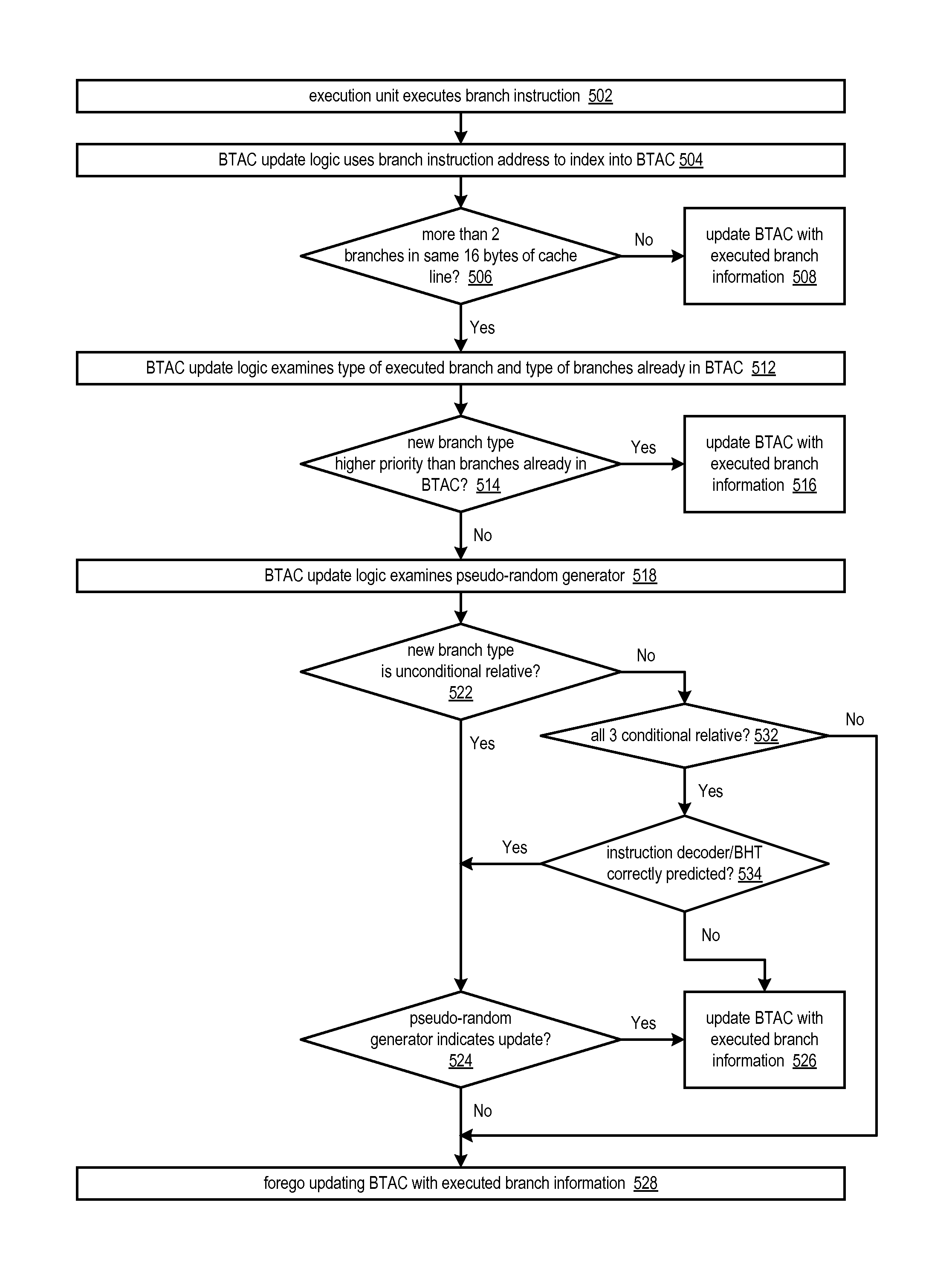

Efficient branch target address cache entry replacement

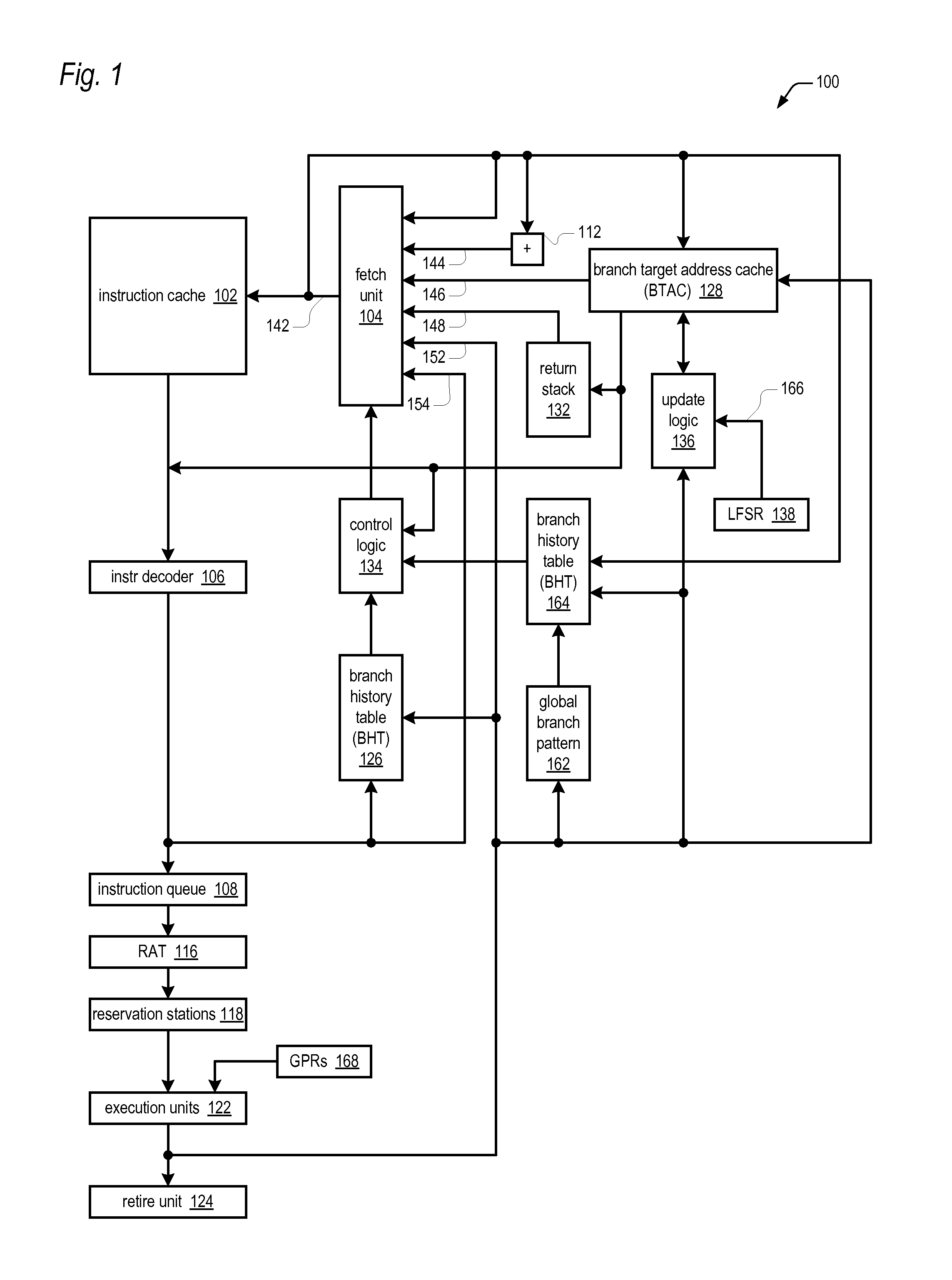

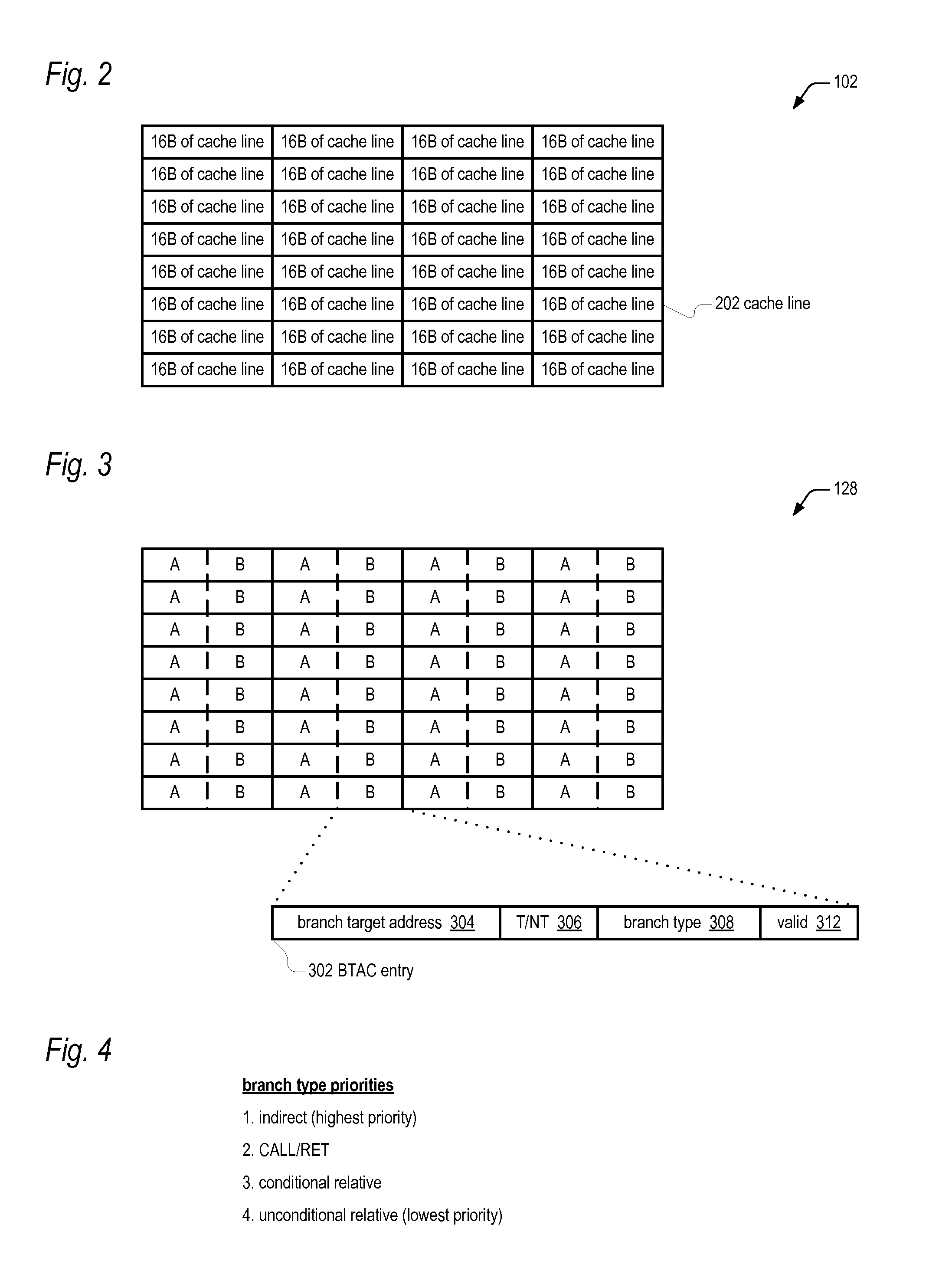

ActiveUS20110055529A1High replacement priorityMemory adressing/allocation/relocationDigital computer detailsBranch target address cacheParallel computing

A microprocessor includes a branch target address cache (BTAC), each entry thereof configured to store branch prediction information for at most N branch instructions. An execution unit executes a branch instruction previously fetched in a fetch quantum. Update logic determines whether the BTAC is already storing information for N branch instructions within the fetch quantum (N is at least two), updates the BTAC for the branch instruction if the BTAC is not already storing information for N branch instructions, determines whether a type of the branch instruction has a higher replacement priority than a type of the N branch instructions if the BTAC is already storing information for N branch instructions, and updates the BTAC for the branch instruction if the type of the branch instruction has a higher replacement priority than the type of the N branch instructions already stored in the BTAC.

Owner:VIA TECH INC

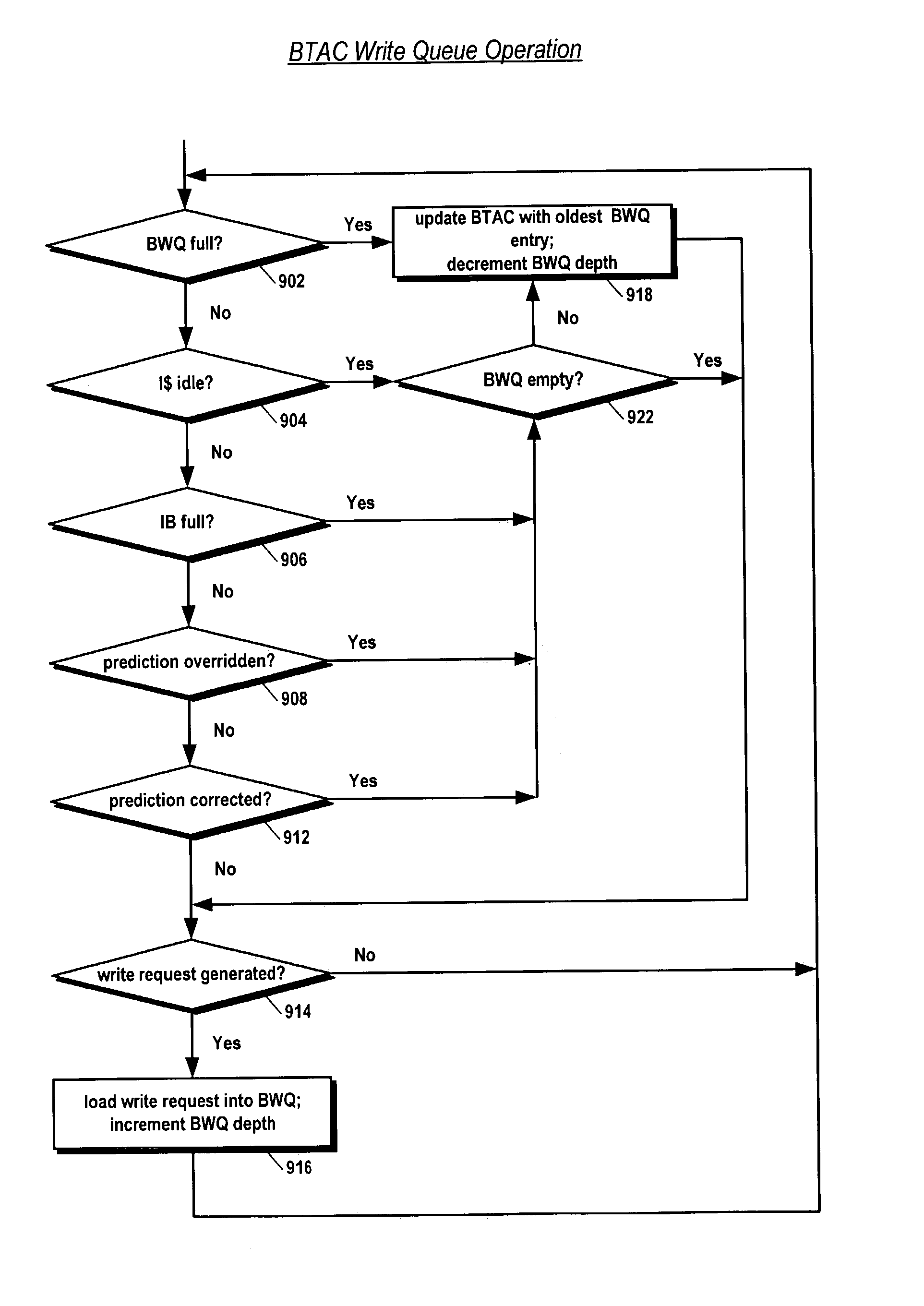

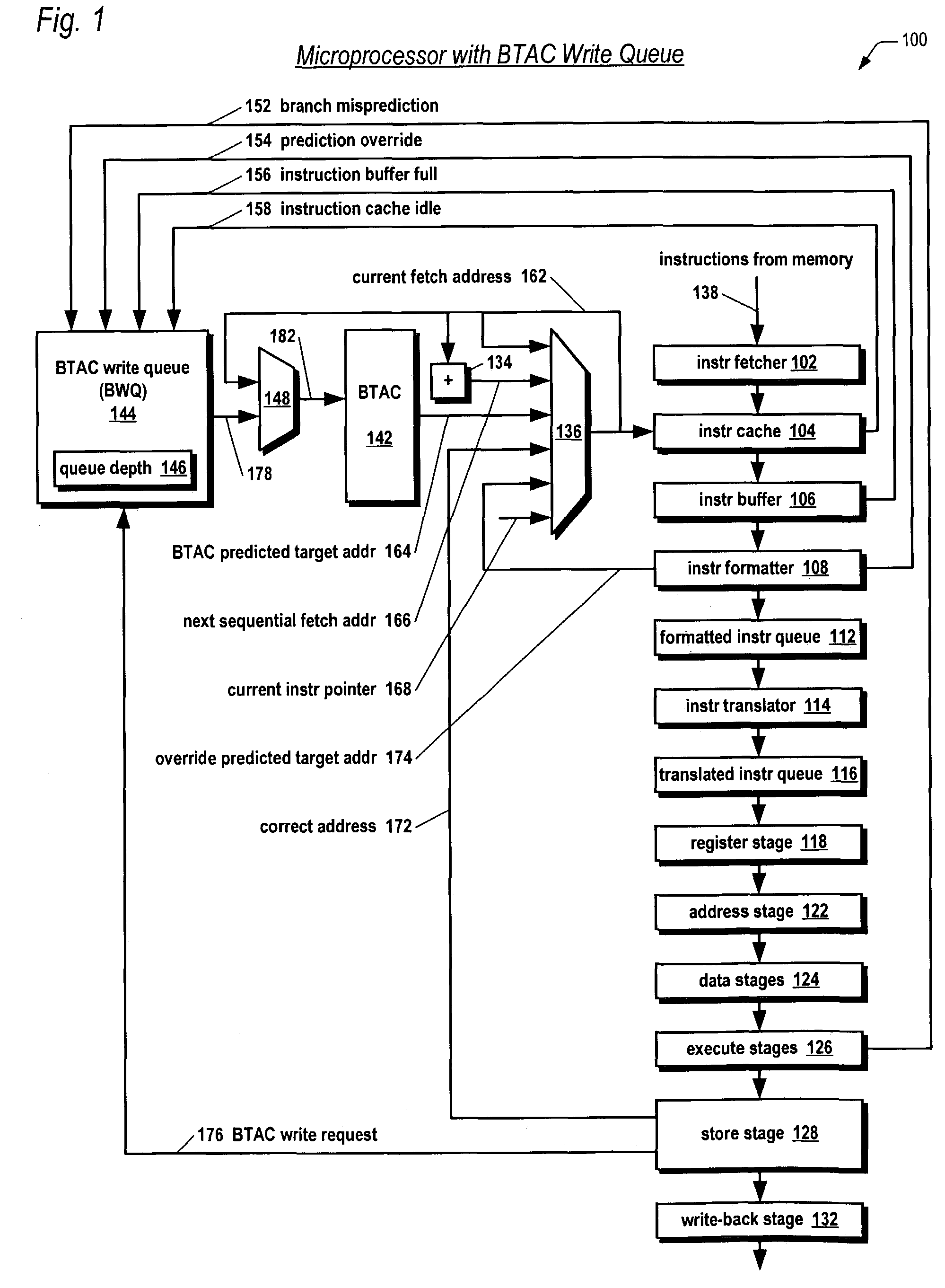

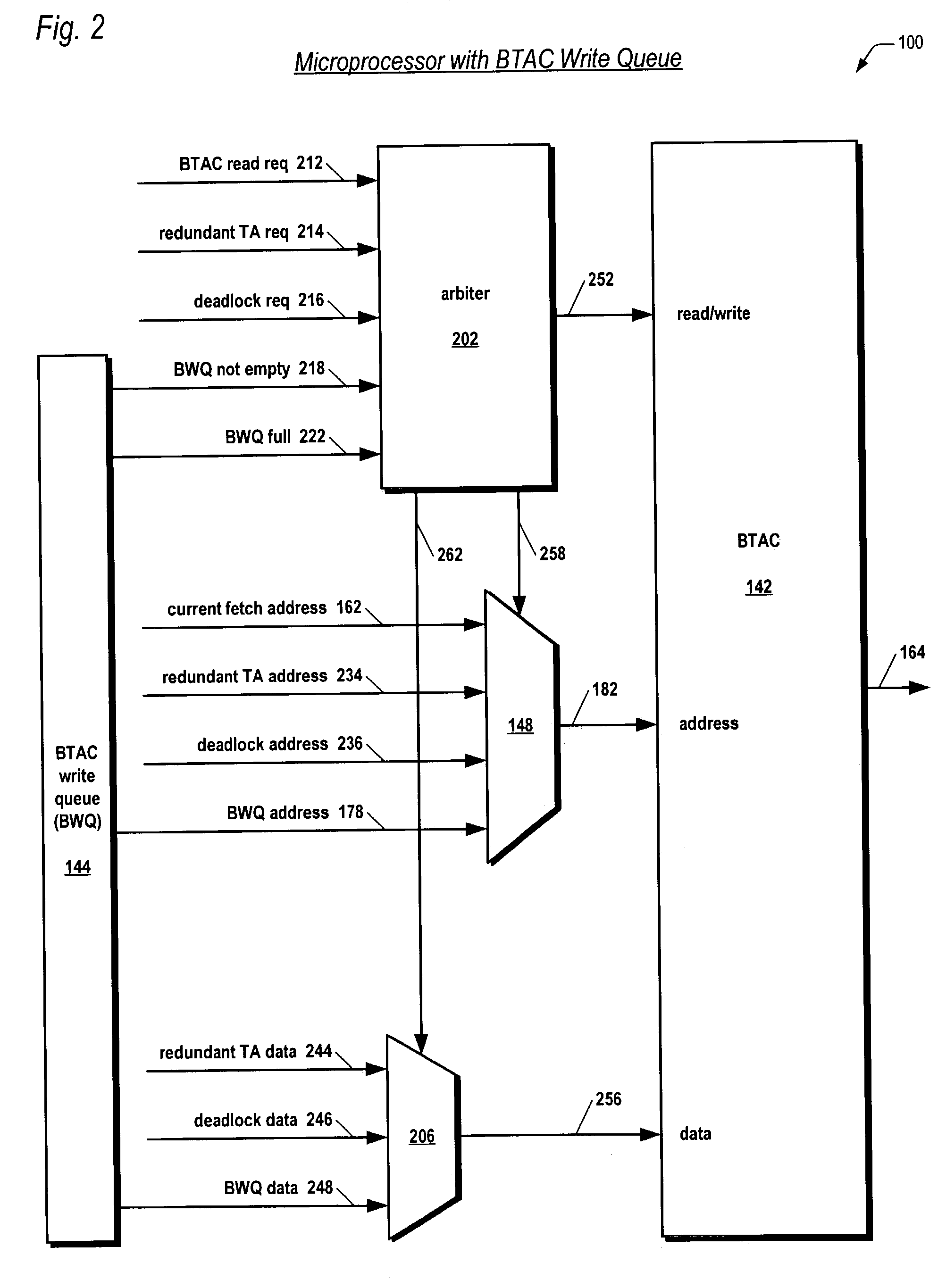

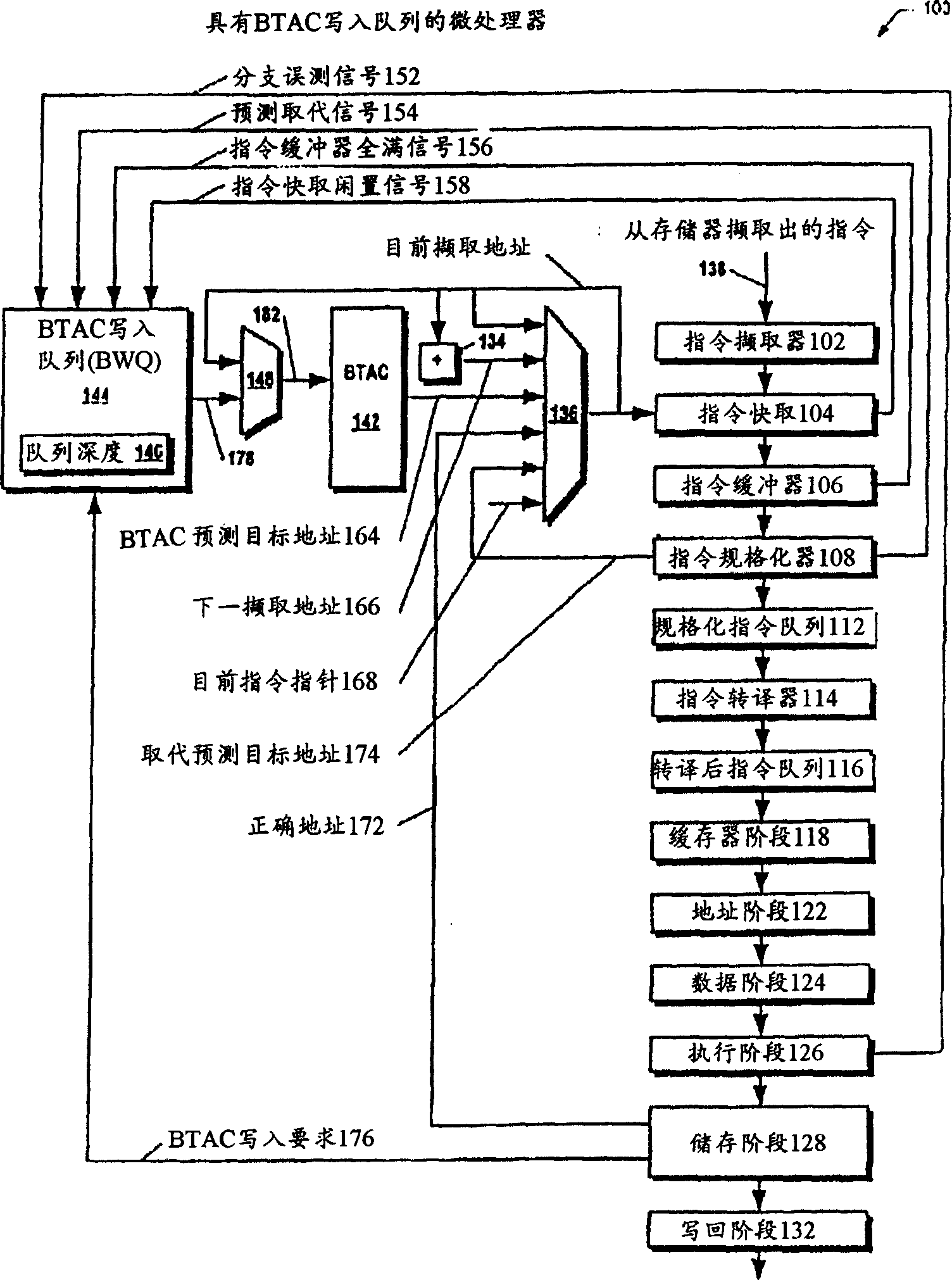

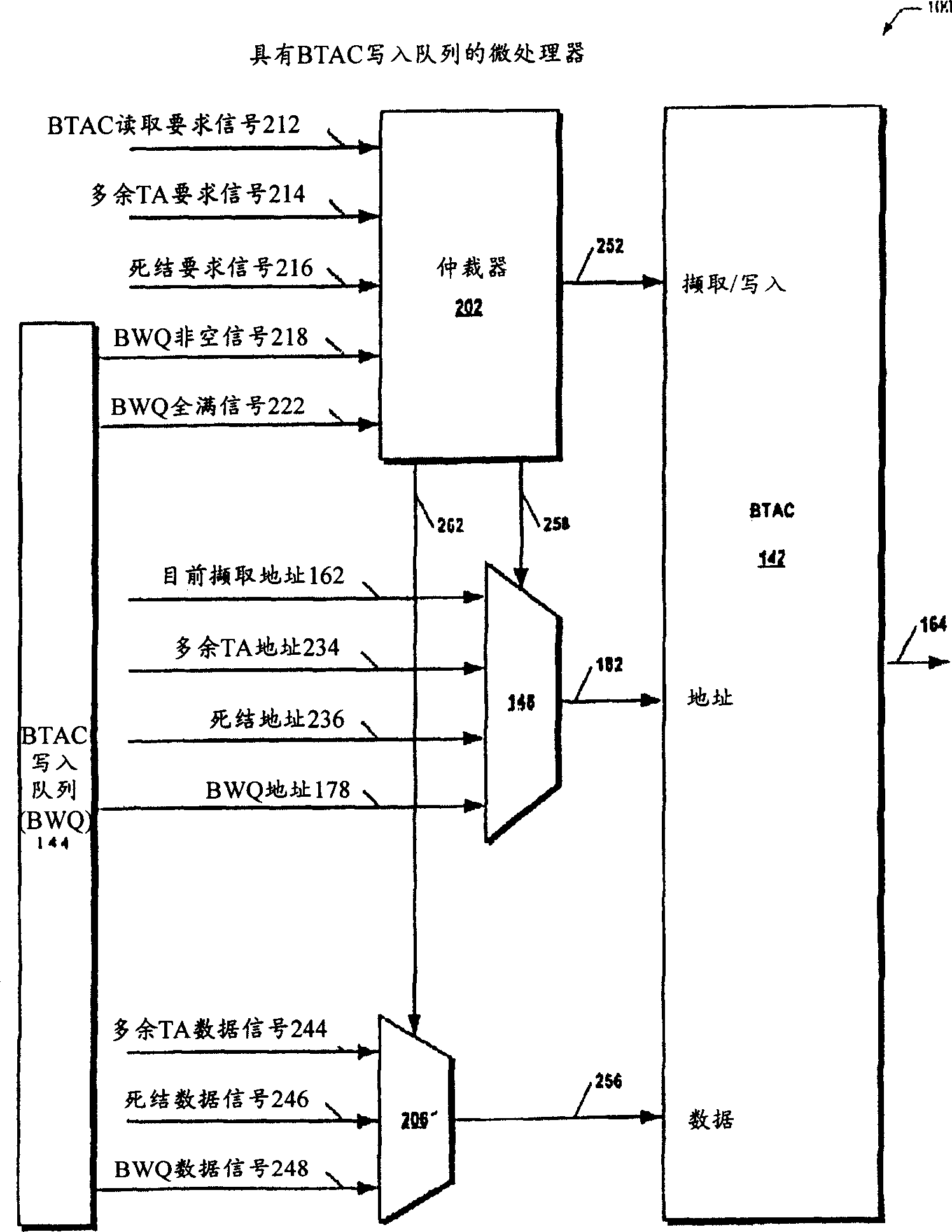

Microprocessor with branch target address cache update queue

ActiveUS7165168B2Improve efficiencyReduce in quantityMemory adressing/allocation/relocationDigital computer detailsRelevant informationParallel computing

A microprocessor with a write queue for a branch target address cache (BTAC) is disclosed. The BTAC is read in parallel with an instruction cache in order to predict a target address of a branch instruction in the accessed cache line. In one embodiment, the BTAC is single-ported; hence, the single port must be shared for reading and writing. When the BTAC needs updating, such as when a branch target address is resolved, the microprocessor stores the branch target address and related information in the write queue. Thus, the write queue potentially enables updating of the BTAC to be delayed until the BTAC is not being read, such as when the instruction cache is idle, a misprediction by the BTAC is being corrected, or a prediction by the BTAC is being overridden. If the write queue becomes full, then it updates the BTAC anyway.

Owner:IP FIRST

Methods and apparatus for proactive branch target address cache management

InactiveUS20120042155A1Likelihood of conflictReduce probabilityDigital computer detailsNext instruction address formationBranch target address cachePrediction system

A multiple stage branch prediction system includes a branch target address cache (BTAC) and a branch predictor circuit. The BTAC is configured to store a BTAC entry. The branch predictor circuit is configured to store state information. The branch predictor circuit utilizes the state information to predict the direction of a branch instruction and to manage the BTAC entry based on modified state information prior to resolution of the branch instruction.

Owner:QUALCOMM INC

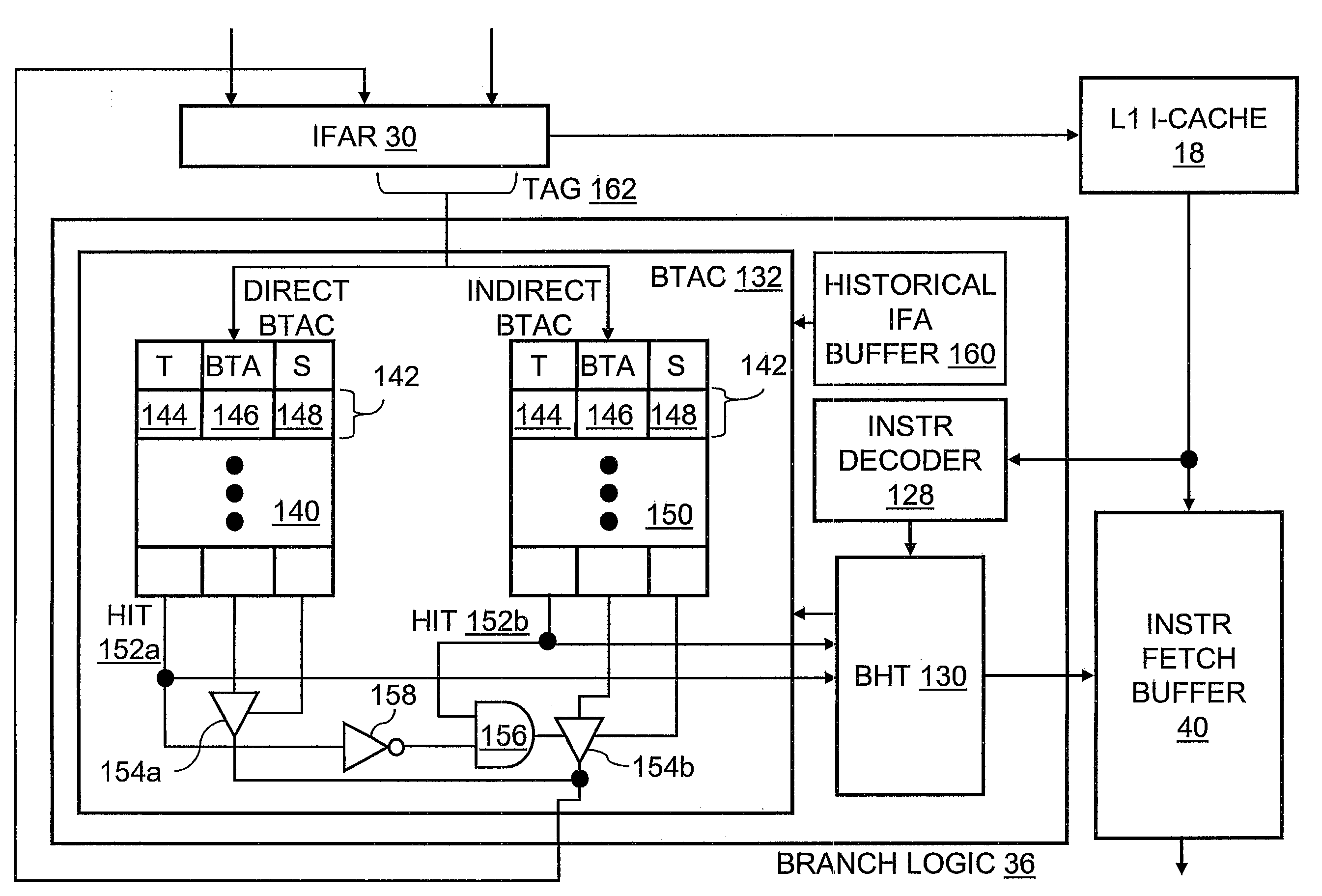

Data processing system, processor and method of data processing having branch target address cache storing direct predictions

InactiveUS20090198981A1Digital computer detailsSpecific program execution arrangementsData processing systemDirect entry

In at least one embodiment, a processor includes at least one execution unit and instruction sequencing logic that fetches instructions for execution by the execution unit. The instruction sequencing logic includes branch logic that outputs predicted branch target addresses for use as instruction fetch addresses. The branch logic includes a branch target address cache (BTAC) having at least one direct entry providing storage for a direct branch target address prediction associating a first instruction fetch address with a branch target address to be used as a second instruction fetch address immediately after the first instruction fetch address and at least one indirect entry providing storage for an indirect branch target address prediction associating a third instruction fetch address with a branch target address to be used as a fourth instruction fetch address subsequent to both the third instruction fetch address and an intervening fifth instruction fetch address.

Owner:IBM CORP

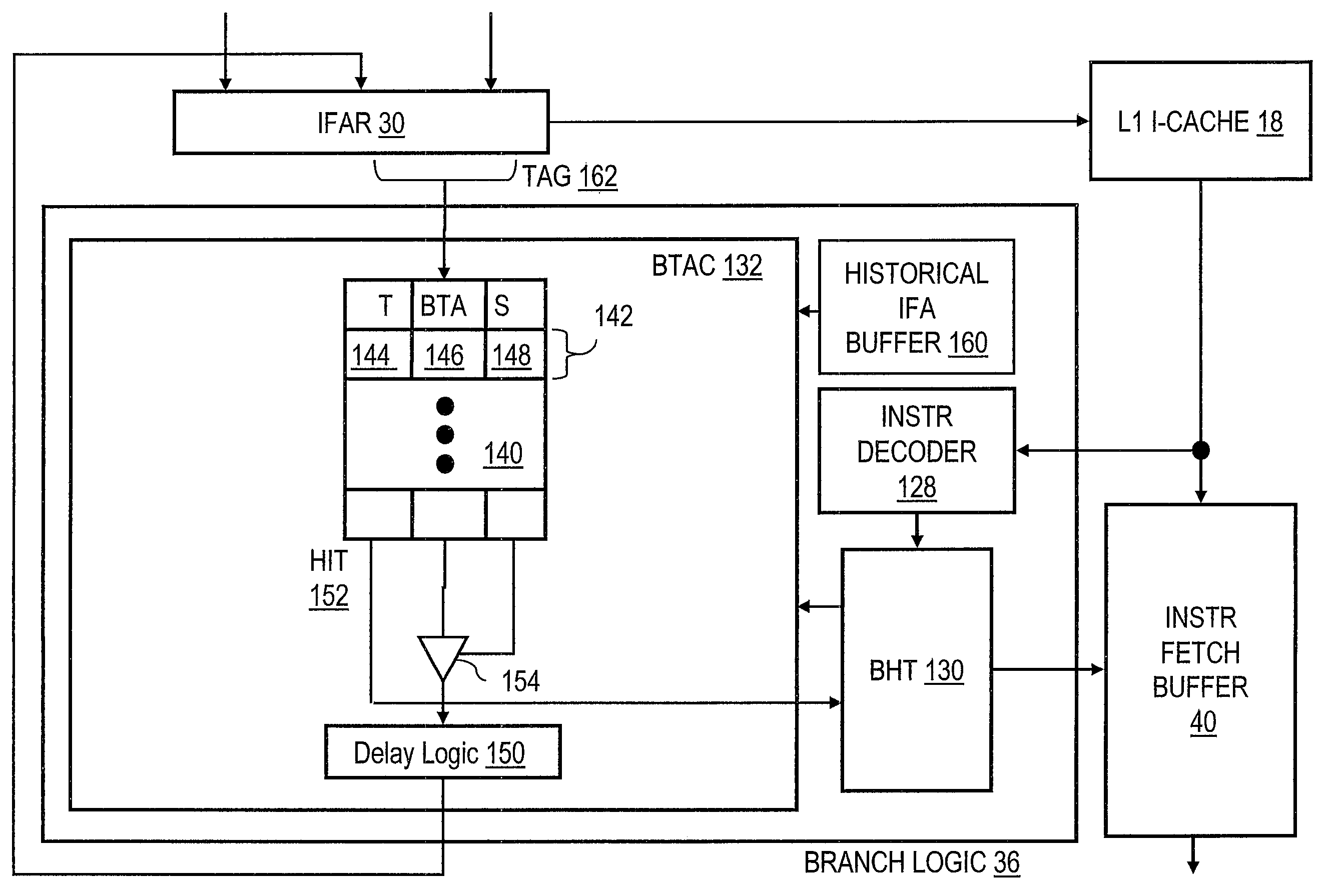

Branch target address cache selectively applying a delayed hit

InactiveUS7877586B2Digital computer detailsNext instruction address formationBranch target address cacheParallel computing

In at least one embodiment, a processor includes at least one execution unit that executes instructions and instruction sequencing logic, coupled to the at least one execution unit, that fetches instructions from a memory system for execution by the at least one execution unit. The instruction sequencing logic including branch target address prediction circuitry that stores a branch target address prediction associating a first instruction fetch address with a branch target address to be used as a second instruction fetch address. The branch target address prediction circuitry includes delay logic that, in response to at least a tag portion of a third instruction fetch address matching the first instruction fetch address, delays access to the memory system utilizing the second instruction fetch address if no branch target address prediction was made in an immediately previous cycle of operation.

Owner:INT BUSINESS MASCH CORP

Data processing system, processor and method of data processing having improved branch target address cache

InactiveUS20090049286A1Enhanced branch target address cacheDigital computer detailsConcurrent instruction executionData processing systemBranch target address cache

A processor includes an execution unit and instruction sequencing logic that fetches instructions from a memory system for execution. The instruction sequencing logic includes branch logic that outputs predicted branch target addresses for use as instruction fetch addresses. The branch logic includes a level one branch target address cache (BTAC) and a level two BTAC each having a respective plurality of entries each associating at least a tag with a predicted branch target address. The branch logic accesses the level one and level two BTACs in parallel with a tag portion of a first instruction fetch address to obtain a first predicted branch target address from the level one BTAC for use as a second instruction fetch address in a first processor clock cycle and a second predicted branch target address from the level two BTAC for use as a third instruction fetch address in a later second processor clock cycle.

Owner:IBM CORP

Apparatus and method for densely packing a branch instruction predicted by a branch target address cache and associated target instructions into a byte-wide instruction buffer

InactiveUS7162619B2Alleviate Timing ConstraintsMemory adressing/allocation/relocationDigital computer detailsProcessor registerBranch target address cache

A branch control apparatus in a microprocessor. A register receives a first cache line containing a branch instruction from an instruction cache in response to a fetch address. The fetch address hits in a BTAC that provides a target address of the branch instruction. The BTAC also provides an offset of the instruction following the branch instruction. The instructions following the branch instruction are invalidated based on the offset. Muxing logic packs only the valid instructions into a byte-wide instruction buffer that is directly coupled to instruction format logic. The instruction cache provides a second cache line containing the target instructions to the register in response to the target address. The instructions preceding the target instructions are invalidated based on the lower bits of the target address. The muxing logic packs only the valid target instructions into the instruction buffer immediately adjacent to the branch instruction bytes.

Owner:IP FIRST

Apparatus and method for efficiently updating branch target address cache

ActiveCN1542625AReduce areaImprove efficiencyMemory adressing/allocation/relocationConcurrent instruction executionRelevant informationBranch target address cache

A microprocessor with a write queue for a branch target address cache (BTAC) is disclosed. The BTAC is read in parallel with an instruction cache in order to predict a target address of a branch instruction in the accessed cache line. In one embodiment, the BTAC is single-ported; hence, the single port must be shared for reading and writing. When the BTAC needs updating, such as when a branch target address is resolved, the microprocessor stores the branch target address and related information in the write queue. Thus, the write queue potentially enables updating of the BTAC to be delayed until the BTAC is not being read, such as when the instruction cache is idle, a misprediction by the BTAC is being corrected, or a prediction by the BTAC is being overridden. If the write queue becomes full, then it updates the BTAC anyway.

Owner:IP FIRST

Efficient branch target address cache entry replacement

ActiveUS8832418B2Digital computer detailsConcurrent instruction executionBranch target address cacheParallel computing

A microprocessor includes a branch target address cache (BTAC), each entry thereof configured to store branch prediction information for at most N branch instructions. An execution unit executes a branch instruction previously fetched in a fetch quantum. Update logic determines whether the BTAC is already storing information for N branch instructions within the fetch quantum (N is at least two), updates the BTAC for the branch instruction if the BTAC is not already storing information for N branch instructions, determines whether a type of the branch instruction has a higher replacement priority than a type of the N branch instructions if the BTAC is already storing information for N branch instructions, and updates the BTAC for the branch instruction if the type of the branch instruction has a higher replacement priority than the type of the N branch instructions already stored in the BTAC.

Owner:VIA TECH INC

Block-based branch target address cache

InactiveCN101438237AMultiprogramming arrangementsConcurrent instruction executionBranch target address cacheParallel computing

A Branch Target Address Cache (BTAC) stores a plurality of entries, each BTAC entry associated with a block of two or more instructions that includes at least one branch instruction having been evaluated taken. The BTAC entry includes an indicator of which instruction within the associated block is a taken branch instruction. The BTAC entry also includes the Branch Target Address (BTA) of the taken branch. The block size may, but does not necessarily, correspond to the number of instructions per instruction cache line.

Owner:QUALCOMM INC