Block-based branch target address cache

A technology of branch target address and high-speed buffering, which is applied in the field of branch target address cache memory, and can solve the problem of wasting BTAC memory units, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

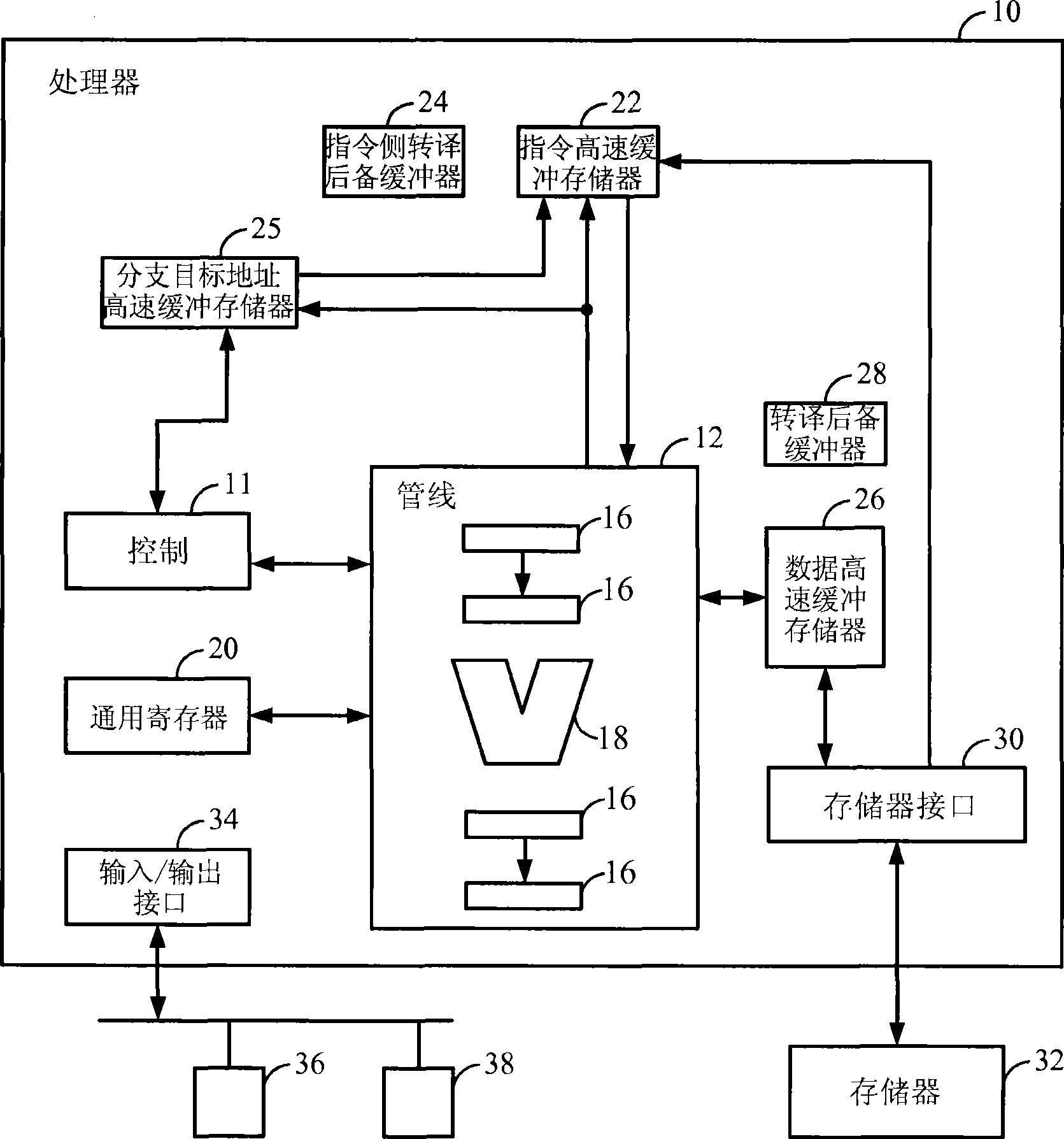

[0016] figure 1 A functional block diagram of processor 10 is depicted. The processor 10 executes instructions in the instruction execution pipeline 12 according to the control logic 11 . In some embodiments, pipeline 12 may be a superscalar design with multiple parallel pipelines. Pipeline 12 includes various registers or latches 16 and one or more arithmetic logic units (ALUs) 18 organized into several pipeline stages. A general purpose register (GPR) file 20 provides registers that make up the top level of the memory hierarchy.

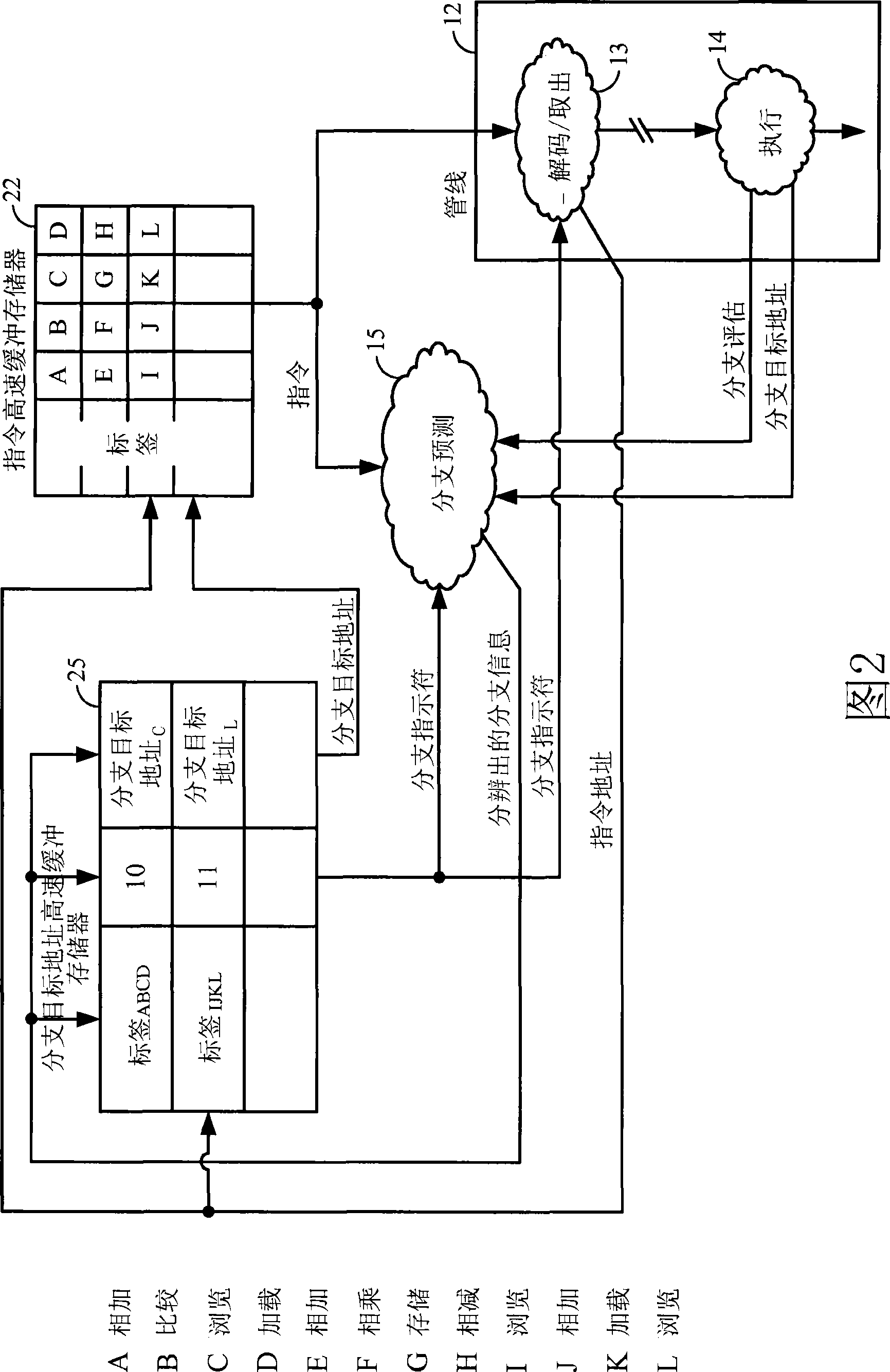

[0017] The pipeline 12 fetches instructions from an instruction cache (I-cache) 22 , where memory address translation and grants are managed by an instruction-side translation lookaside buffer (ITLB) 24 . In parallel, pipeline 12 provides the truncated instruction address to block-based branch target address cache (BTAC) 25 . If the truncated address hits in BTAC 25, BTAC 25 may provide a branch target address (BTA) to I-cache 22 to begin fetch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More