Method and apparatus for accelerating processor to read and write scratch memory

A technology for accelerating processors and temporary registers, applied in program control devices, electrical digital data processing, instruments, etc., can solve the problems of processor development dilemma, inability to meet reading and writing requirements, and resource consumption of built-in ICE.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

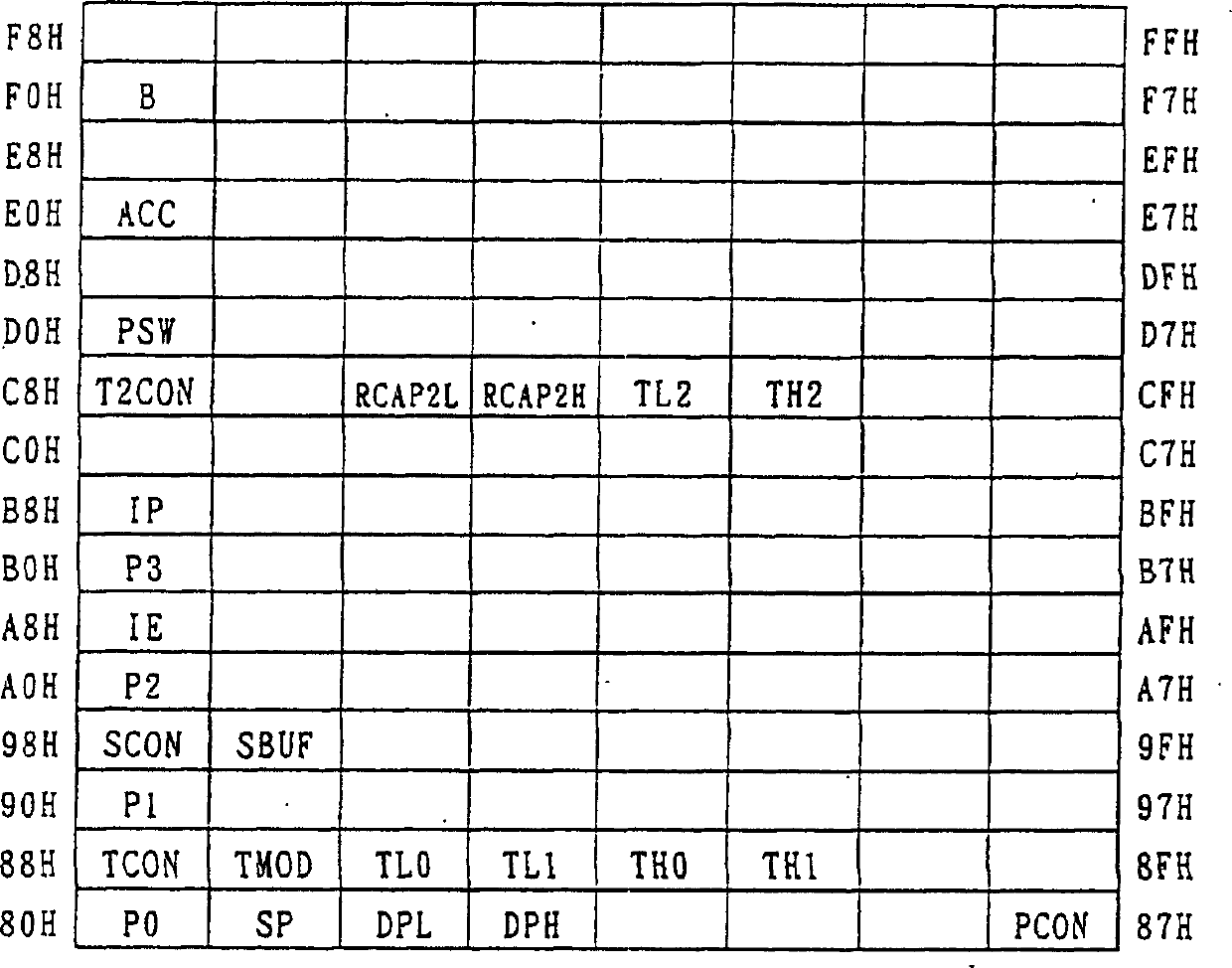

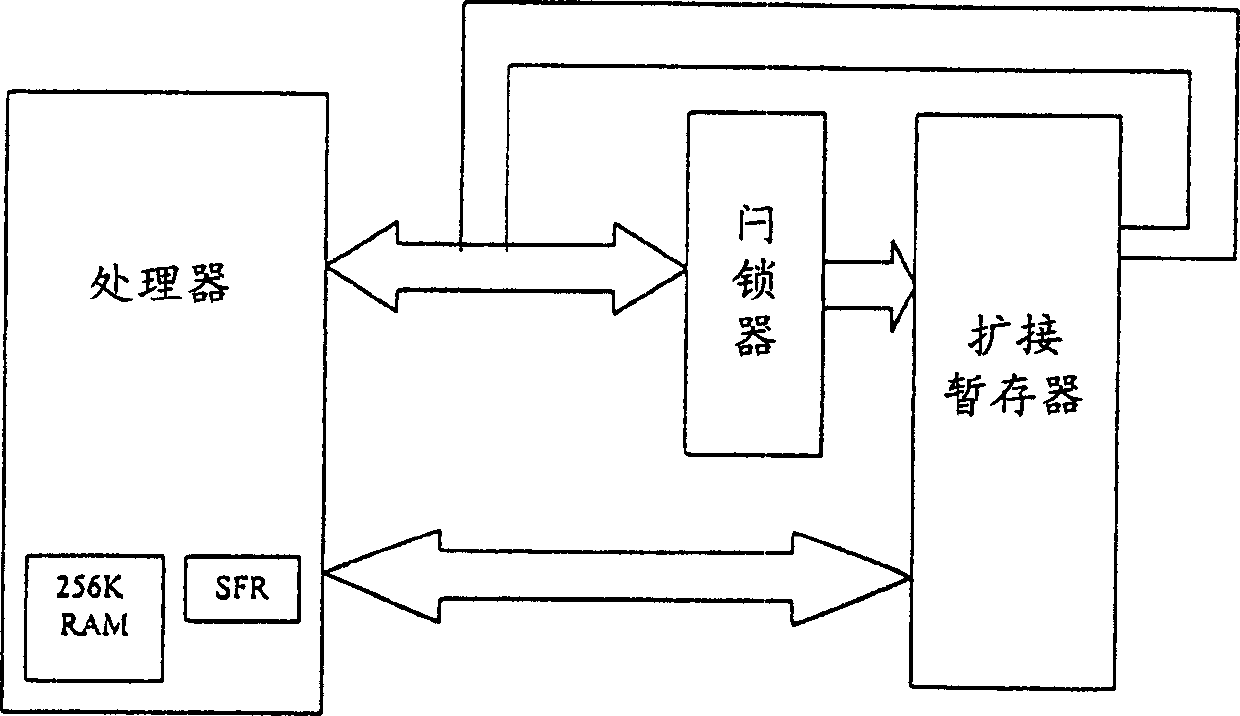

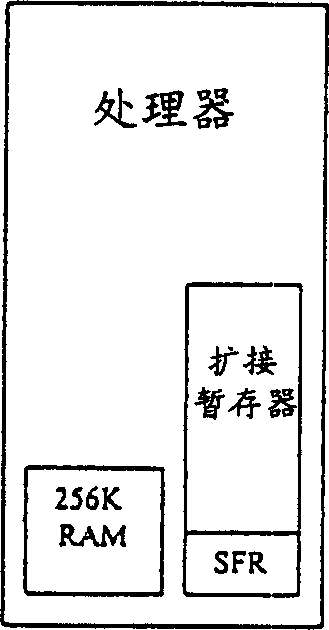

[0021] Firstly, in the present invention, the processor is externally connected with an expansion memory to establish an expansion temporary register. In this embodiment, an 8051 processor is used as an example. The address of the extended temporary register in the external memory is mapped to the idle address of the special function register (SFR) built in the processor by means of memory mapping (MEMORY MAPPING).

[0022] The SFR is a 128-byte (Bytes) (80H~FFH) memory area that can be directly addressed (see Figure 1). In addition to its own multiple sets of temporary registers, there are still many idle addresses. Therefore, the present invention maps the address of the expansion temporary register to the idle address of the SFR, so that in the normal operation mode, the expansion temporary register is simulated as an internal temporary register, and then the internal data transfer command can be used to read and write the expansion register. Compared with the method of rea...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More