Non-volatile storage device

A technology of non-volatile storage and storage devices, which is applied in the field of non-volatile storage devices and can solve problems such as data destruction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail with reference to the accompanying drawings.

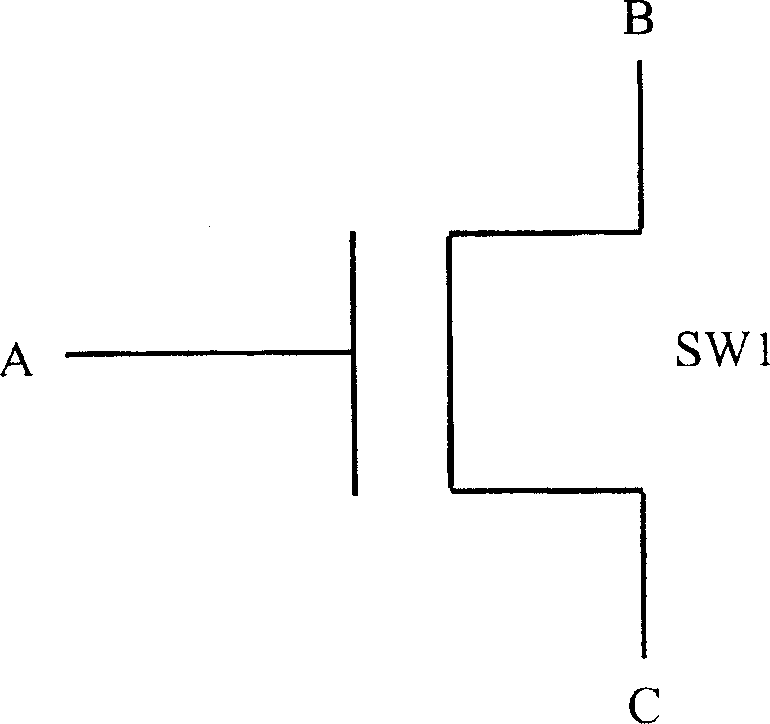

[0029] Figure 4a A circuit diagram showing a nonvolatile memory device used as a nonvolatile logic switch according to an embodiment of the present invention.

[0030] In one embodiment, the non-volatile memory device includes a write / read controller 20, resistive memory devices R1 and R2, and a logic switch SW2.

[0031] The write / read controller 20 selectively outputs a write / read signal in response to a write control signal WRC2 input to a gate of an NMOS transistor N5 and a write control signal WRC3 input to a gate of a PMOS transistor P3. Control signal WRC1. The phase of the write control signal WRC2 is opposite to that of the write control signal WRC3.

[0032] The resistive memory device R1 is connected between a node D and a node F. The resistive memory device R2 is connected between a node E and a node F. As shown in FIG. The node F is connected to the gate o...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap