Device and method for preventing stagnation of microprocessor pipeline

A microprocessor and pipeline technology, applied in the field of microelectronics, can solve problems such as large access delays

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

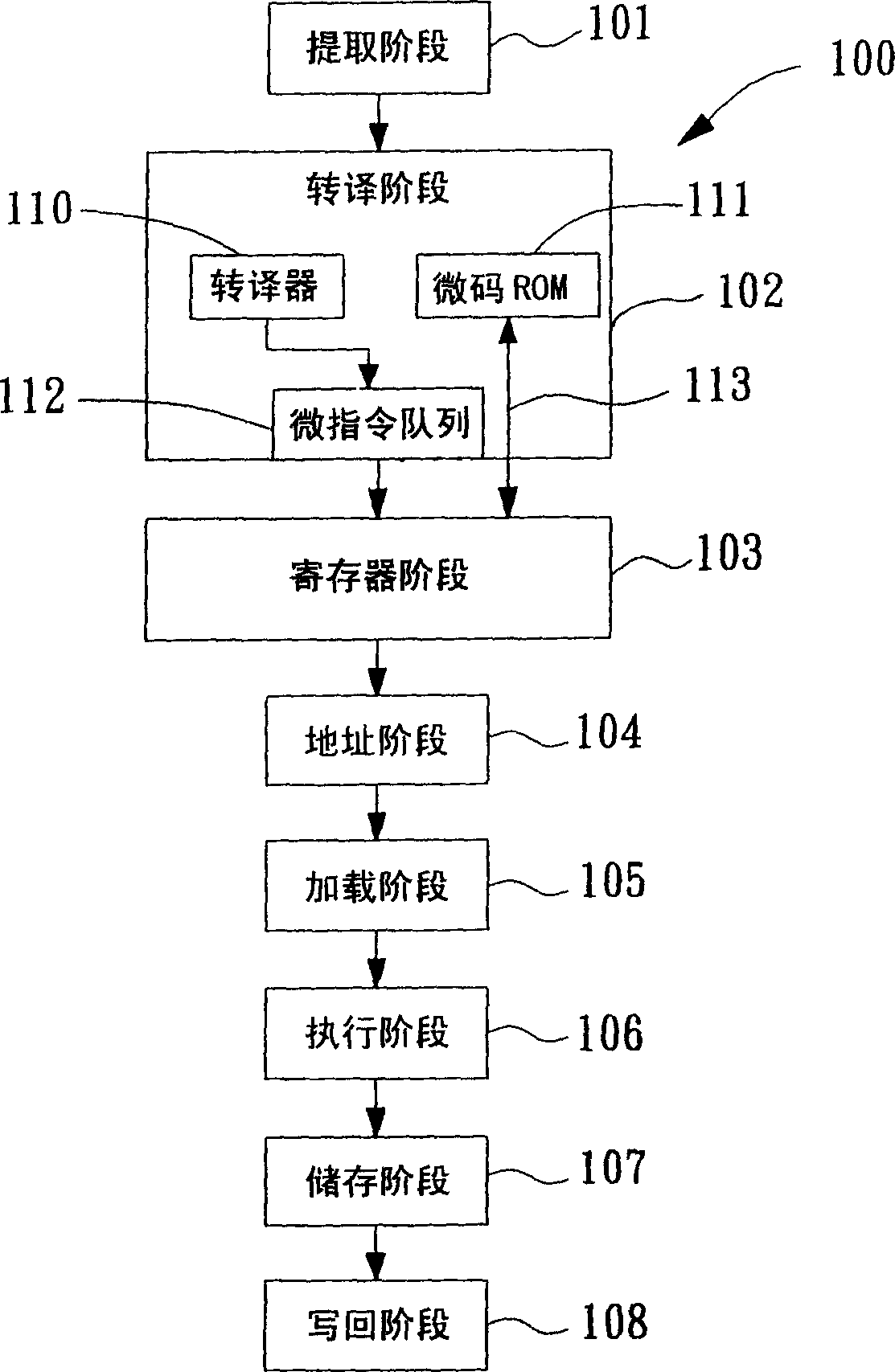

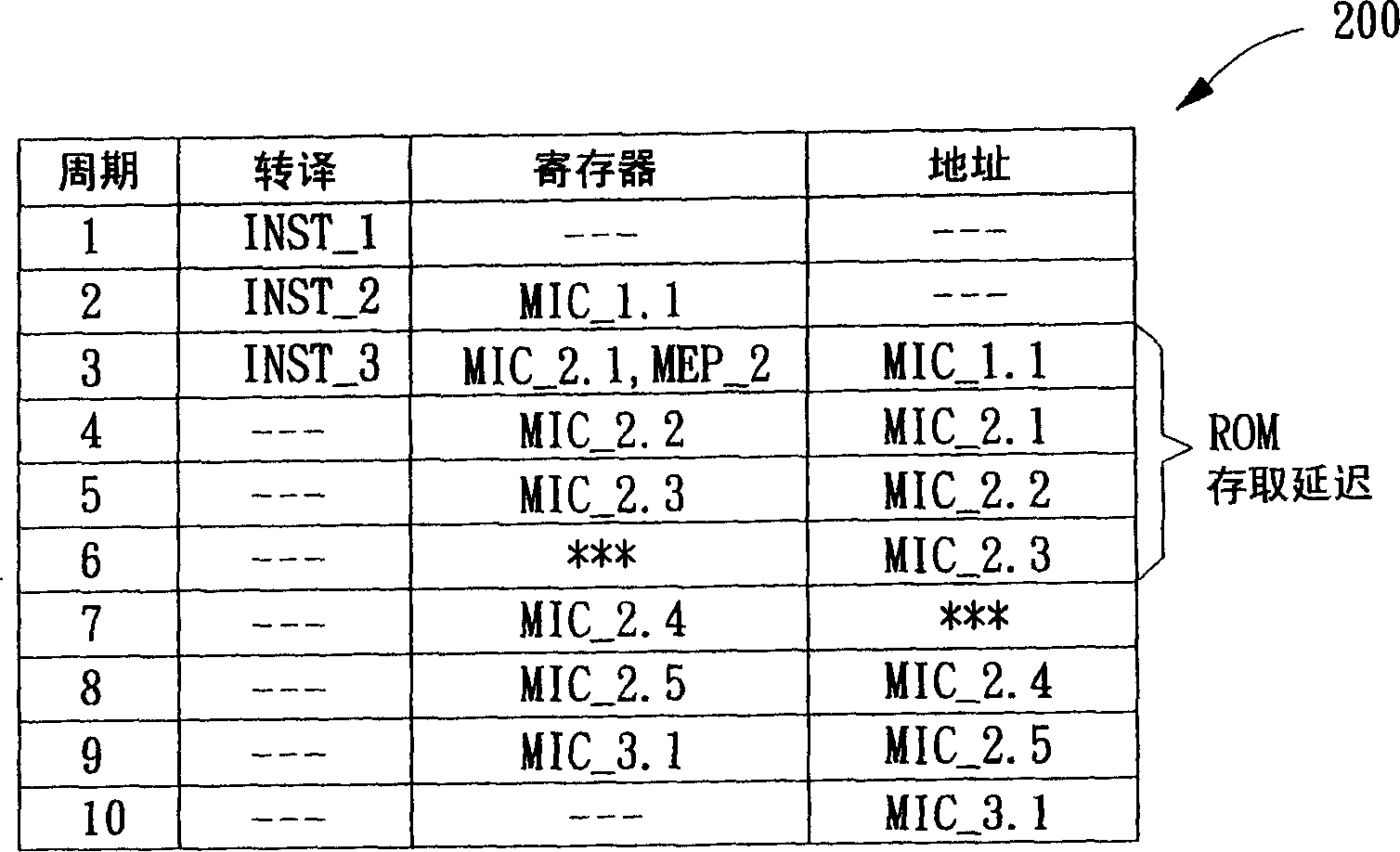

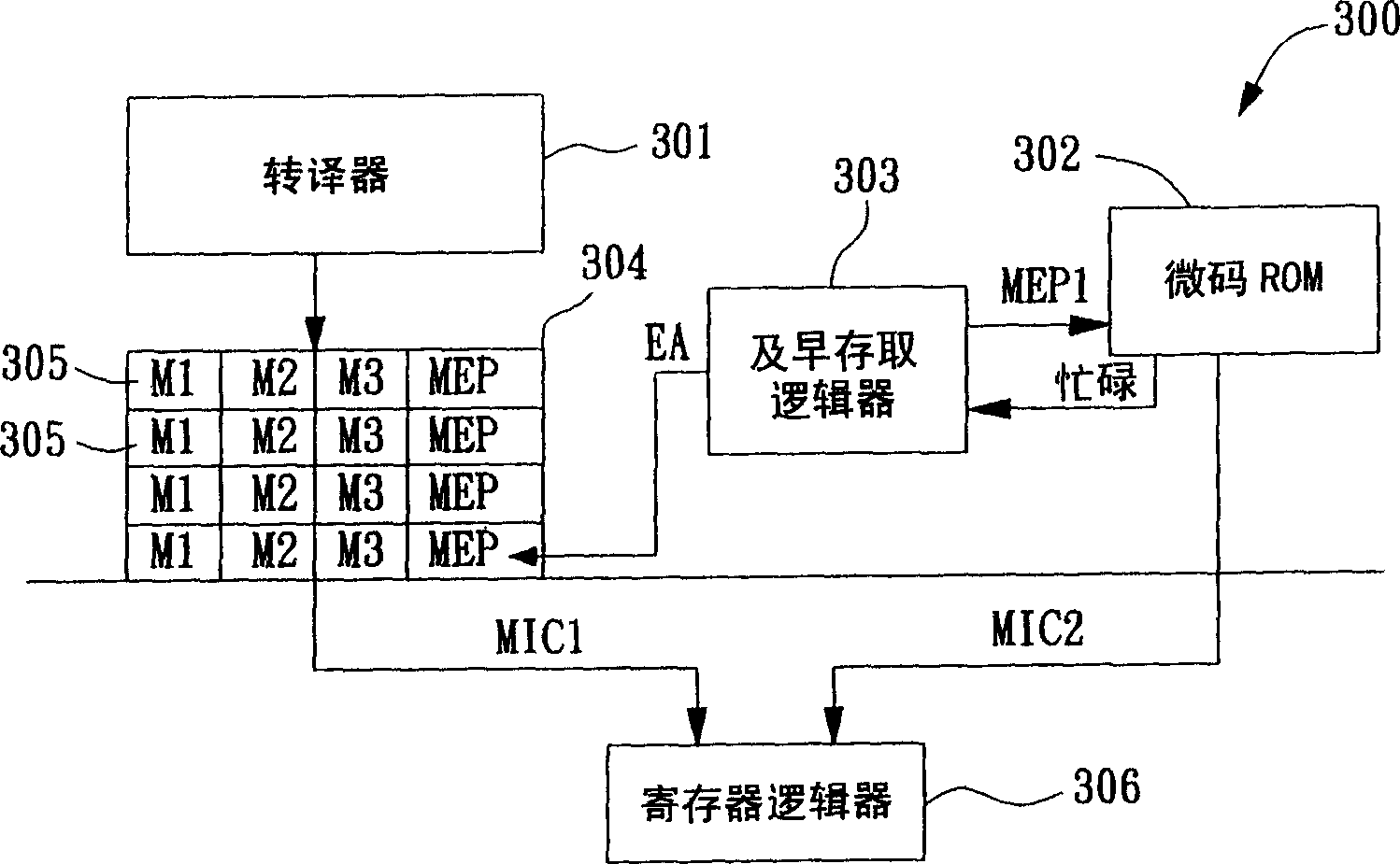

[0034] In view of the above background discussion of instruction translation and corresponding techniques used in current pipeline microprocessors for generating microinstruction sequences, a more detailed discussion of the problems addressed by the present invention will be presented in conjunction with figure 1 , figure 2 to proceed. Immediately thereafter, the discussion of the present invention will cooperate with Figure 3 to Figure 5 And manifested. The present invention can effectively absorb the delay caused by the microcode ROM access delay when the verification logic for accessing the corresponding microcode ROM sends the microinstruction before the corresponding microcode entry point is sent to the next pipeline stage. caused pipeline stagnation.

[0035] refer to figure 1 , the block diagram shown is a block diagram illustrating stages of an embodiment within a current microprocessor. Microprocessor 100 includes eight example stages 101 - 108 : fetch stage 10...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More