Microcontroller instruction set

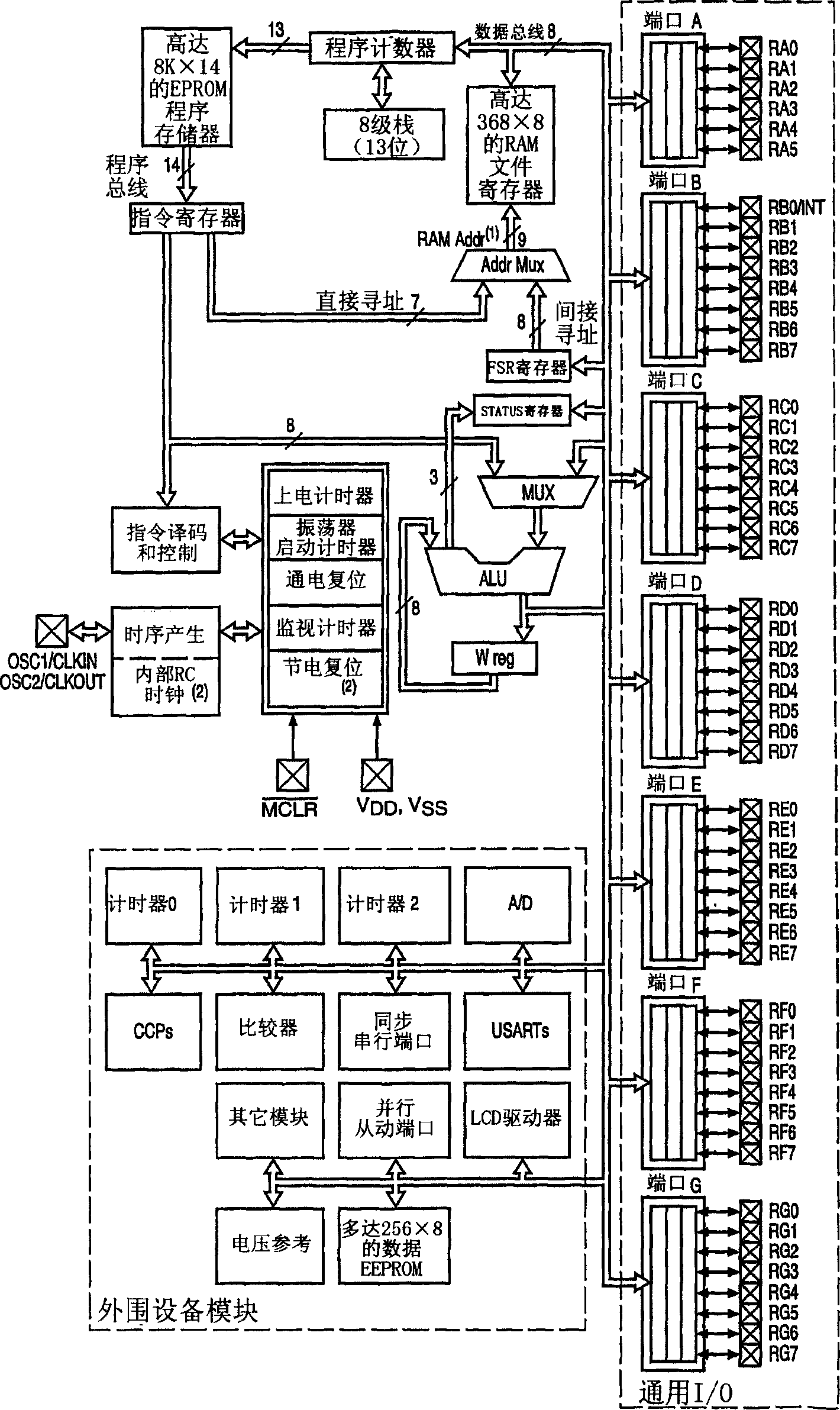

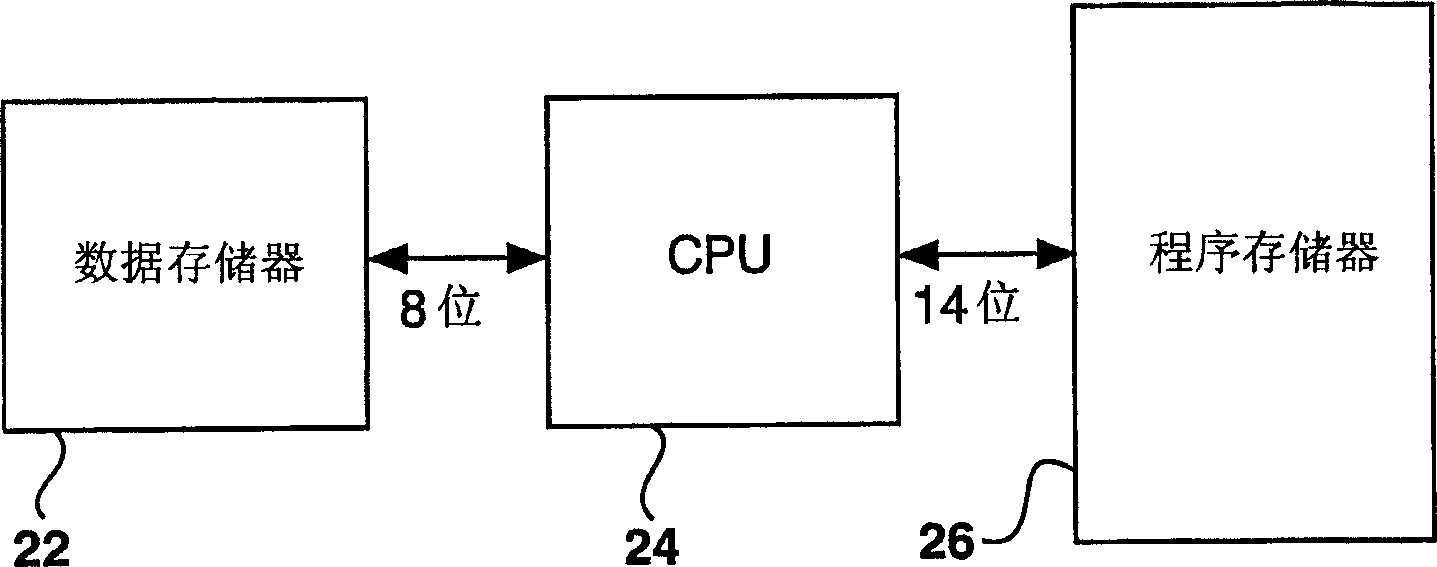

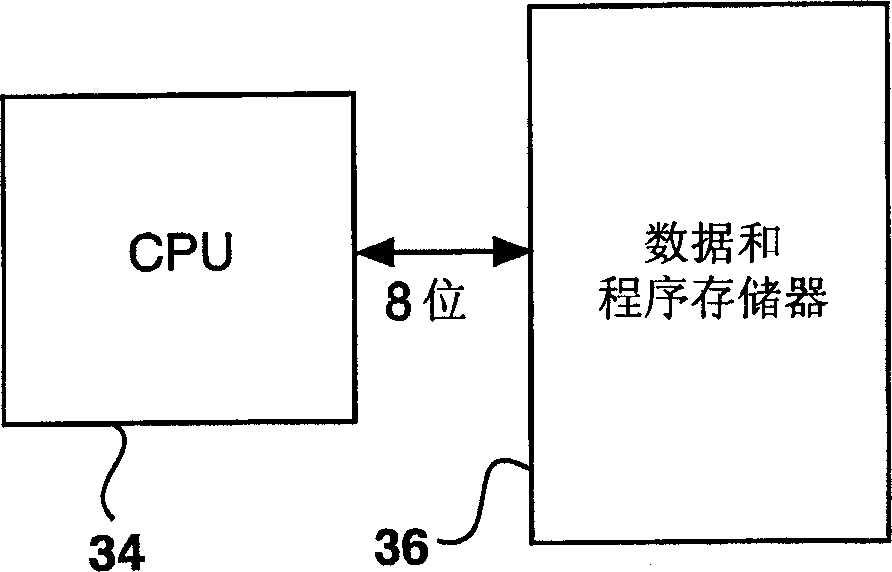

A microcontroller and instruction set technology, applied in the field of operation code instructions, can solve problems such as unsimulated multiple modules, compiler errors, address space linearization, etc., and achieve the effect of simple and effective programming and shortening the learning curve

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

[0641] Example 1: DAW

[0642] Before executing the command:

[0643] W = 0xA5

[0644] c = 0

[0645] DC = 0

[0646] After executing the command:

[0647] W = 0x05

[0648] c = 1

[0649] DC = 0

example 2

[0651] Before executing the command:

[0652] W = 0xCE

[0653] c = 0

[0654] DC = 0

[0655] After executing the command:

[0656] W = 0x34

[0657] c = 1

[0658] DECF

decrement f

grammar:

[label] DECF f, d, a

Operands:

0≤f≤255

d∈[0.1]

a∈[0,1]

operate:

(f)-1→dest

Affected states:

C, DC, N, OV, Z

encoding:

0000

01da

ffff

ffff

illustrate:

Decrements register "f". If "d" is 0, then

Then store the result in W. If "d" is 1,

Then store the result back into register "f" (default

of). If "a" is 0, then the virtual

memory area, thus overwriting the BSR value. if "a"

=1, then the storage area will be selected according to the BSR value (default

recognized).

Character:

1

cycle:

1

Q cycle activities:

Q1

Q2

Q3

Q4

decoding

read register "f" ...

example 3

[0930] Example 3: SDBFWB REG, 1, 0

[0931] Before executing the command:

[0932] REG = 1

[0933] W = 2

[0934] C = 0

[0935] After executing the command:

[0936] REG = 0

[0937] W = 2

[0938] C = 1

[0939] Z = 1; the result is 0

[0940] SUBLW

Literal minus W

grammar:

[label] SUBLW k

Operands:

0≤k≤255

operate:

k-(W)→W

Affected states:

N, OV, C, DC, Z

encoding:

0000

1000

kkkk

kkkk

illustrate:

Subtracts W from the 8-bit literal "k". Will

The result is placed in W.

Character:

1

cycle:

1

Q cycle activities:

Q1

Q2

Q3

Q4

decoding

read the literal "k"

write to W

[0941] Example 1: SUBLW 0x02

[0942] Before executing the command:

[0943] W = 1

[0944] C=?

[0945] After executing the command:

[0946] W = 1

[094...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More