System and method for encoding packet header to enable higher bandwidth efficiency across PCIe links

一种数据包、完成数据包的技术,应用在数字传输系统、传输系统、数据交换网络等方向,能够解决消耗计算机系统总线带宽总线吞吐率等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

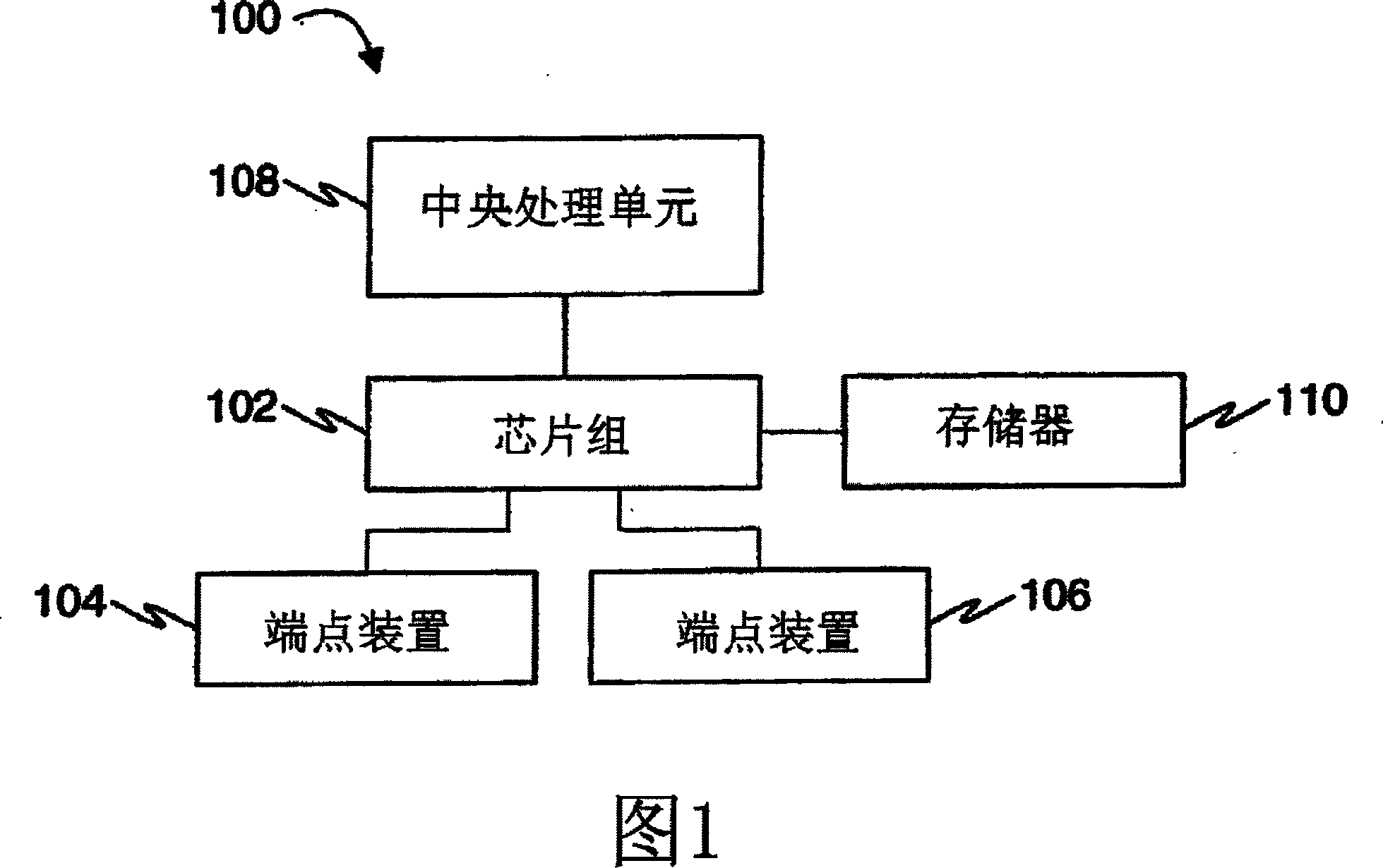

[0031] Embodiments of the invention provide methods and systems for communication in computer systems employing peripheral component interconnect express (PCIe) links. PCIe is a general-purpose input / output (I / O) interconnect used for communication between two or more devices within a computer. The devices may include one or more endpoint devices and a chipset.

[0032] FIG. 1 is a block diagram illustrating an environment 100 (which is exemplary, such as a computer system, within which embodiments of the invention may function). Environment 100 includes a chipset 102 , an endpoint device 104 and an endpoint device 106 . Those skilled in the art will readily appreciate that the number of endpoint devices does not limit the invention in any way.

[0033] Chipset 102 is a root complex, such as a chipset, that includes chips commonly known as Northbridge and Southbridge in communication with at least one of Endpoint Device 104 and Endpoint Device 106, a Central Processing Unit ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More