Method and its circuit for realizing multiplication capacitor

An implementation method and circuit technology, applied in the field of multiplier capacitor implementation method and its circuit, can solve the problems of increasing system complexity, increasing system cost, reducing system reliability, etc., and achieve the effect of reducing cost and reducing chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

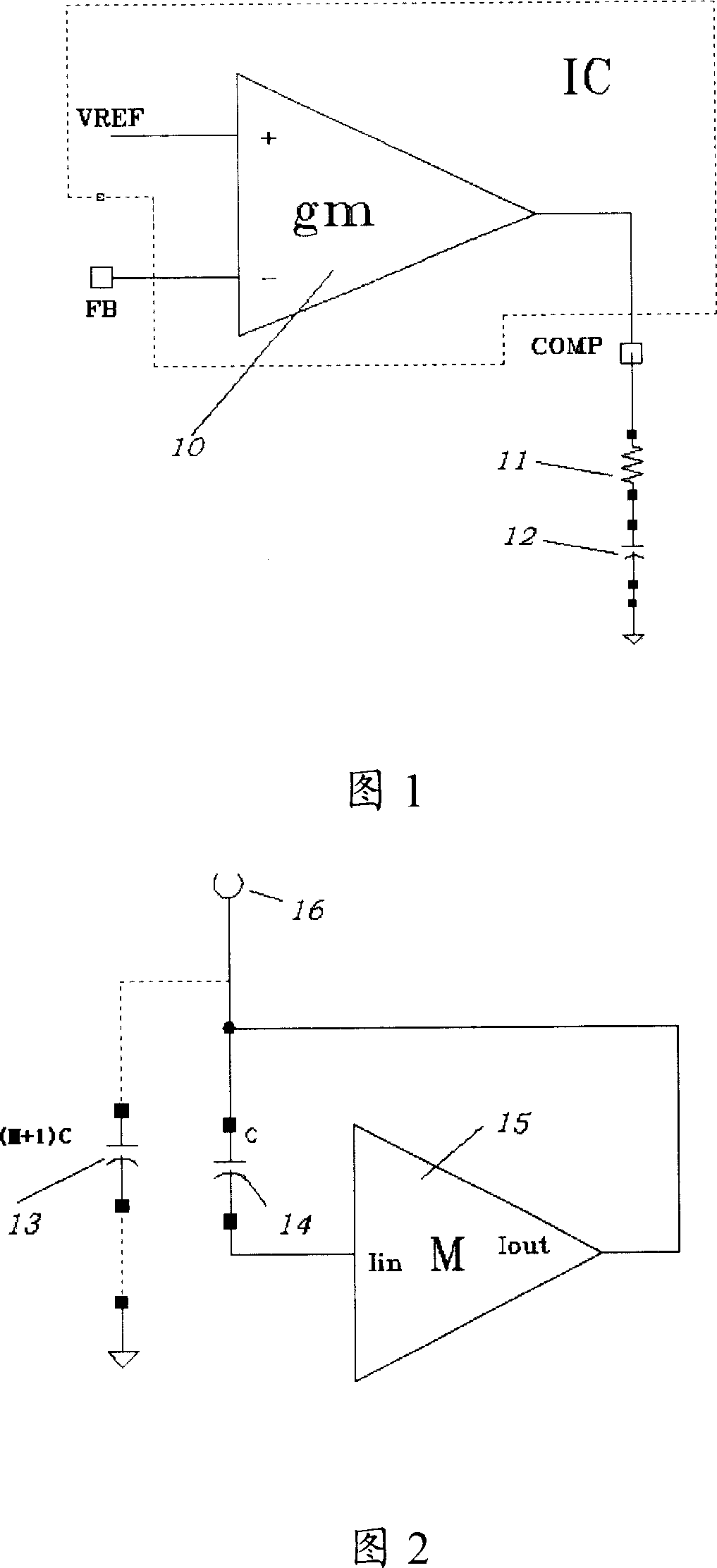

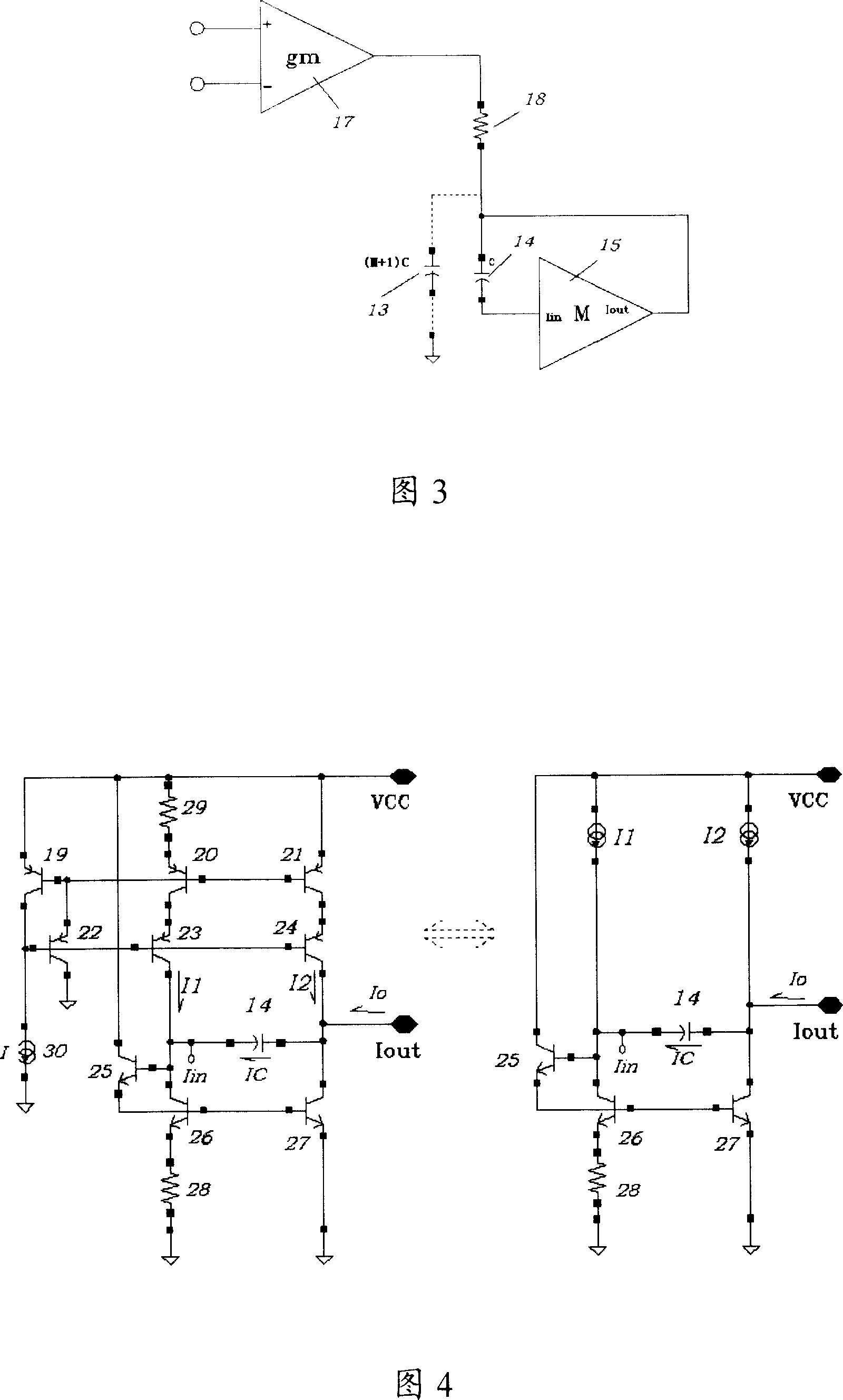

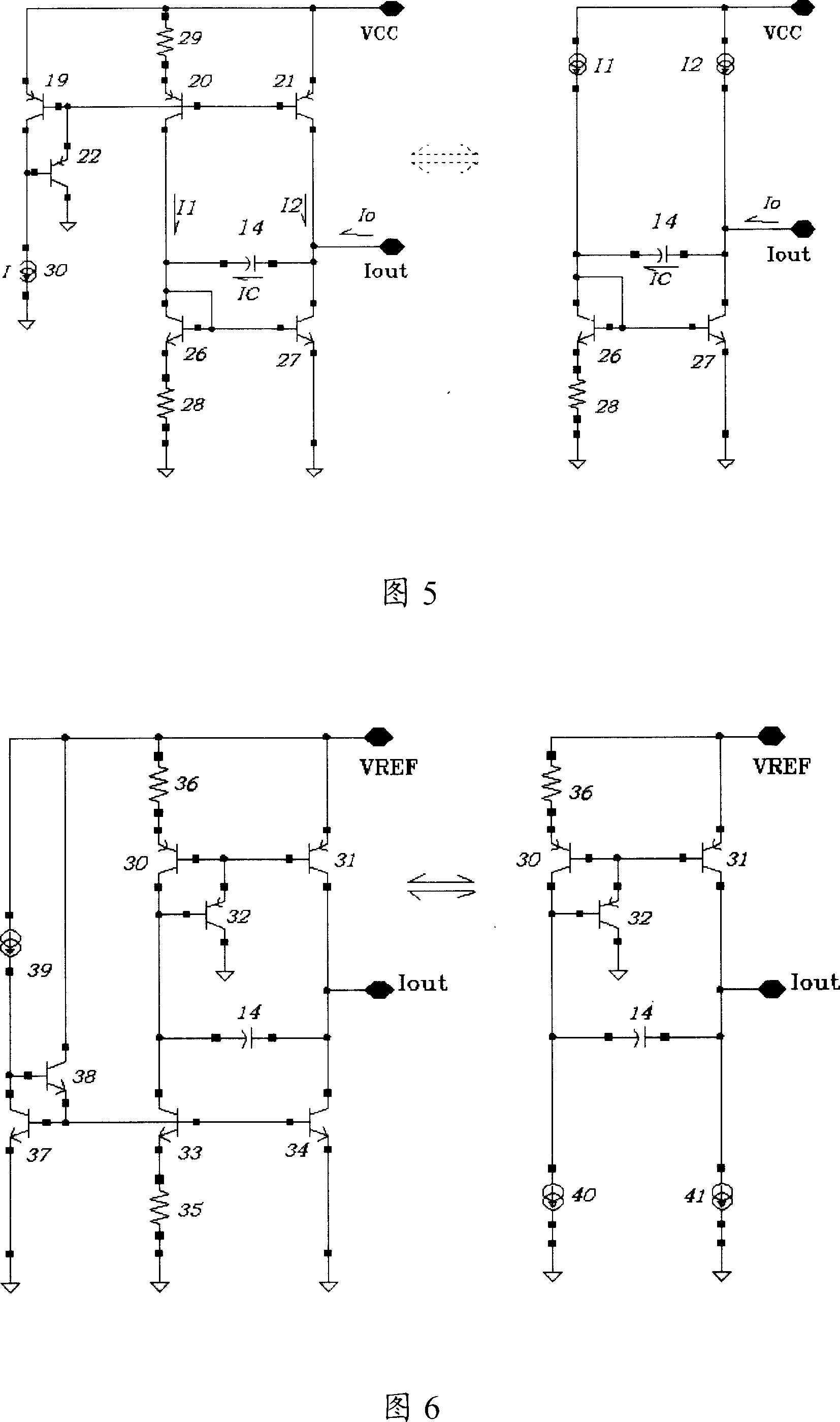

[0039] The invention mainly solves the relevant problem of how to integrate the capacitor into the integrated circuit as an integrated device. It is very difficult to integrate a capacitor with a large capacitance in an integrated circuit, because the size of the integrated capacitor is proportional to the chip area used to manufacture the capacitor, and an integrated 1nF physical capacitor needs to occupy about 1mm 2 chip area. However, many circuit functions require capacitors with relatively large capacitance values, and these capacitors with large capacitance values cannot be physically integrated into integrated circuits as real capacitors.

[0040] The present invention solves the above-mentioned problems by utilizing a capacitance multiplying circuit. The object of the present invention is to provide a method for realizing multiplied capacitance and its circuit, which multiplies the capacitance with smaller capacitance value to realize the equivalent capacitance with...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More