Memory interface for systems with multiple processors and one memory system

a memory system and interface technology, applied in the field of memory systems, can solve the problems of large amount of on-chip memory in most digital asics, not very scalable, and more expensive problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

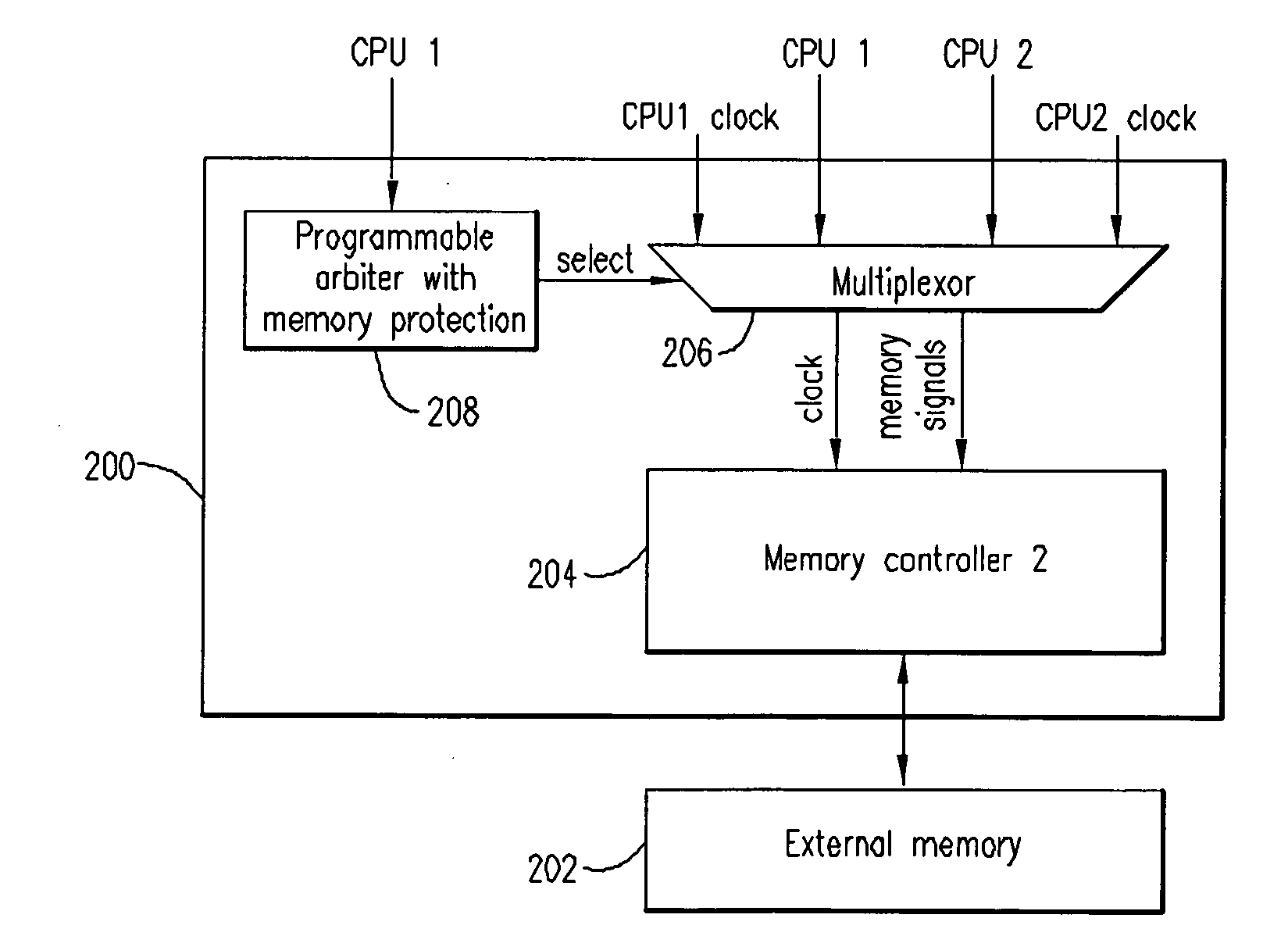

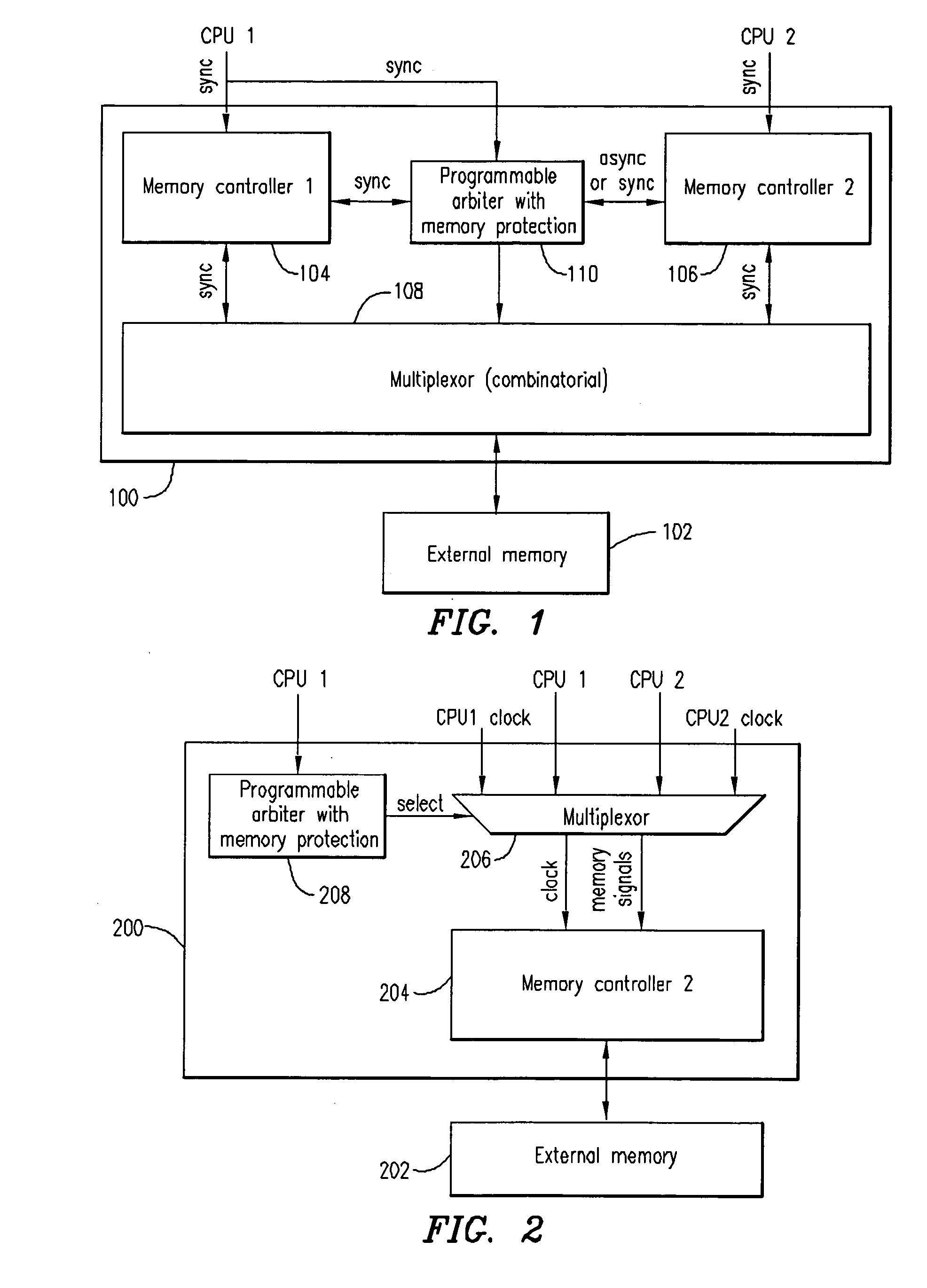

[0015] Following is a Detailed Description of Illustrative Embodiment(s) of the invention with reference to the drawings wherein the same reference labels are used for the same or similar elements. As used herein, the term “access”, when used in conjunction with the term “external memory”, means and refers to any memory operation, including, but not necessarily limited to, read operations, write operations, and refresh operations.

[0016] While asynchronous request-and-grant systems work reasonably well, improvements in several areas are desirable. For example, various handshakes that take place between the CPU and the memory interface can consume valuable bandwidth. In addition, it is difficult to predict the latency of the system with any accuracy for a given CPU because the memory access, once granted, is usually not interrupted until the CPU is finished. This unknown and potentially long wait time may cause problems for other CPUs, especially in real-time-oriented applications.

[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More