Three-level leadframe for no-lead packages

a leadframe and no-lead technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of high cost and no-lead package based on wire bonding technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The present invention is related to U.S. Pat. No. 6,072,230, issued on Jun. 6, 2000 (Carter et al., “Exposed Leadframe for Semiconductor Packages and Bend Forming Method of Fabrication”), and U.S. patent applications Ser. No. 09 / 900,080, filed on Jul. 6, 2001 (Abbott et al., “Preplating of Semiconductor Small Outline No-Lead Leadframes”), and Ser. No. 10 / 346,899, filed on Jan. 17, 2003 (Abbott, “Semiconductor Device with Double Nickel-Plated Leadframe”).

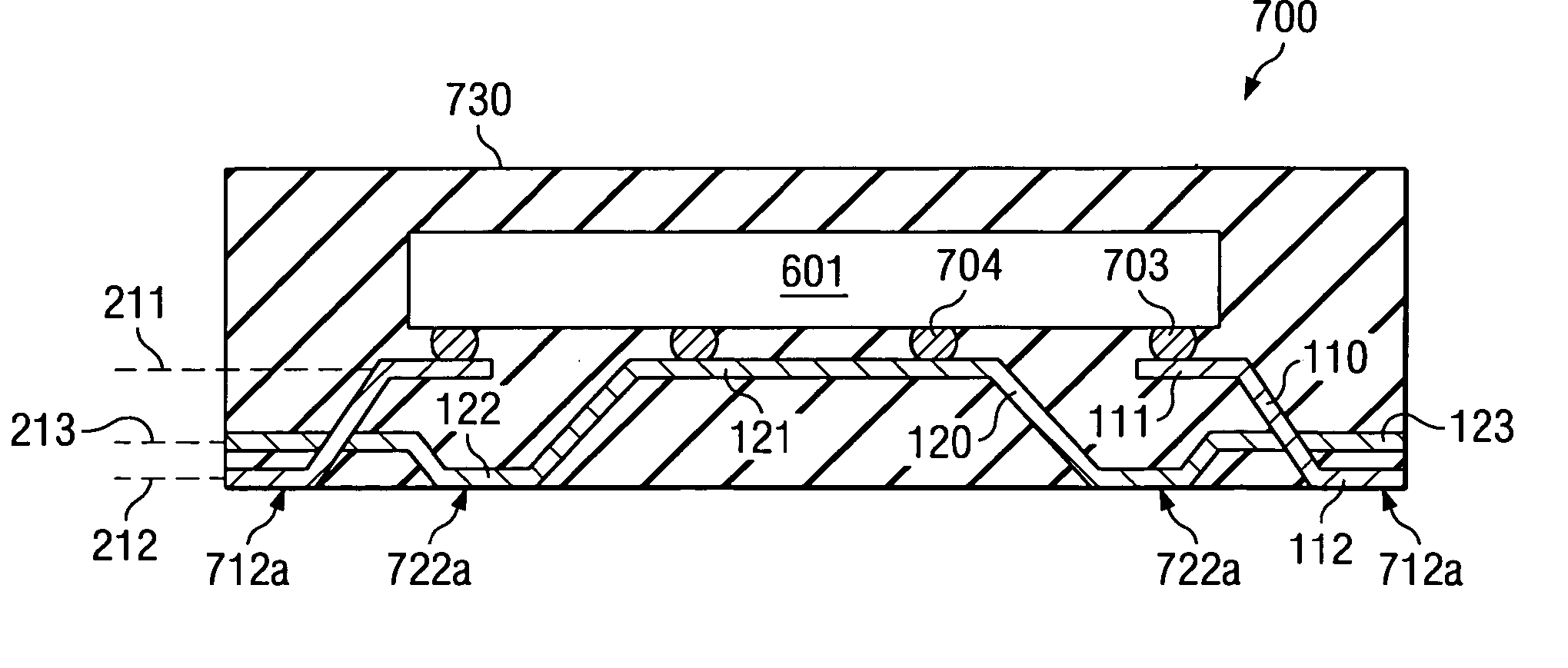

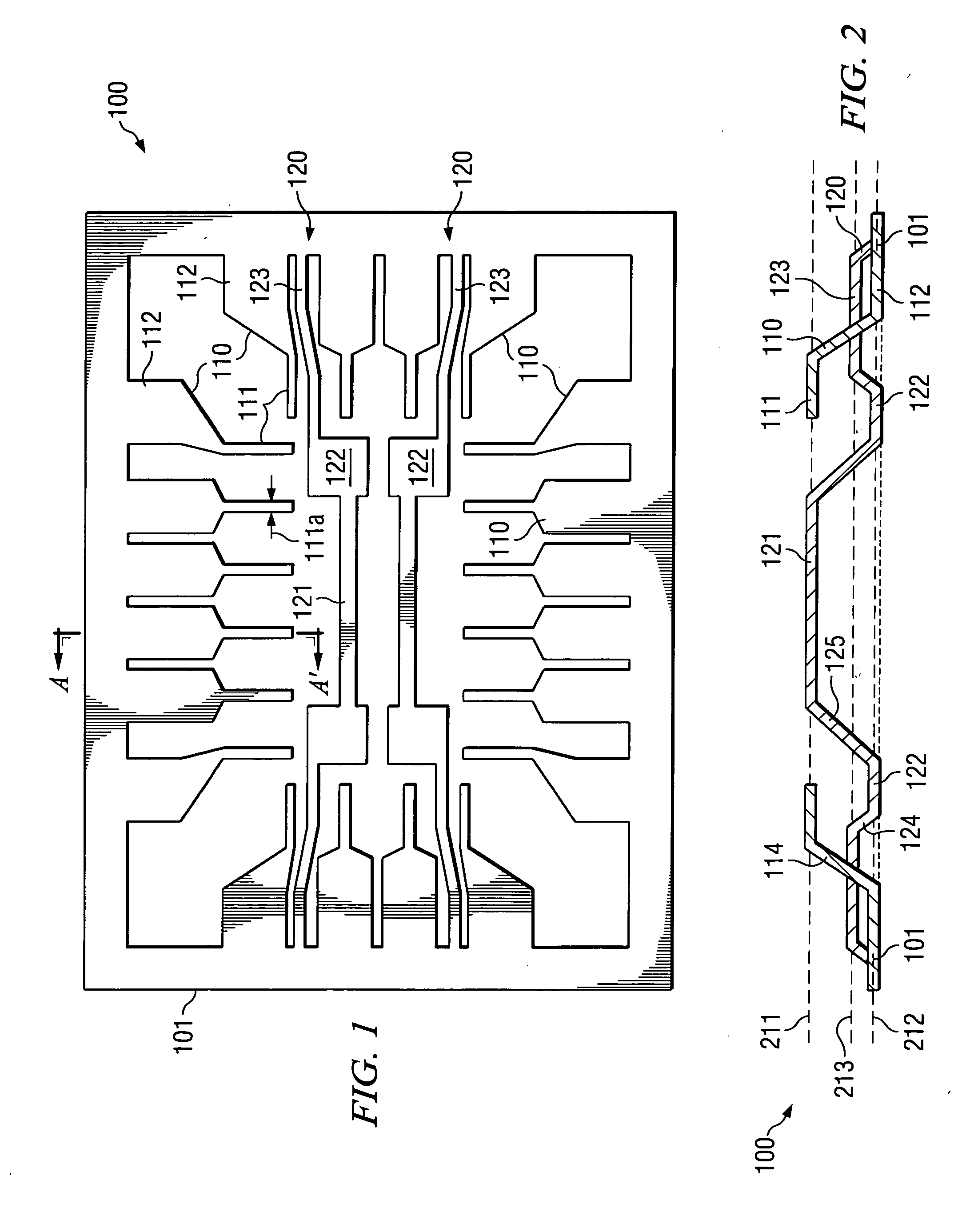

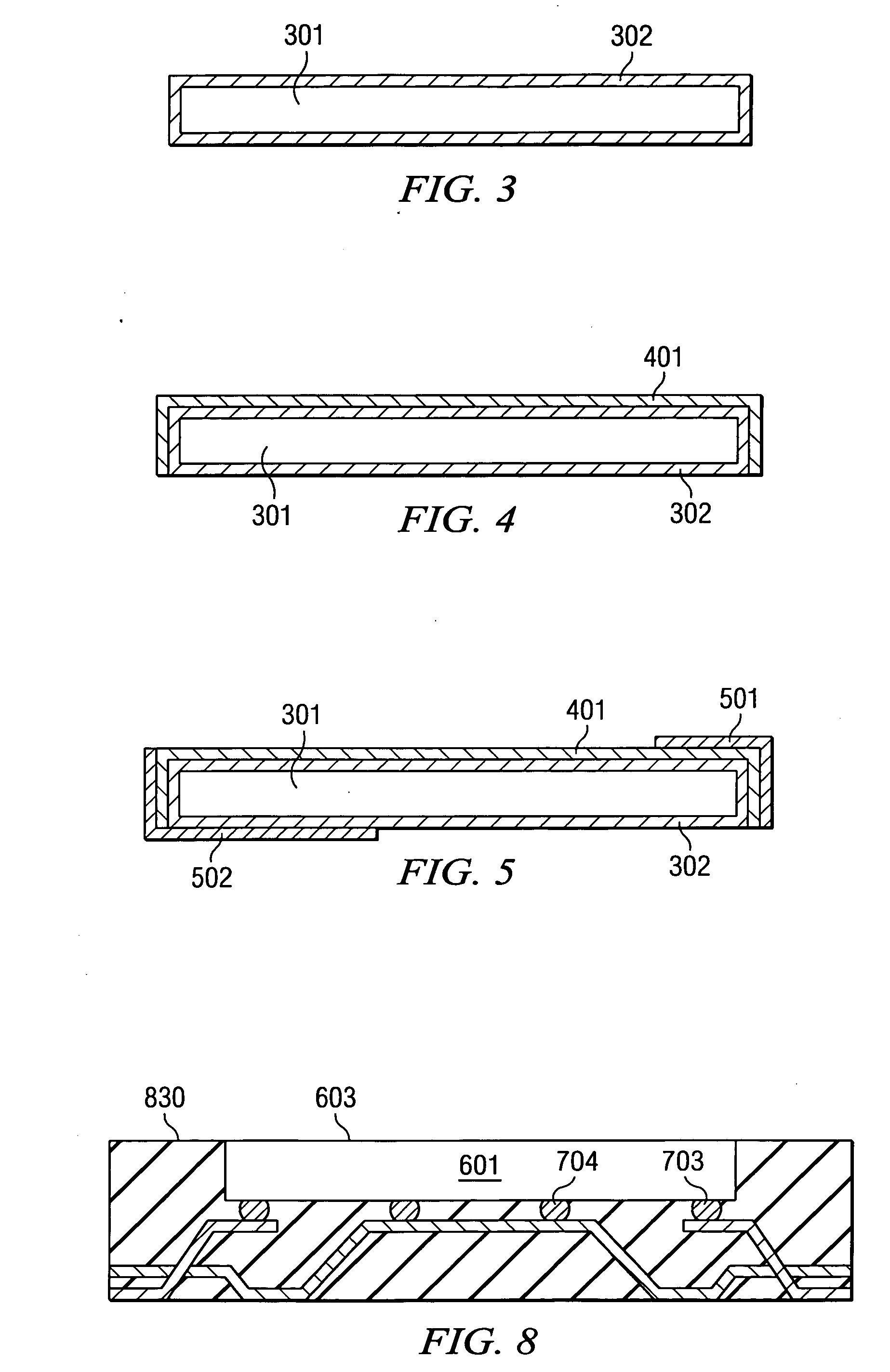

[0021]FIG. 1 is a schematic and simplified top view of a leadframe, generally designated 100, for use in the assembly of semiconductor chips; FIG. 2 is a schematic x-ray view of leadframe 100 after the forming step. FIGS. 1 and 2 illustrate two pluralities of leadframe segments, held together by frame 101. Several segments of the first plurality are designated 110, and several segments of the second plurality are designated 120.

[0022] Each segment 110 of the first plurality has a narrow end portion 111 in a first horizontal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More