Decoding circuit and decoding method for a Viterbi decoder

a decoding circuit and decoding method technology, applied in the field of decoding circuit and decoding method of viterbi decoder, can solve the problems of difficult implementation of high-speed viterbi decoder, inability to record hardware, and inability to detect hidden paths, etc., and achieve the effect of high decoding speed of viterbi decoder

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

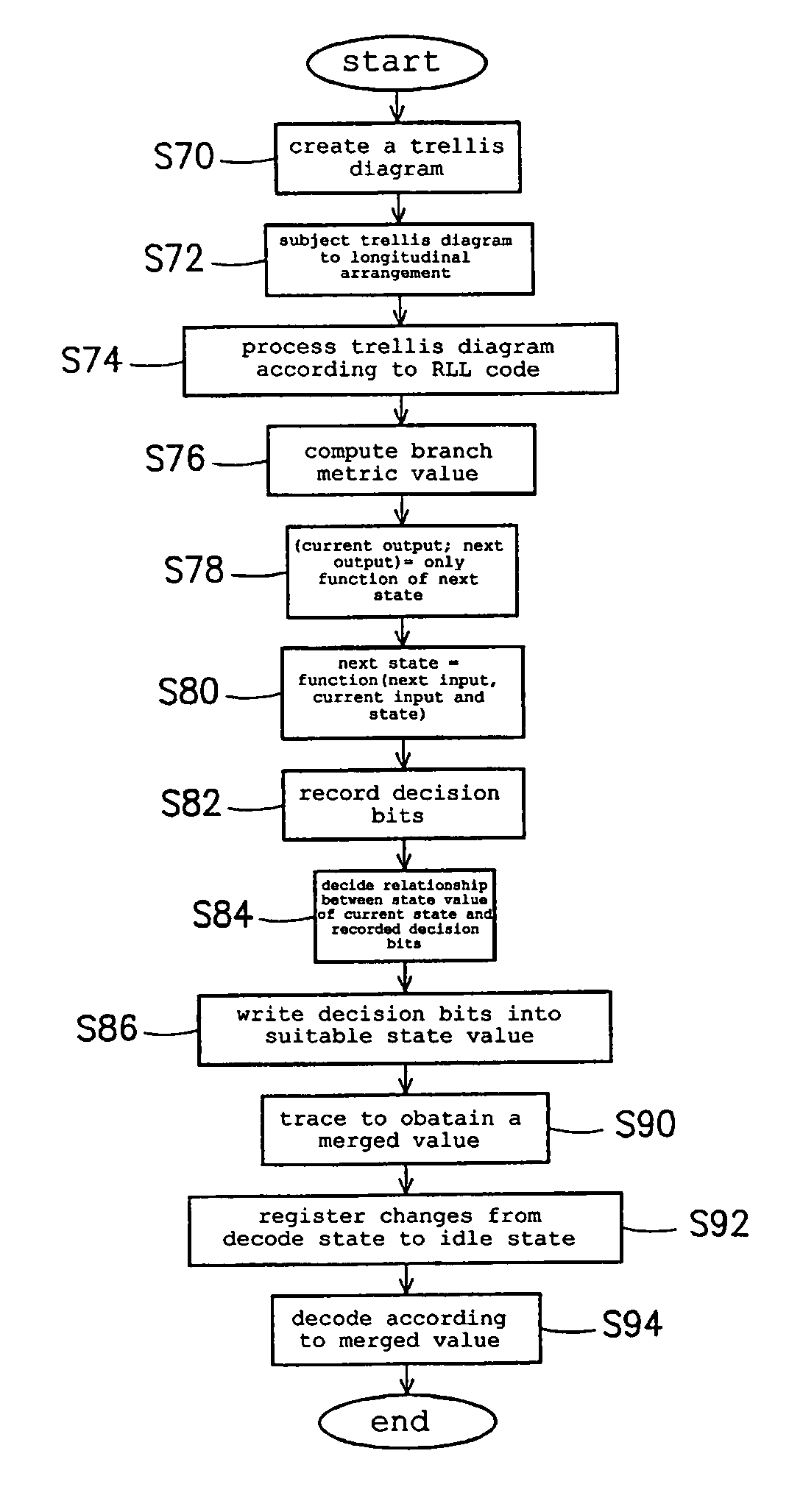

[0051]FIG. 8 is a flow chart showing the method for the Viterbi decoder of the invention. As shown in FIG. 8, a trellis diagram (as shown in FIG. 3) corresponding to the Viterbi decoder is first created in step S70. In order to overcome the bottleneck for the ACS, the trellis diagram of the Viterbi decoder is re-arranged by the re-arranging method including a transverse arrangement and a longitudinal arrangement. Taking the original trellis diagram shown in FIGS. 9A and n=2 as an example, FIG. 9B shows a transverse arrangement performed in the original trellis diagram. The so-called transverse arrangement is to merge the trellises of the n sates into a state. Although the bottleneck of ACS still exists, the time of the bottleneck is lengthened from 1T to nT. Thus, the overall speed limitations of the Viterbi decoder can be eased.

[0052]FIG. 9C is a schematic illustration showing that a longitudinal arrangement is performed in the original trellis diagram. In FIG. 9C, the trellis dia...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More