Semiconductor integrated circuit device

a technology of integrated circuit and semiconductor, applied in semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of insufficient noise reduction effect, serious power supply noise, and serious countermeasures against esd for the decoupling capacitor itself, so as to improve the esd robustness of the capacitor. , the effect of large area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

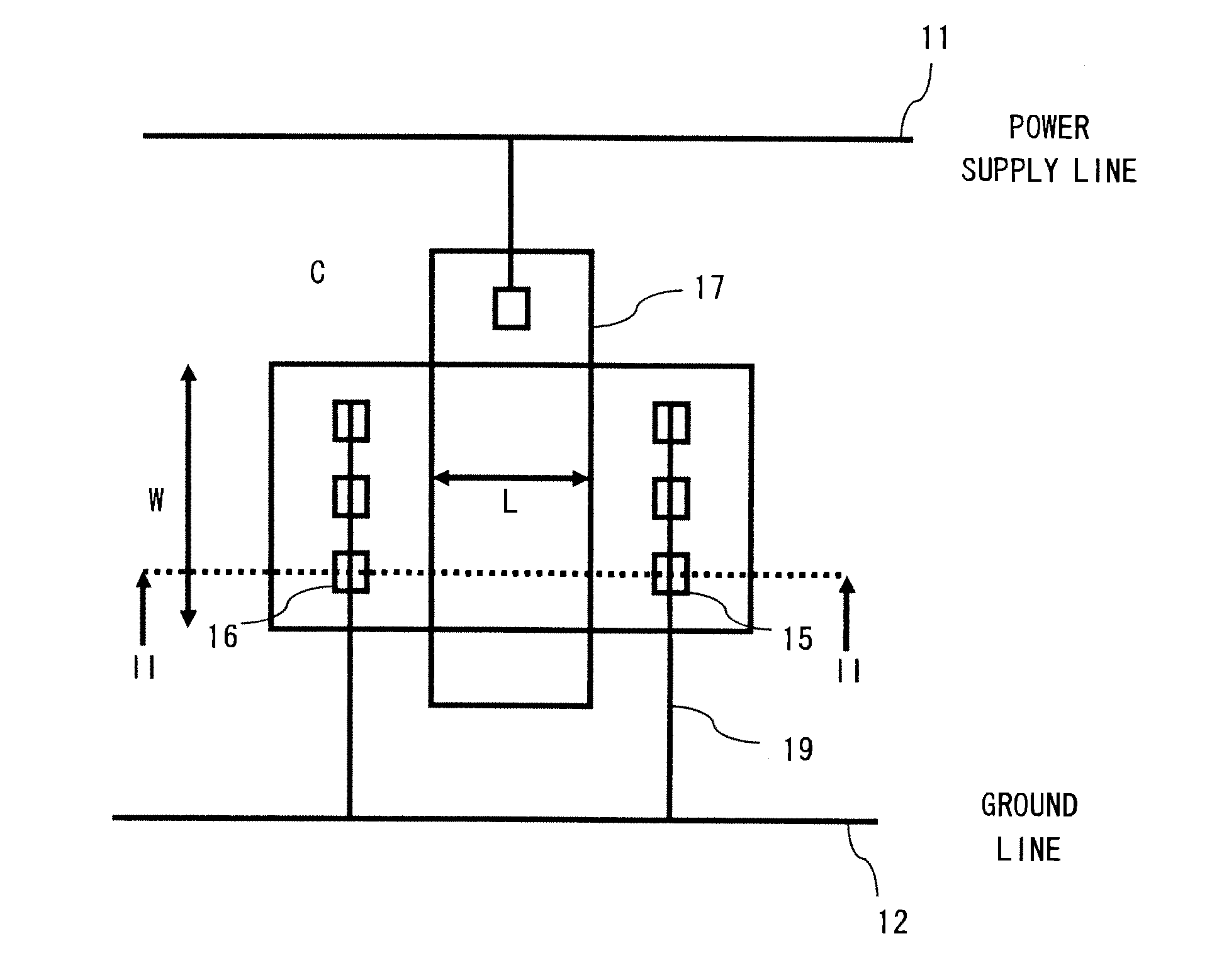

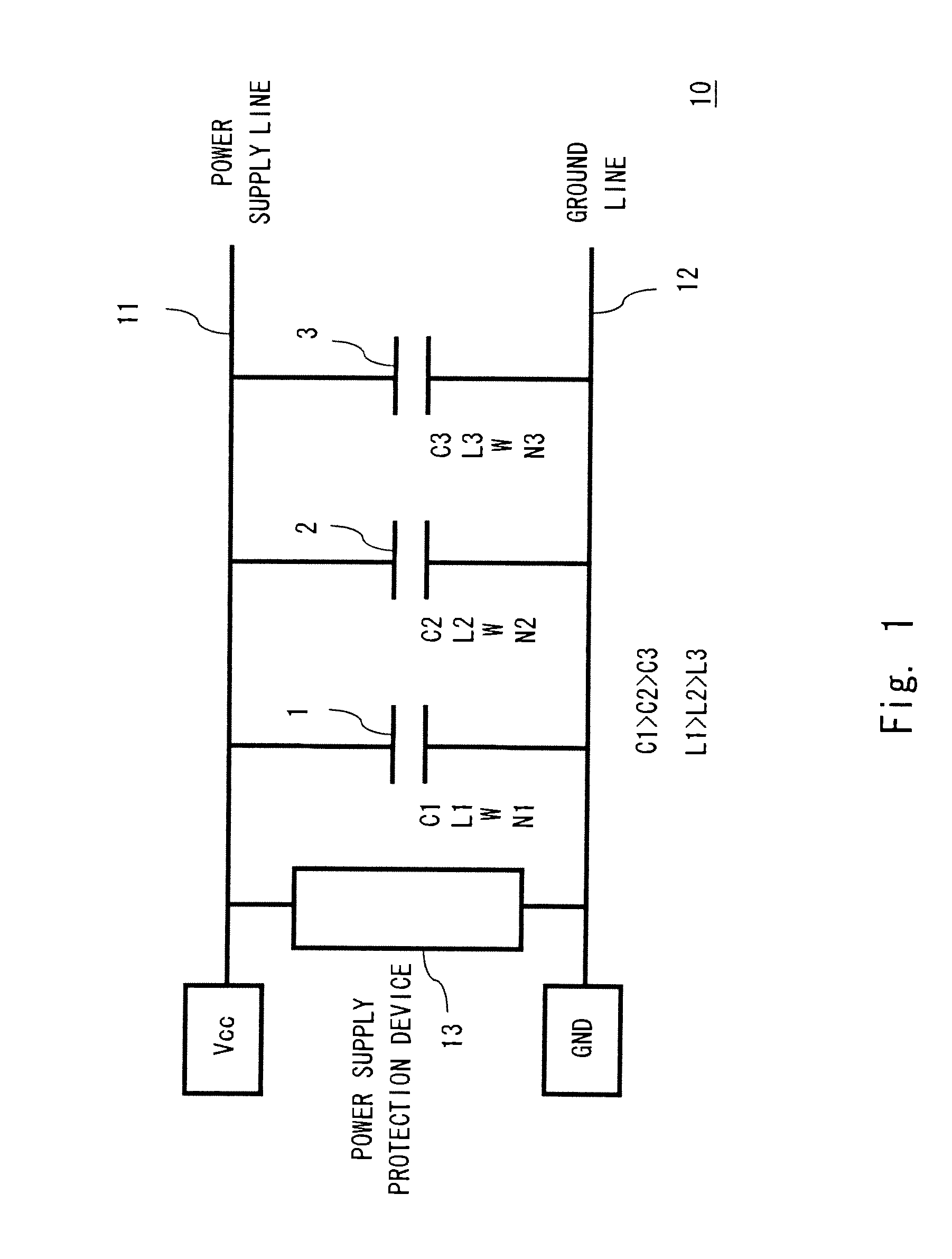

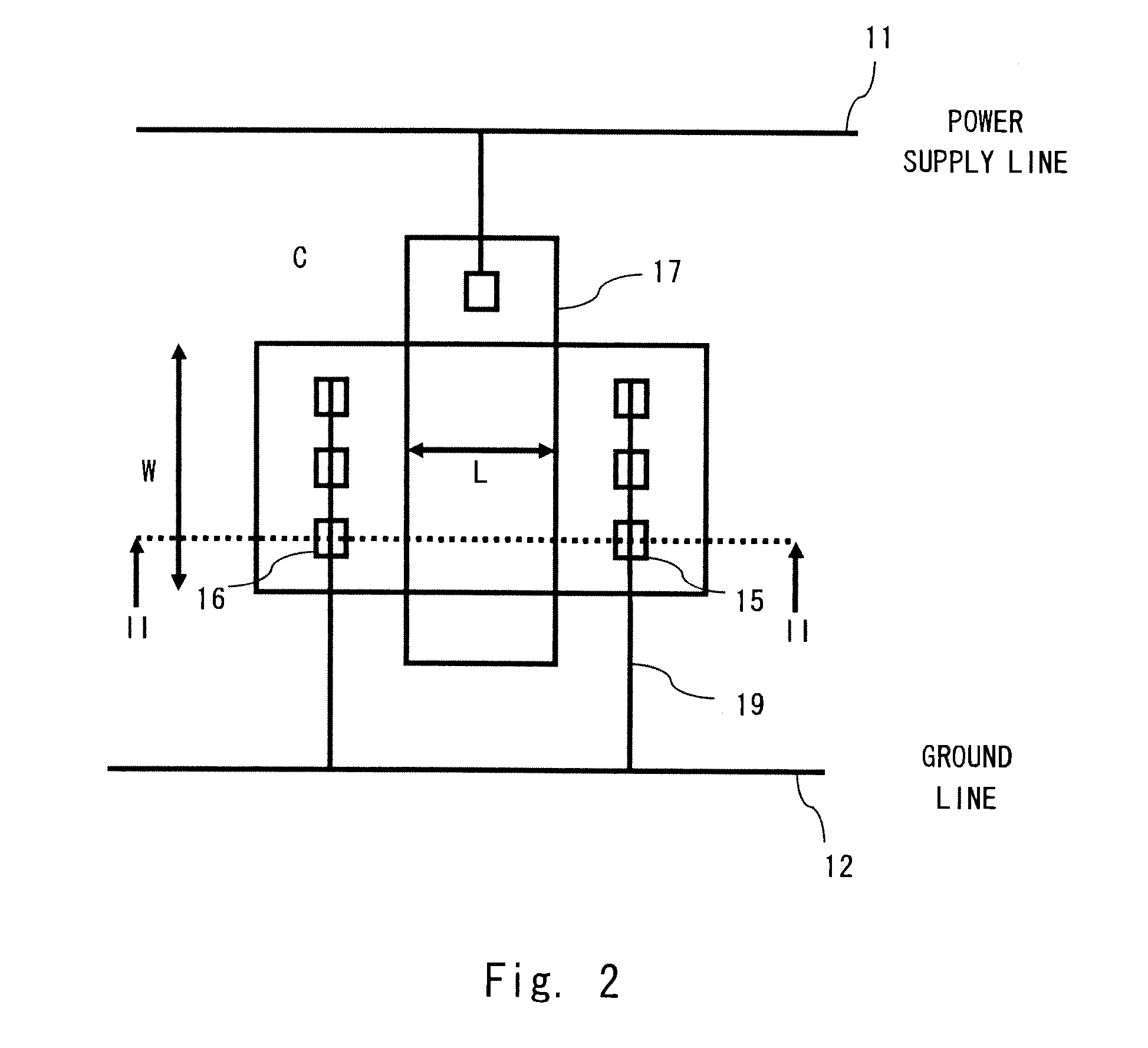

[0036]A first embodiment of the present invention is explained with reference to FIGS. 1 to 3. FIG. 1 shows the circuit configuration of a semiconductor integrated circuit device 10 according to this embodiment. Moreover, FIG. 2 is a plane view of a MOS capacitance device mounted to the semiconductor integrated circuit device 10 of this embodiment. FIG. 3 is a cross-sectional diagram taken along the line II-II of FIG. 2. Note that the internal circuit is omitted in FIG. 1.

[0037]As shown in FIG. 1, the semiconductor integrated circuit device 10 of this embodiment includes a power supply terminal Vcc, a ground terminal GND, a power supply line 11, a ground line 12, a power supply protection device 13 and capacitors 1, 2 and 3. In this embodiment, the capacitors 1, 2 and 3 are all formed of N type MOS capacitance devices. Note that in this embodiment, although the example of a semiconductor integrated circuit device having 3 capacitors is explained, it is not limited to this. Moreover,...

second embodiment

[0049]A semiconductor integrated circuit device 20 according to a second embodiment of the present invention is explained with reference to FIG. 4. FIG. 4 shows the configuration of the semiconductor integrated circuit device 20 according to this embodiment. There are many power supply lines and ground lines in the whole LSI. The power supply line and the ground line each have a trunk line and its branch line. As shown in FIG. 4, the semiconductor integrated circuit device 20 of this embodiment includes a power supply terminal Vcc, a ground terminal GND, a power supply line 21, a ground line 22 and a functional circuit block 29. The power supply line 21 includes a trunk line 23 and a branch line 25. Moreover, the ground line 22 includes a trunk line 24 and a branch line 26. The trunk line 23 is extended from the power supply terminal Vcc. Then, the branch line 25 is extended and branches from the trunk line 23. On the other hand, the trunk line 24 is extended from the ground termina...

third embodiment

[0056]A semiconductor integrated circuit device 30 according to a third embodiment of the present invention is explained with reference to FIG. 5. FIG. 5 shows the configuration of the semiconductor integrated circuit device 30 of this embodiment. A difference in this embodiment from the first embodiment shown in FIG. 1 is the locating position of the power supply terminal Vcc and the ground line GND.

[0057]As shown in FIG. 5, a power supply line 31 extended from the power supply terminal Vcc is formed toward the ground terminal GND side. Moreover, a ground line 32 extended from ground terminal GND is formed toward the power supply terminal Vcc side. Between the power supply line 31 and the ground line 32, a power supply protection device 33, capacitors 34, 35, and 36 and a power supply protection device 37 are provided from the ground terminal GND side to the power supply terminal Vcc side. That is, the distance from the power supply terminal Vcc to the capacitor 34 differs from the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More