Method and apparatus for reducing cache thrashing

a cache memory device and cache technology, applied in the field of cache memory devices, can solve the problems of significantly reducing cache performance and increasing cache misses, and achieve the effect of improving cache performance and reducing cache trashing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

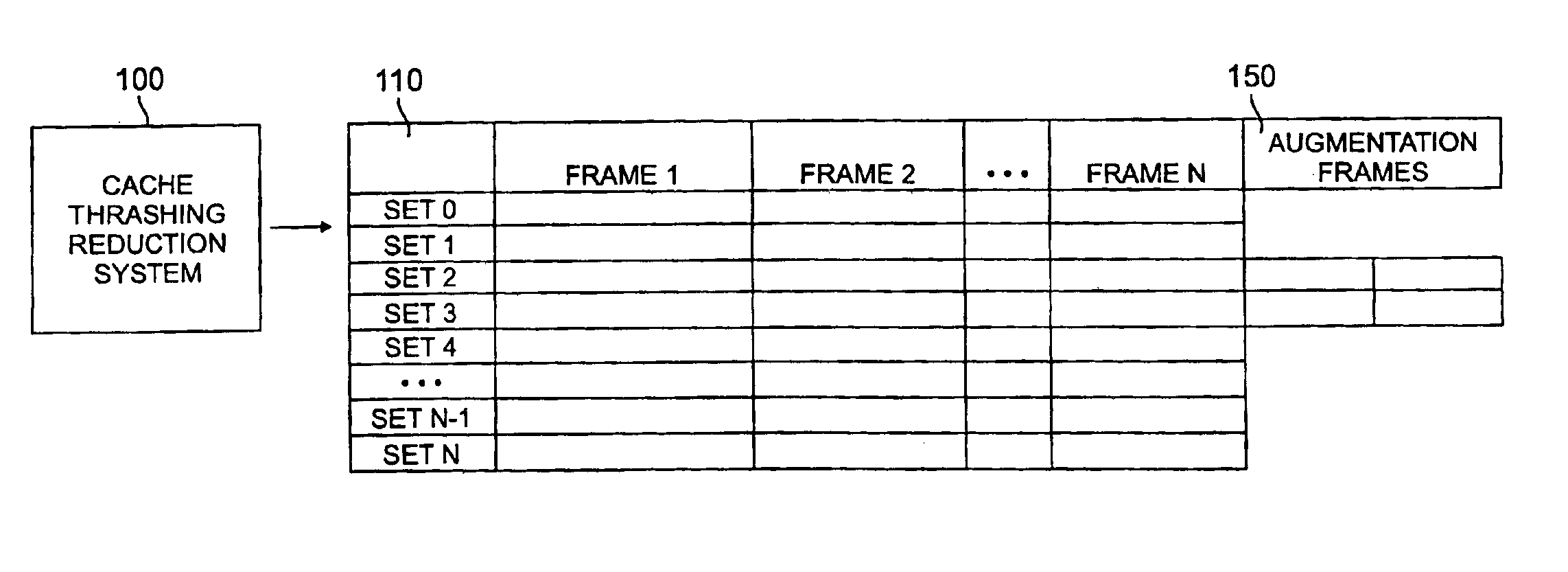

FIG. 1 illustrates a cache thrashing reduction system 100 in accordance with the present invention. The present invention improves performance of an N-way associative cache 110 by automatically detecting thrashing in a set, such as sets 2 and 3, and then reducing thrashing in the thrashed set(s) by providing one or more augmentation frames 150 as additional cache space. In this manner, the trashed sets can remain in the cache longer, improving their hit rate. The augmentation frames 150 are obtained, for example, by mapping the blocks that map to a thrashed set to one or more additional, less utilized sets. While the present invention is illustrated with a two-way set associative instruction cache that has two frames at each set address, the present invention may be incorporated into all cache organizations (data or instruction), as would be apparent to a person of ordinary skill in the art. The cache thrashing reduction system 100 and cache 110 can be part of a digital signal proce...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More