Stack type chip packaging structure, chip packaging body and manufacturing method

A chip packaging structure and chip packaging technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical solid-state devices, etc., can solve the problems of heat dissipation, the overall thickness cannot be further reduced, and achieve the effect of high packaging integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

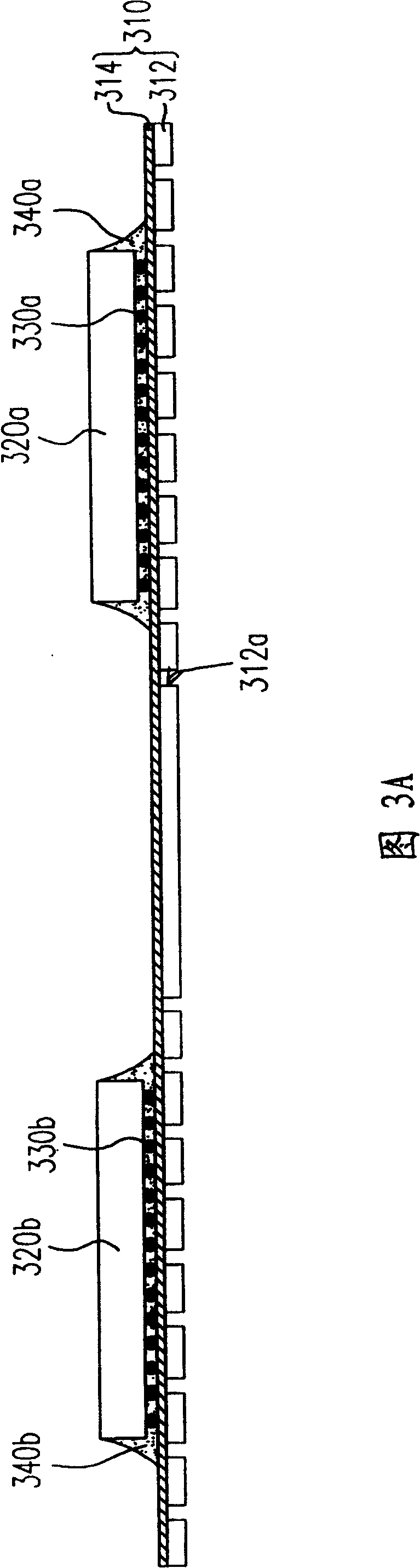

[0046] Figure 3A to Figure 3Cis a sectional view of the manufacturing process of the stacked chip package structure according to the first embodiment of the present invention. Please refer to FIG. 3A , the manufacturing method of the stacked chip packaging structure of this embodiment includes the following steps. First, a flexible circuit board 310 is provided, and the flexible circuit board 310 includes a flexible substrate 312 and a patterned circuit layer 314 disposed on the flexible substrate 312 . In this embodiment, the material of the flexible substrate 312 may be polyimide or other flexible plastic materials.

[0047] Then, a plurality of through holes 312 a are formed in the flexible substrate 312 , and these through holes 312 a expose part of the patterned circuit layer 314 . In addition, the method of forming the through holes 312a may be an etching process or other processes capable of forming through holes. Next, chips 320 a and 320 b are provided, and the chi...

no. 2 example

[0056] Figure 4A to Figure 4B A cross-sectional view of the manufacturing process of the stacked chip package structure according to the second embodiment of the present invention is shown. Please refer to Figure 4A , this embodiment is similar to the above embodiment, the main difference between the two lies in that: the chips 410a and 420b are respectively arranged on the flexible circuit board 310, and then a plurality of wires 420a and 420b are formed. The chip 410a is electrically connected to the patterned circuit layer 314 through the wire 420a, and the chip 410b is electrically connected to the patterned circuit layer 314 through the wire 420b. Next, encapsulants 430 a and 430 b are respectively formed on the flexible circuit board 310 , wherein the encapsulant 430 a covers the chip 410 a and the wire 420 a. In addition, the encapsulant 430b covers the chip 410b and the wire 420a.

[0057] Then, the flexible circuit board 310 is bent to form an accommodating space...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More