Method of specifying pin states for a memory chip

A foot position and status technology, applied in the field of systematic methods, can solve problems such as confusion, achieve the effect of improving services, reducing possible combinations, and avoiding confusion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the above objects, features and advantages of the present invention more comprehensible, a preferred embodiment will be described in detail below together with the accompanying drawings.

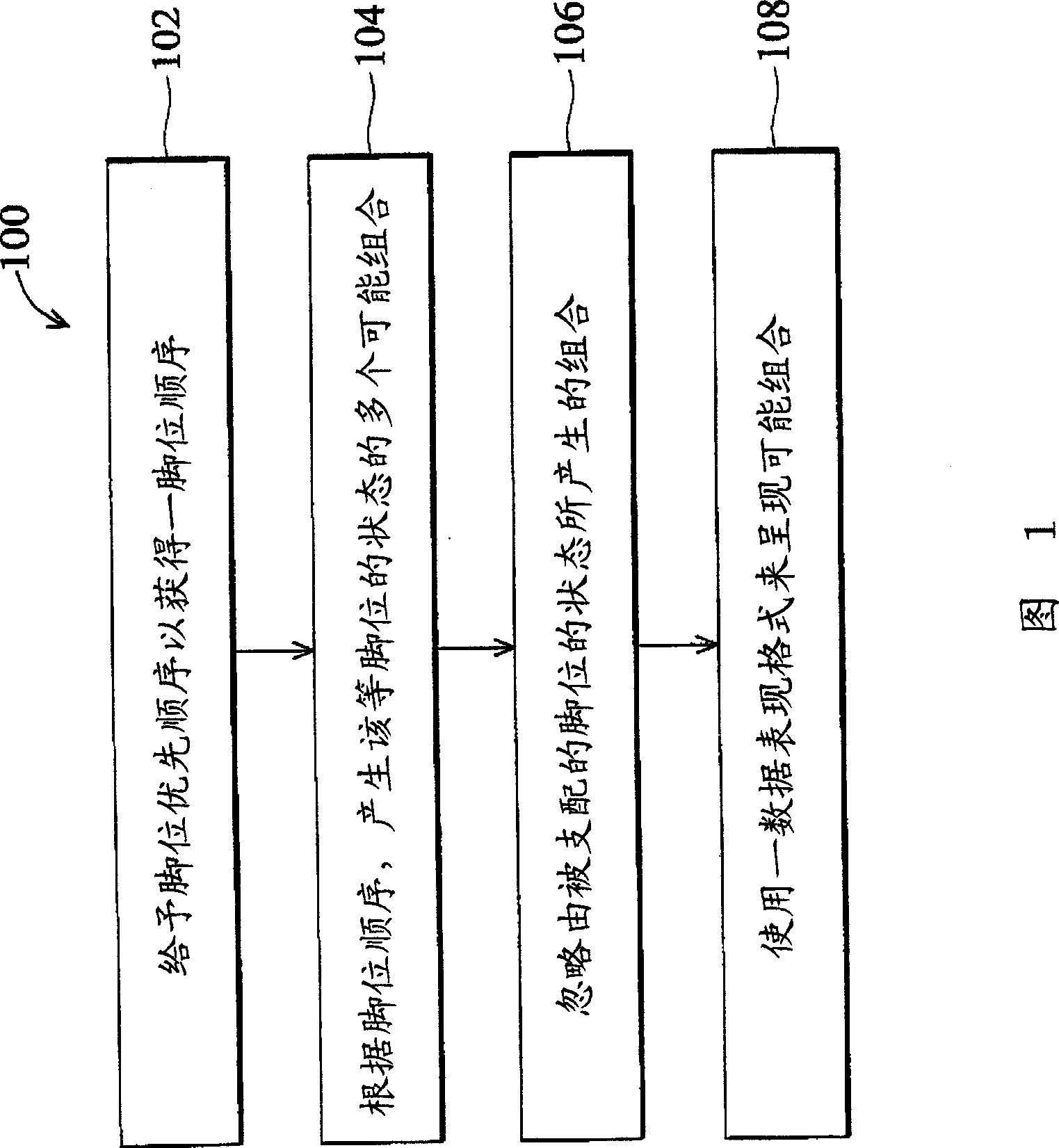

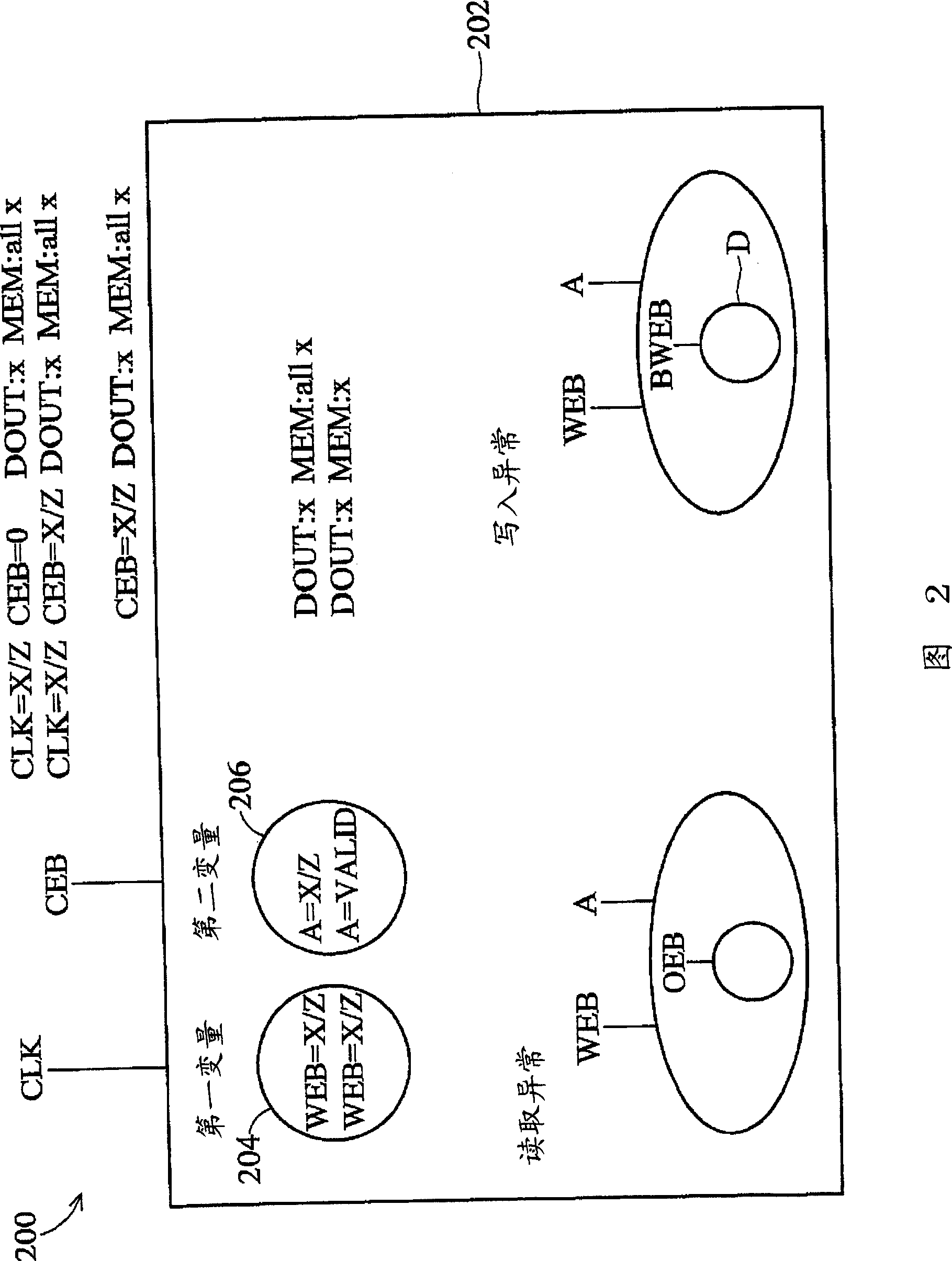

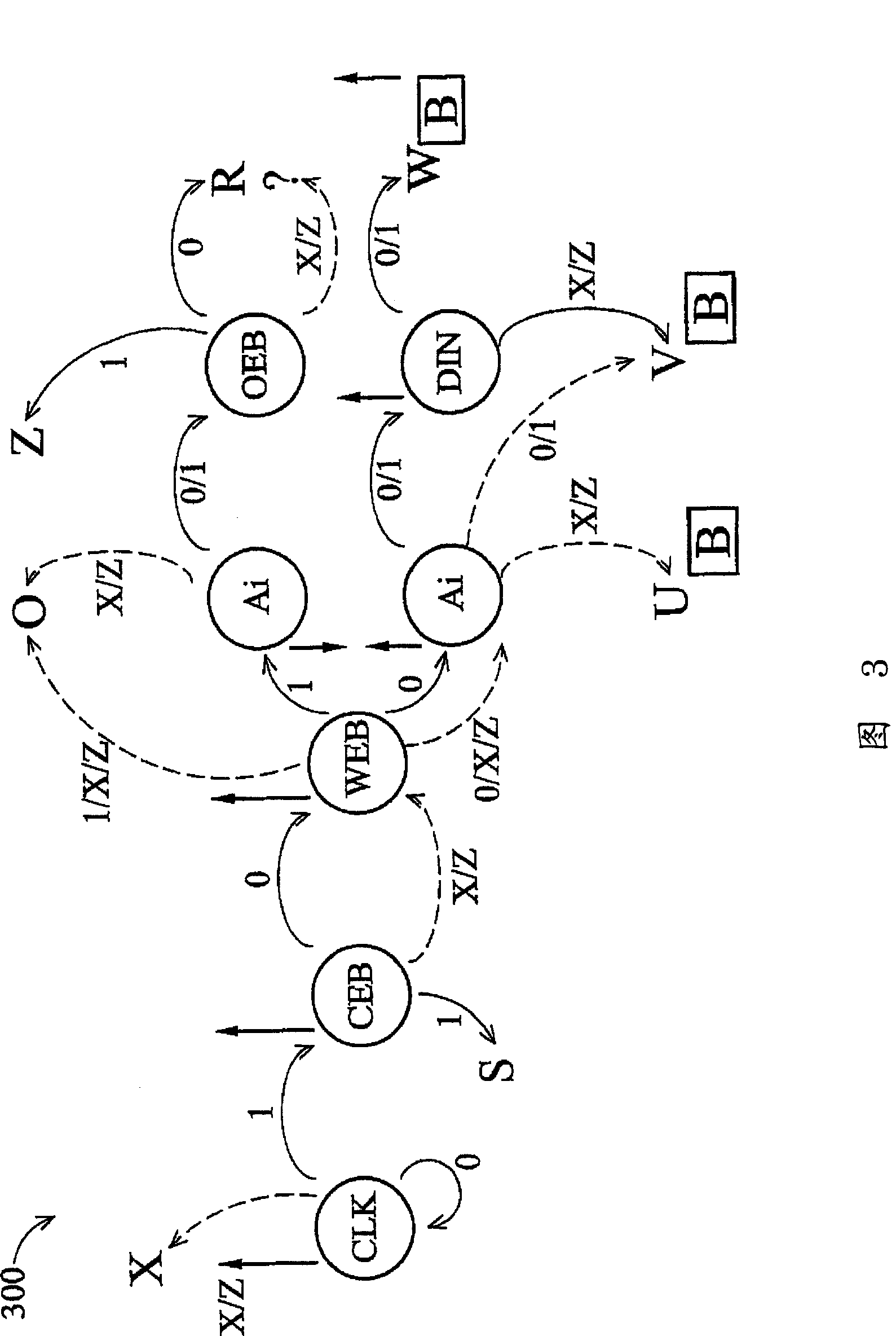

[0025] This method provides a systematic way to specify all possible combinations of pin states, including memory chip normalities and abnormal states, such as exception states and timing violation states. A systematic approach is important because it can help reduce the actual number of pin state combinations needed to provide a complete specification of memory behavior. For example, when specifying four different states of a memory die with seven input pins, such as high state, low state, unknown state, provided no systematic approach is used to reduce the total number of possible combinations and the high impedance state, will cost 16378 or 4 7 a combination of species. The method provided by the present invention can provide specifications for the behavior of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com