Testing method capable of configuring FPGA interconnection resource with four times

A test method and a technology for interconnecting resources are applied in the field of testing FPGA interconnect resources with only four configurations, which can solve the problems of reducing the number of test configurations and failing to effectively distinguish fault locations, so as to reduce the number of test configurations and avoid Test the effect of repeating and simplifying the connection relationship

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

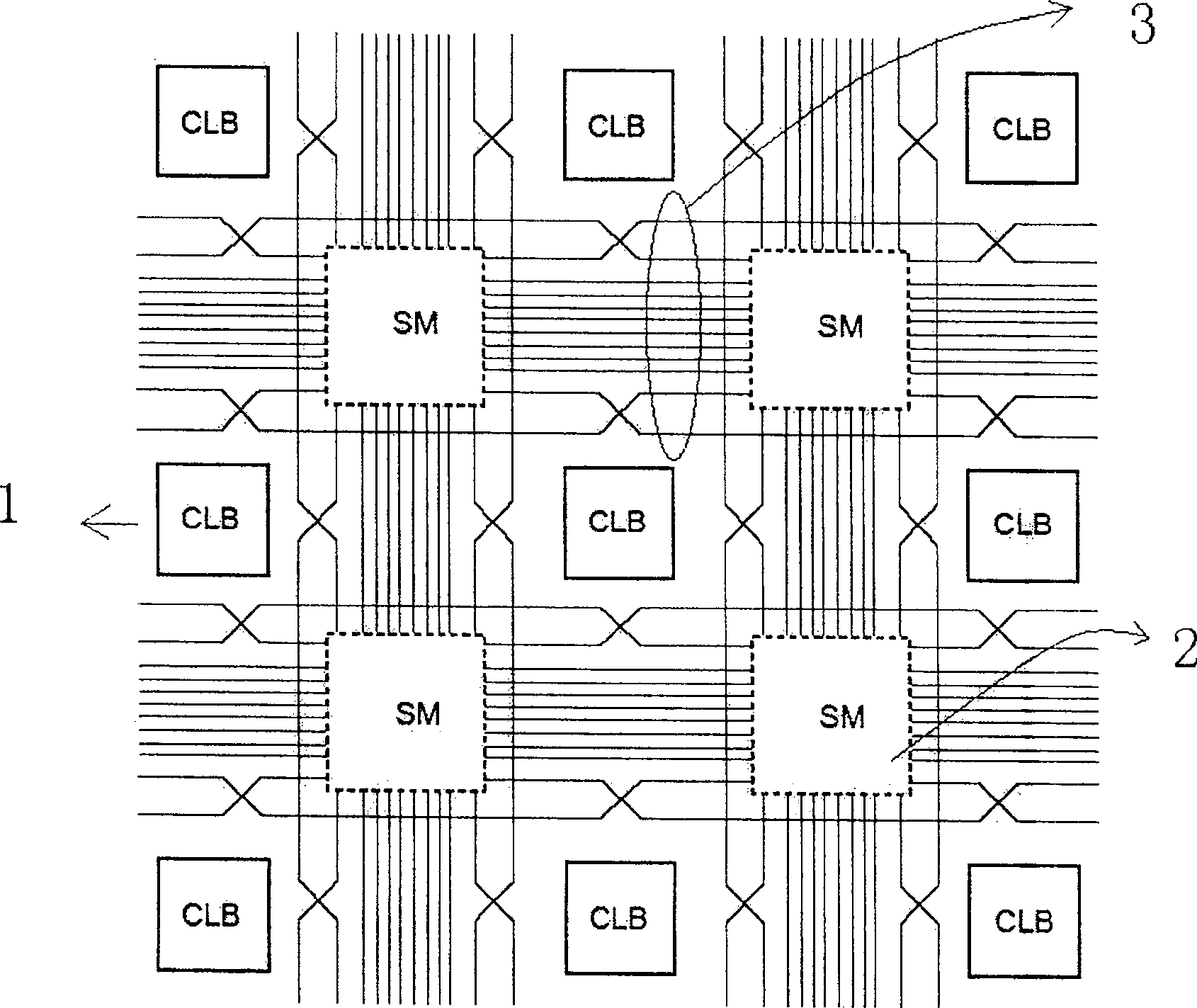

[0044] The basic structure of FPGA is as figure 1 As shown, its basic structure is composed of programmable logic module CLB1, programmable switch matrix SM2 and interconnection segment 3. The switch matrix SM2 and the interconnection segment 3 surround the programmable logic to form a network structure and realize flexible programmability.

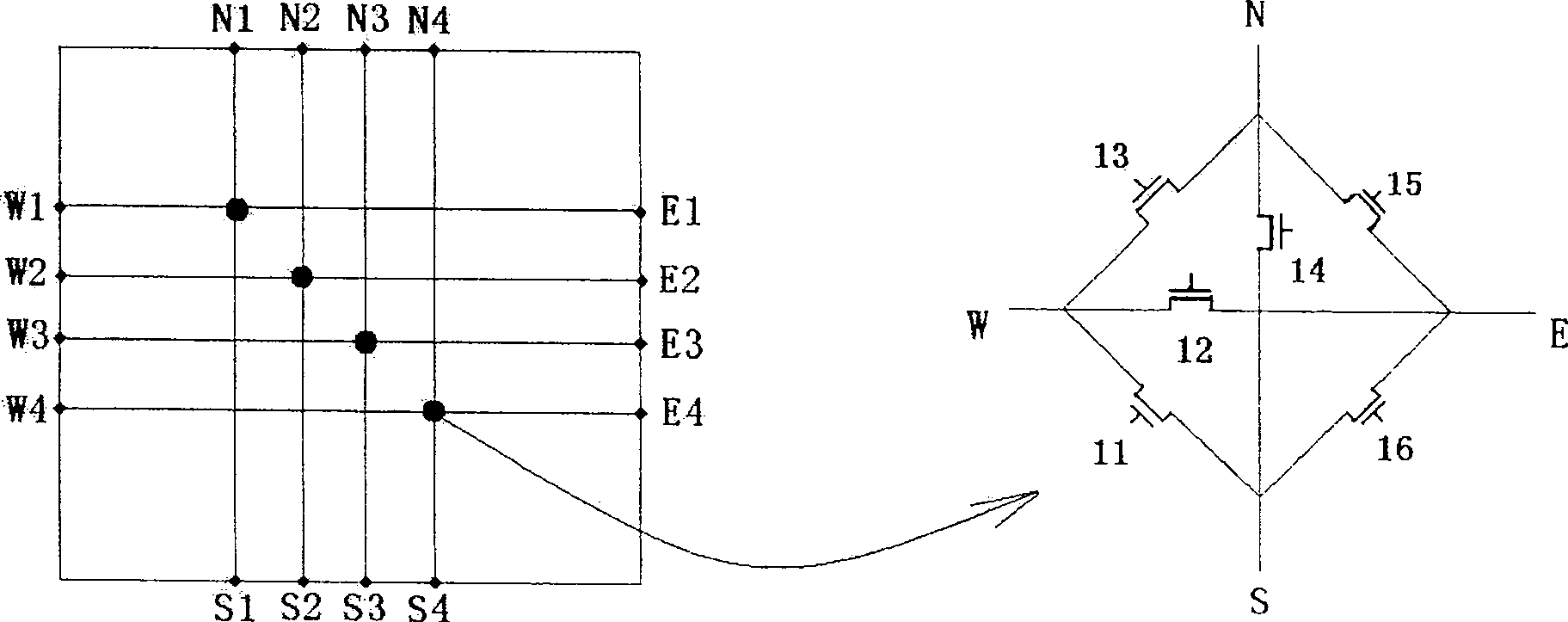

[0045] The structure of switch matrix SM2 is as figure 2 As shown, it is divided into four types of switches: West, South, East, and North. By combining the West-East direction switch of the switch matrix SM2, that is, the WE switch 12, the South-North direction switch, that is, the SN switch 14, and the West-North direction switch The switch is the WN switch 13, the West-South direction switch is the WS switch 11, the East-North direction switch is the EN switch 15, and the East-South direction switch is the ES switch 16. According to the method of cascading in the same direction, a serpentine test channel is formed. test. In the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More