Test structure and method for interconnect resources in field programmable gate array (FPGA)

A technology of test structure and test method, applied in the direction of digital circuit test, electronic circuit test, static memory, etc., can solve the problems of long test time and unfavorable practical application, and achieve the effect of shortening test time and reducing the number of test configurations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

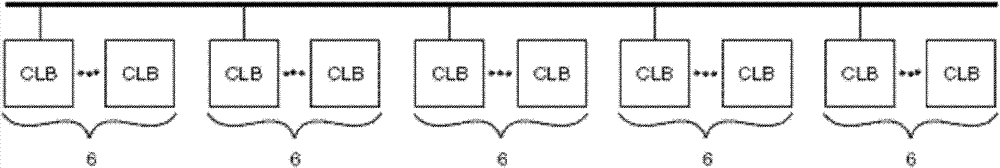

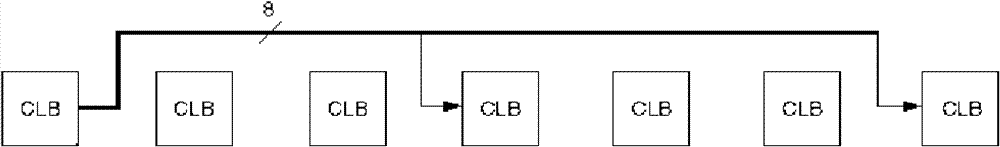

[0035] Take the XC3S400 FPGA of the Spartan 3 series of Xilinx as an example. This type of FPGA has 34 rows and 32 columns in total, including two rows and two columns of input and output ports IOB and two columns of block RAM (random access memory). There are eight double long lines and intelligent long lines in the east, west, north and south directions. Among them, the east line and west line are staggered, and the south line and north line are staggered. Column line segment test BIST structure such as Figure 6 As shown, the line segment test BIST structure is as follows Figure 7 shown.

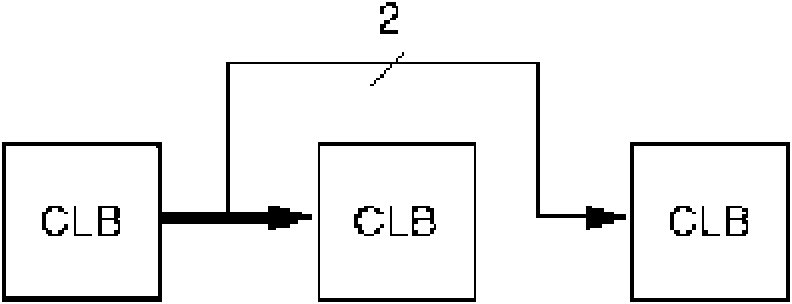

[0036]1) the test structure of a kind of FPGA internal connection resource of the present invention, it is a kind of built-in self-test structure, its test pattern generator TPG 1, output response analyzer ORA 2 and tested circuit CUT 10 are all by FPGA internal resources constitute. The entire test structure will be implemented by writing a test configuration program to configure t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More