FPGA interconnect resource allocation generation method based on reinforcement learning

A technology of interconnected resources and enhanced learning, applied in the field of FPGA, can solve the problems of inability to test Global, no automatic configuration, and many configuration times, and achieve the effect of reducing the number of test configurations, high test efficiency, and high test coverage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

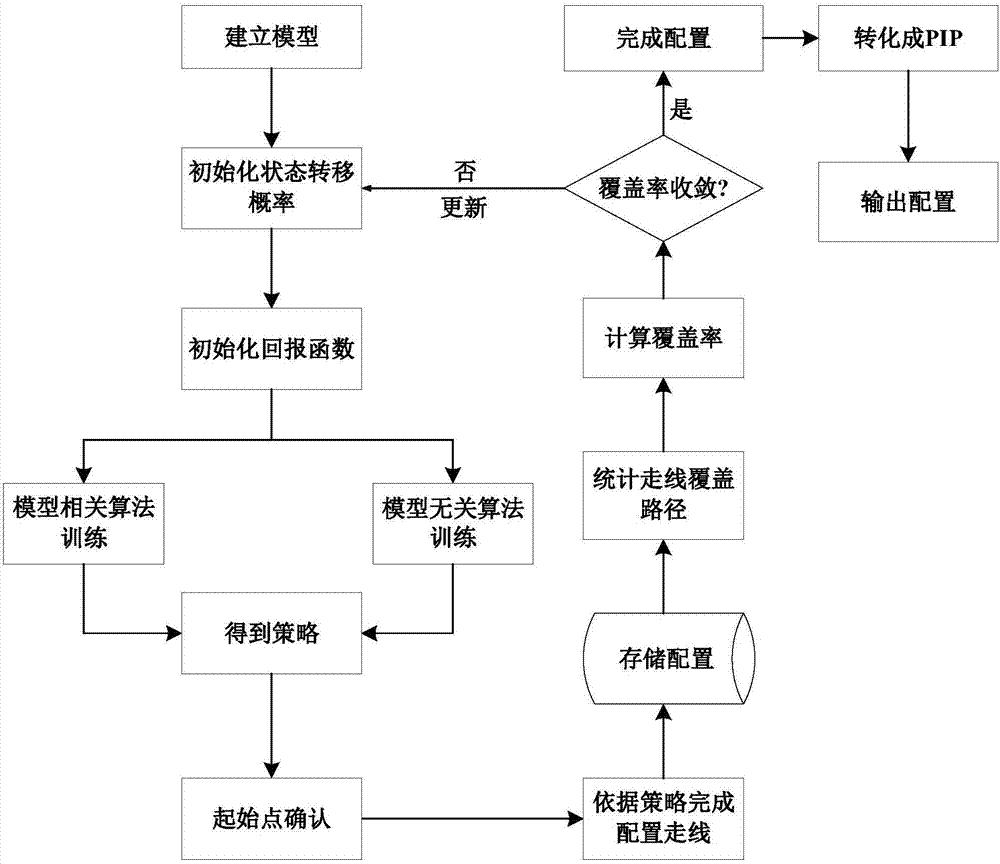

[0038] This embodiment provides a method for generating FPGA interconnection resource configuration based on reinforcement learning, such as figure 1 shown, including the following steps:

[0039] Step 1: Build an interconnected resource model of FPGA based on reinforcement learning

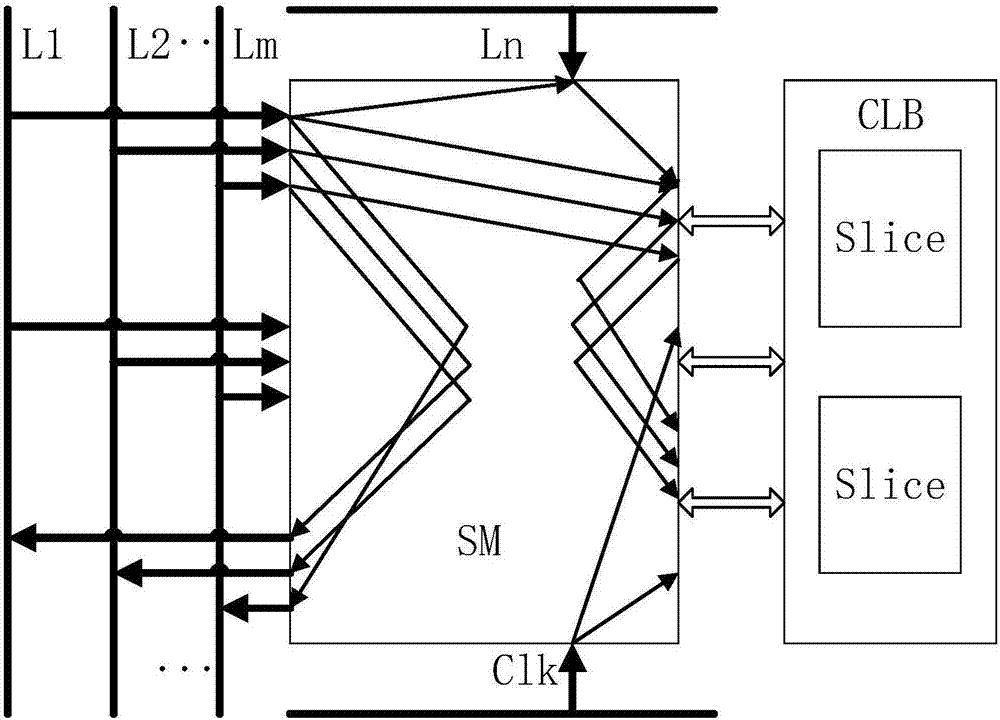

[0040] Each chip switch box (SM) in the FPGA has the same structure and is arranged in an array. Each endpoint in the chip switch box is defined as a state s, and the SM coordinate model is used to identify the same endpoint in each SM, and the FPGA system state set is obtained:

[0041] Among them, N is the total number of states;

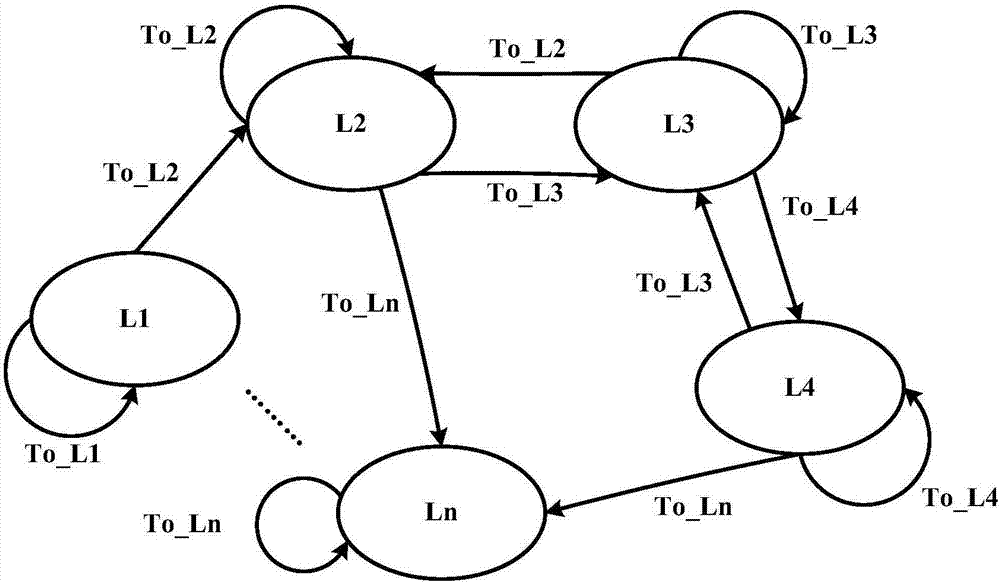

[0042] All states in any chip switch box are layered according to the type of metal interconnection wires they are connected to, that is, states of the same type are collectively called a layer, and the connections between layers are onl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More