Method for measuring MOS transistor dismatching features

A technology of oxide semiconductors and measurement methods, applied in semiconductor/solid-state device testing/measurement, special data processing applications, instruments, etc., can solve problems such as inability to fully and truly reflect product mismatch characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

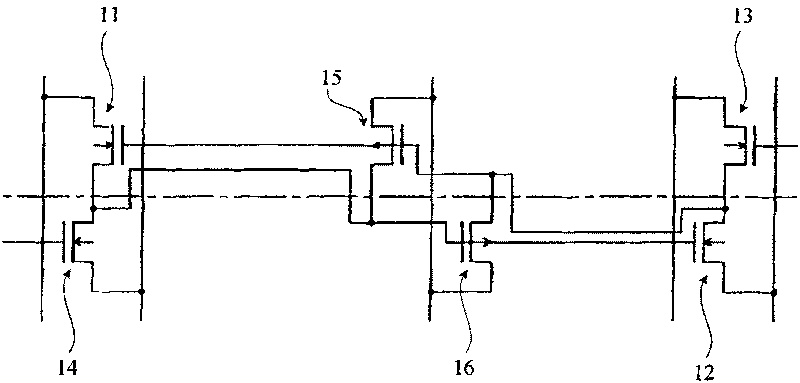

[0045]After a semiconductor device including two or more identical MOS transistors is manufactured, the matching degree of the two or more identical MOS transistors is often one of the main parameters for judging the performance of the semiconductor device. Since some semiconductor devices are sensitive to differences in electrical parameters of the same MOS transistors, that is, mismatch characteristics, it is necessary to understand such differences and minimize such differences. The invention provides a method for measuring the mismatch characteristic of a MOS transistor.

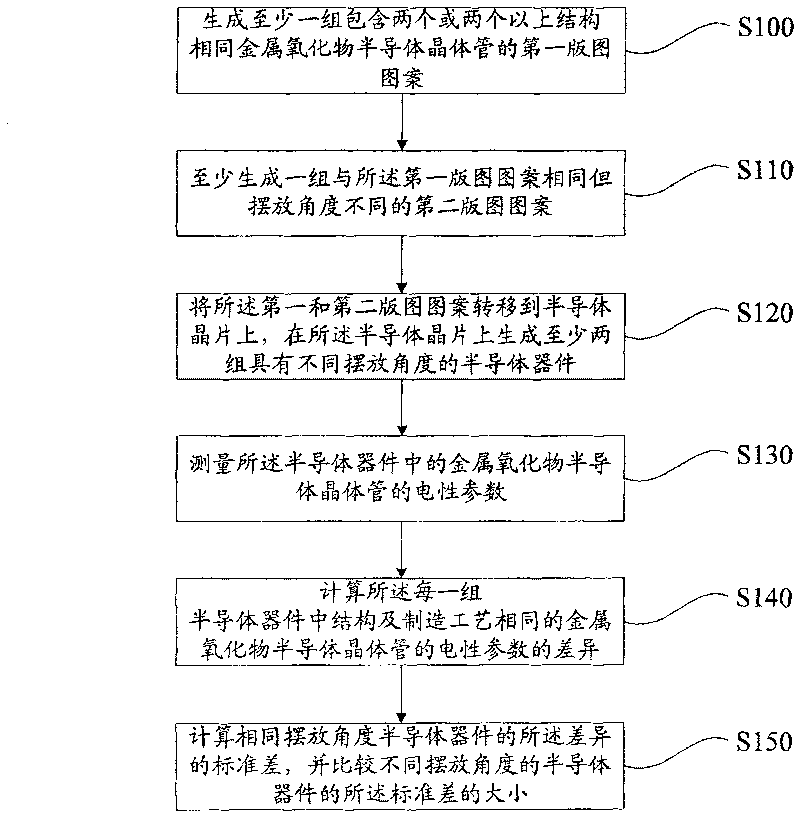

[0046] figure 2 It is a flow chart of an embodiment of the method for measuring mismatch characteristics of MOS transistors in the present invention.

[0047] Such as figure 2 In the flow chart shown, at first, at least one group of first layout patterns of semi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More