Data processing method and communications system and relevant equipment

A technology of processor and target device, applied in the field of communication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

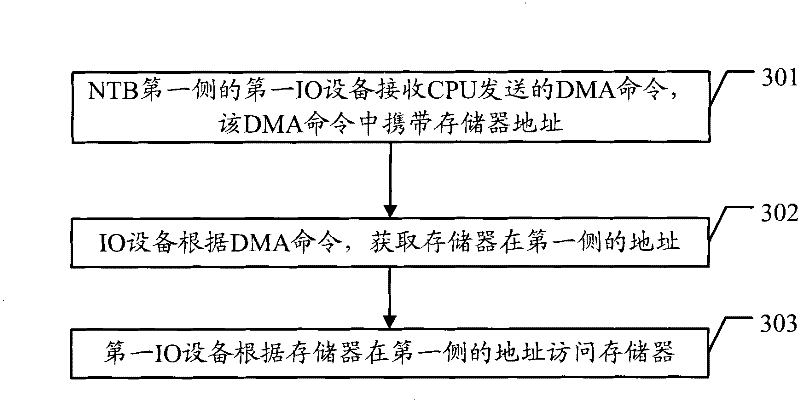

[0034] Such as image 3 As shown, the data processing method of this embodiment includes the following steps:

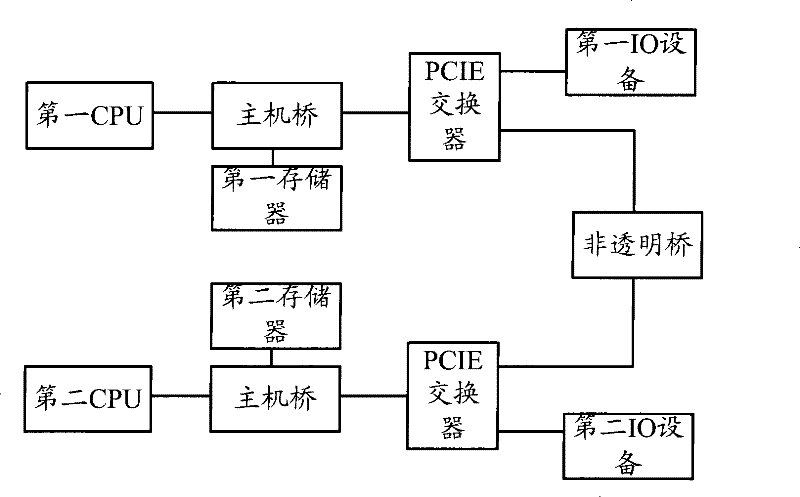

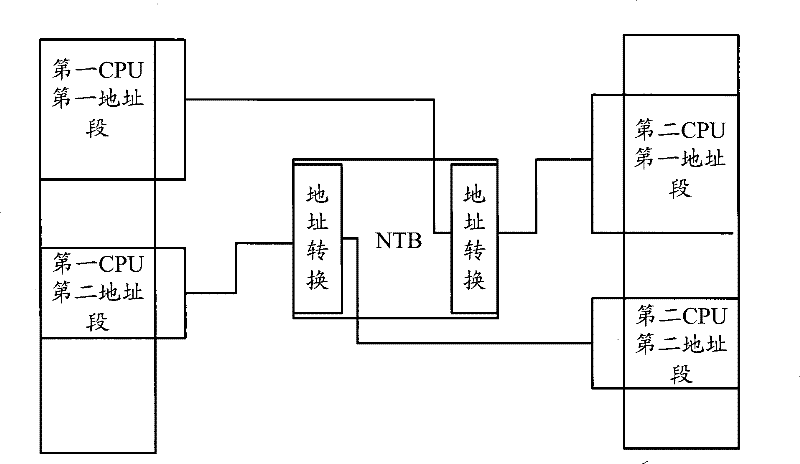

[0035] 301. The first IO device on the first side of the NTB receives a DMA command sent by the CPU, and the DMA command carries a memory address; the CPU may be the second CPU on the second side of the NTB or the first CPU on the first side of the NTB, and the memory It can be the second memory on the second side of the NTB or the first memory on the first side of the NTB; where the first IO device, the first CPU, and the first memory are on the first side of the NTB, using the same first addressing space ; The second CPU and the second memory are on the second side of the NTB, using the same second addressing space; the first addressing space and the second addressing space are mutually independent addressing spaces; the first CPU and the second The CPU will allocate an address space to NTB for the mutual mapping of the two address spaces, and establish the corres...

Embodiment 2

[0043] see Figure 4 , the data processing method of this embodiment includes:

[0044] 401. The CPU on the source side constructs a DMA command and sends it to the target device. When the target device and the CPU are on the same side of the NTB, the CPU directly sends the DMA command to the target device on the same side through the bus. When the target device and the CPU are on the same side of the NTB When the different sides of the CPU are on different sides, the CPU forwards the DMA command to the target device on the other side through the NTB;

[0045] Wherein, the DMA command includes a source side address of the target device and a DMA source side address, the source side address of the target device is used to indicate the receiving device of the DMA command, and the DMA source side address is used to indicate the memory during the DMA operation;

[0046] In this embodiment, when the first CPU needs to communicate with the second IO device isolated by the NTB, the ...

Embodiment 3

[0067] see Figure 5 , the data processing method of this embodiment includes:

[0068]501. The CPU on the source side constructs a DMA command and sends it to the target device. When the target device and the CPU are on the same side of the NTB, the CPU directly sends the DMA command to the target device on the same side through the bus. When the target device and the CPU are on the same side of the NTB When the different sides of the CPU are on different sides, the CPU forwards the DMA command to the target device on the other side through the NTB;

[0069] Wherein, the DMA command includes a source side address of the target device and a DMA target side address, the source side address of the target device is used to indicate the receiving device of the DMA command, and the DMA target side address is used to indicate the memory during the DMA operation;

[0070] In this embodiment, when the first CPU needs to communicate with the second IO device isolated by the NTB, the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More