Circuit and method for self repairing multiport memory

A technology for repairing circuits and repairing methods, applied in static memory, instruments, etc., can solve problems such as multi-port memory port related errors, no reliable self-repair technology, etc., to avoid incorrect or incomplete repairs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

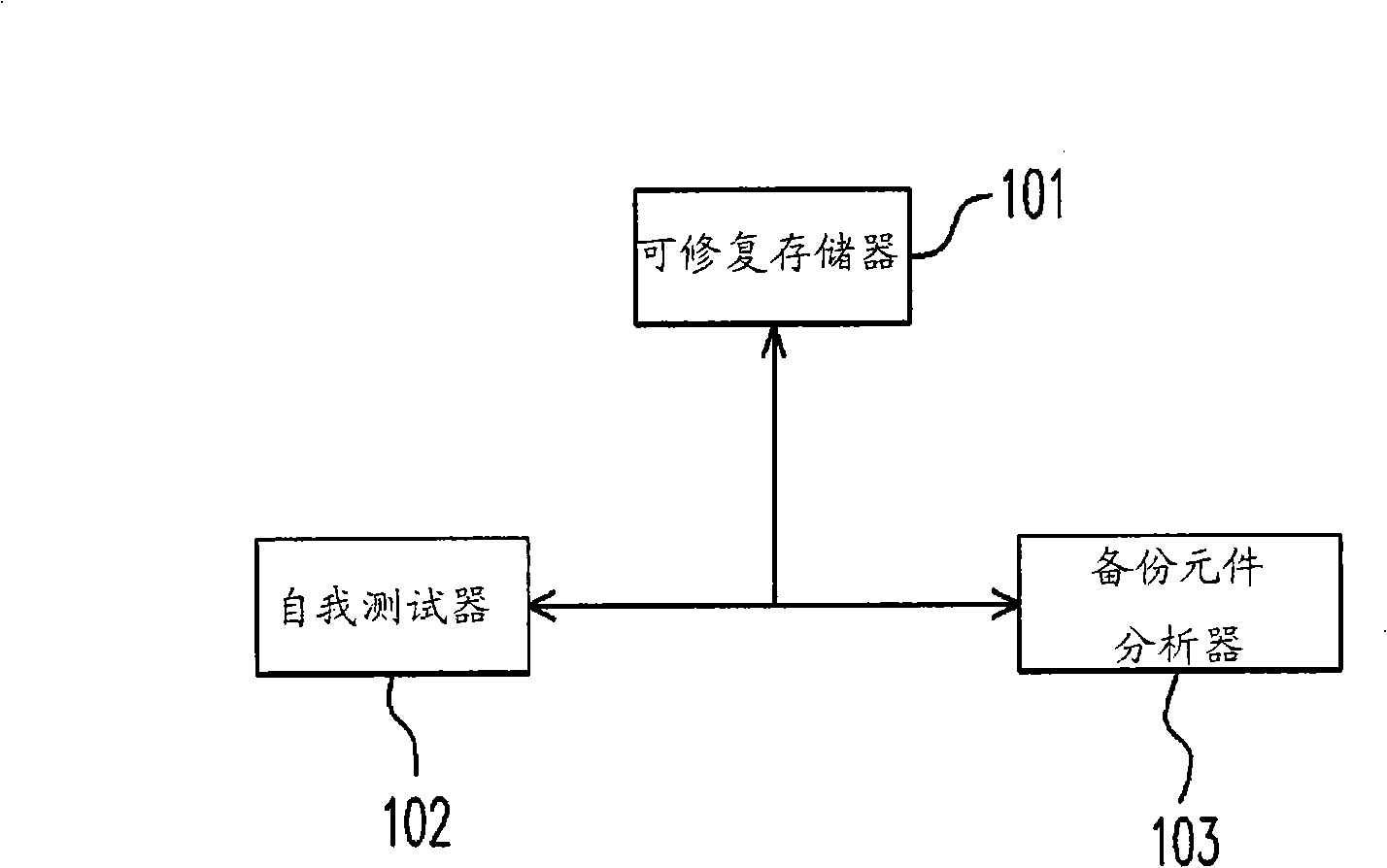

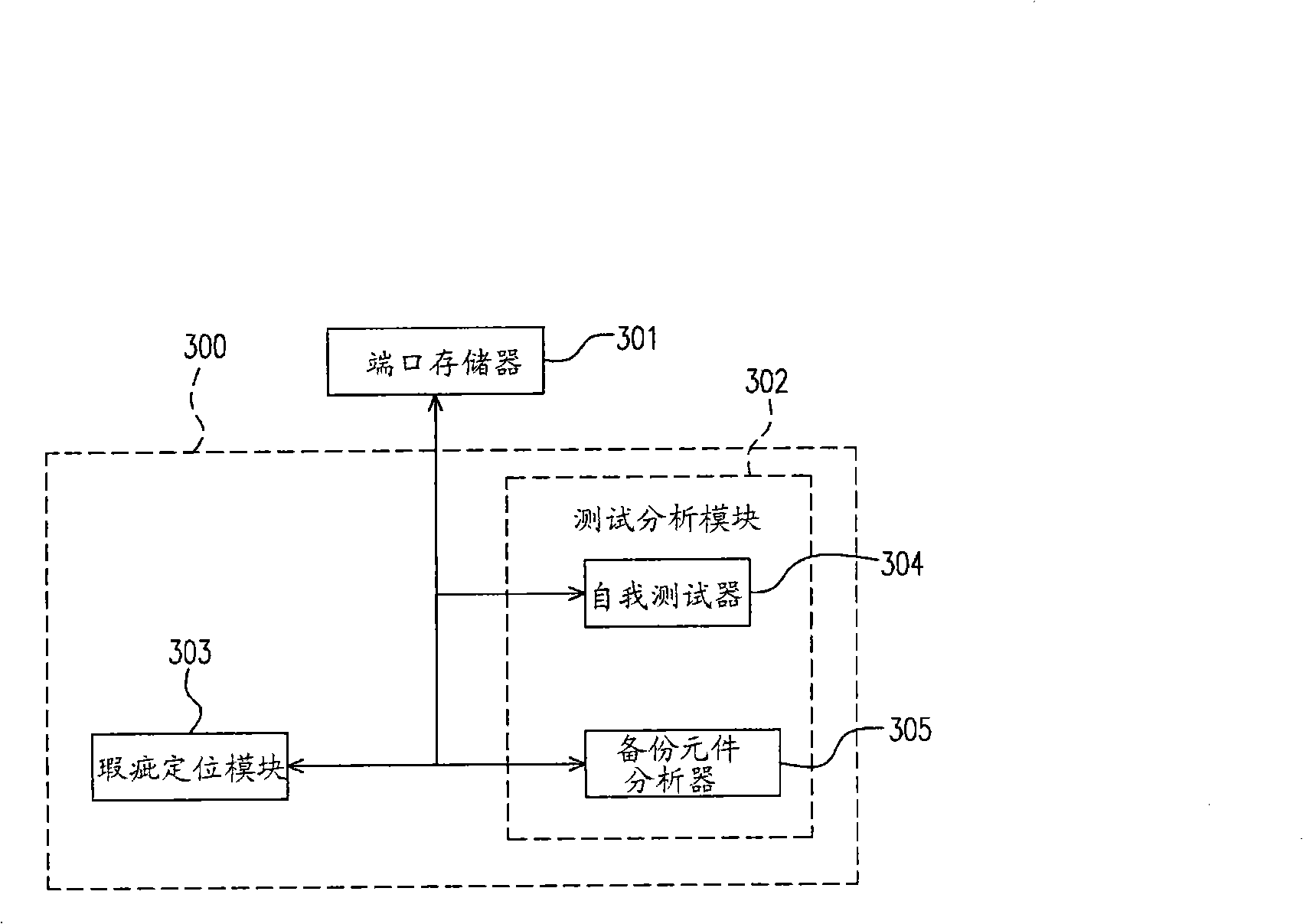

[0046] Please refer to the following instructions image 3 and Figure 4 . image 3 is a schematic diagram of a multi-port memory self-healing circuit 300 according to an embodiment of the present invention, Figure 4 It is a flow chart of the multi-port memory self-healing method executed by the self-healing circuit 300 . The multi-port memory self-repair circuit 300 includes a test analysis module 302 and a defect location module 303 , and the test analysis module 302 further includes a self-tester 304 and a backup component analyzer 305 . The repairable multi-port memory 301 , the self-tester 304 , the backup component analyzer 305 , and the defect location module 303 are coupled to each other.

[0047] Figure 4 The process starts from step 405. The self-tester 304 tests the repairable multi-port memory 301 to generate an error location at step 405 . In step 410, the backup component analyzer 305 judges whether the above-mentioned test generates a port-related error ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More