Chip packaging outer lead wire molding die

A technology for installing external leads and forming molds, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of easily damaged packaging blocks, etc., and achieve the effect of good coplanarity and good electrical connection characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

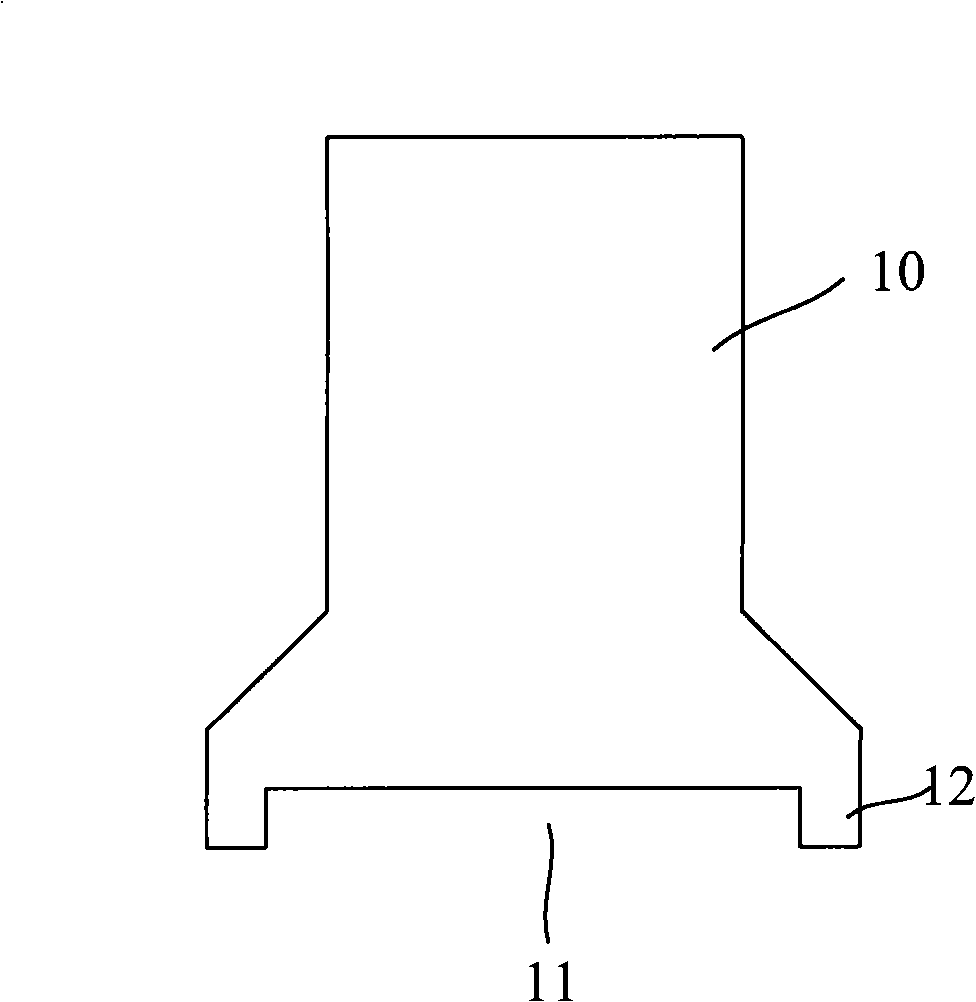

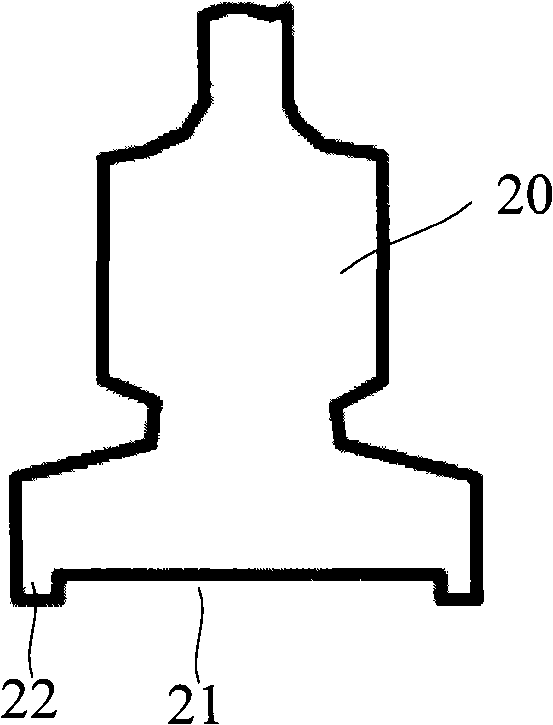

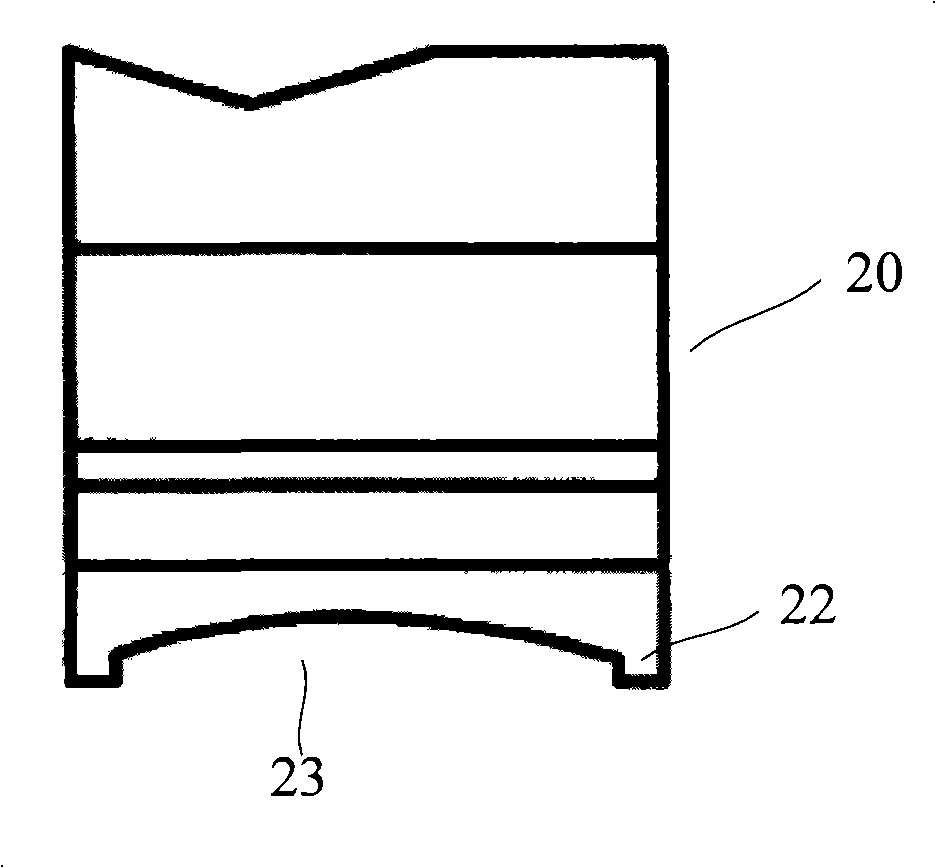

[0033] The specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0034] In order to achieve thin packaging, lead-on-chip packaging structure is adopted in the TSOP packaging process. After the chip is plastic-encapsulated, the thickness of the resin on the top and bottom of the chip is different, resulting in different shrinkage of the resin on the top and bottom of the chip during the cooling process after plastic packaging, resulting in the formation of TSOP packaging blocks. produce warping. This warpage leads to poor coplanarity of the outer leads when the outer leads are formed through the molding die and the stamping head after the chip is plastic-packed, which in turn causes the outer leads to be in contact with the PCB or other substrates when the TSOP package block is mounted. The solder joints on other substrates are not in good contact, or even open circuit, which may easily cause electrical ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| depth | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More