Multiplier, digital filter, signal processing device, synthesis device, synthesis program, and synthesis program recording medium

A technology of multipliers and multipliers, which is applied in the field of multipliers in which multipliers and multiplicands are multiplied, and can solve problems such as reducing circuit scale.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

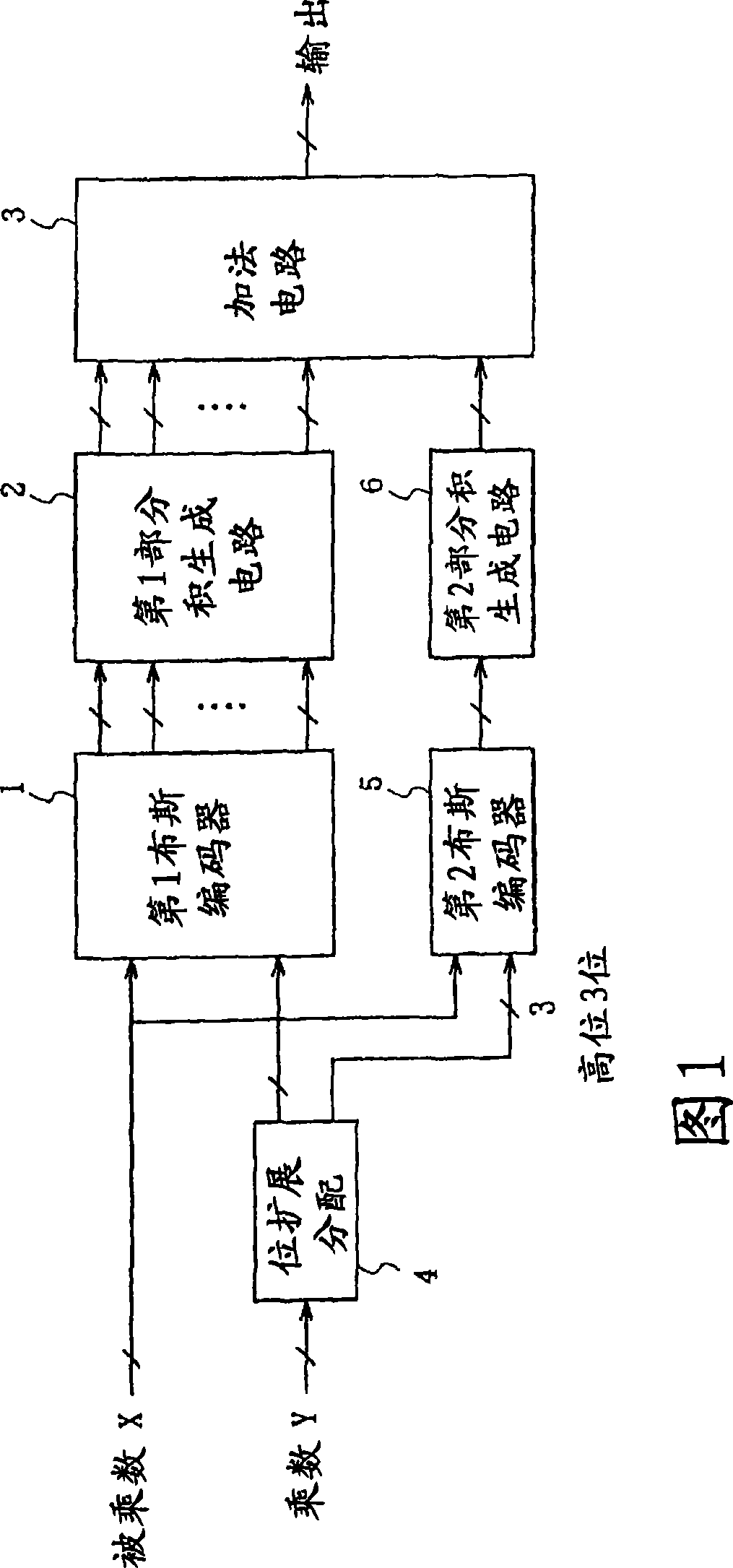

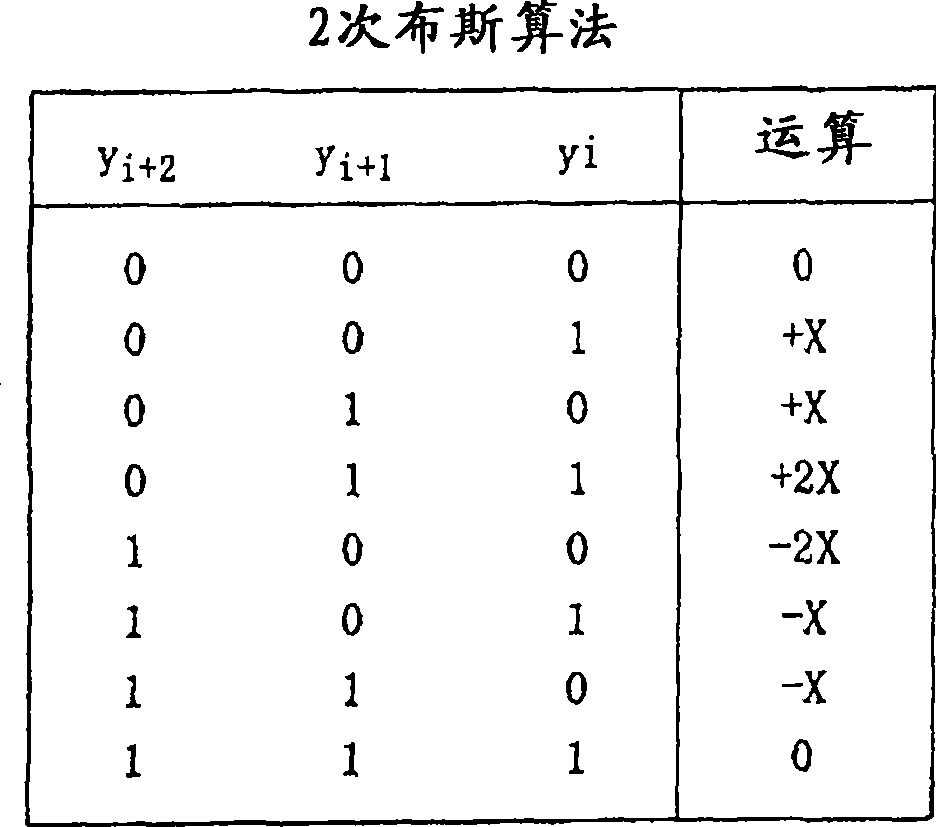

[0078] Hereinafter, a multiplier according to Embodiment 1 of the present invention will be described with reference to FIG. 1 .

[0079] FIG. 1 is a block diagram of a multiplier that receives an unsigned multiplier as an input according to the first embodiment. In Fig. 1, 1 is the first Booth encoder, 2 is the first partial product generation circuit using the output of the first Booth encoder 1 to generate the partial product, 5 is the second Booth encoder, and 6 is the first partial product generation circuit using the output of the first Booth encoder 1. 2. A second partial product generation circuit for generating a partial product from the output of the Booth encoder 5 . In addition, 3 is an adding circuit for adding the output of the first partial product generating circuit 2 and the output of the second partial product generating circuit 6, and 4 is bit-expanding the input multiplier and distributing it to the first Booth encoder 1 and 2 bit extension distribution ci...

Embodiment approach 2

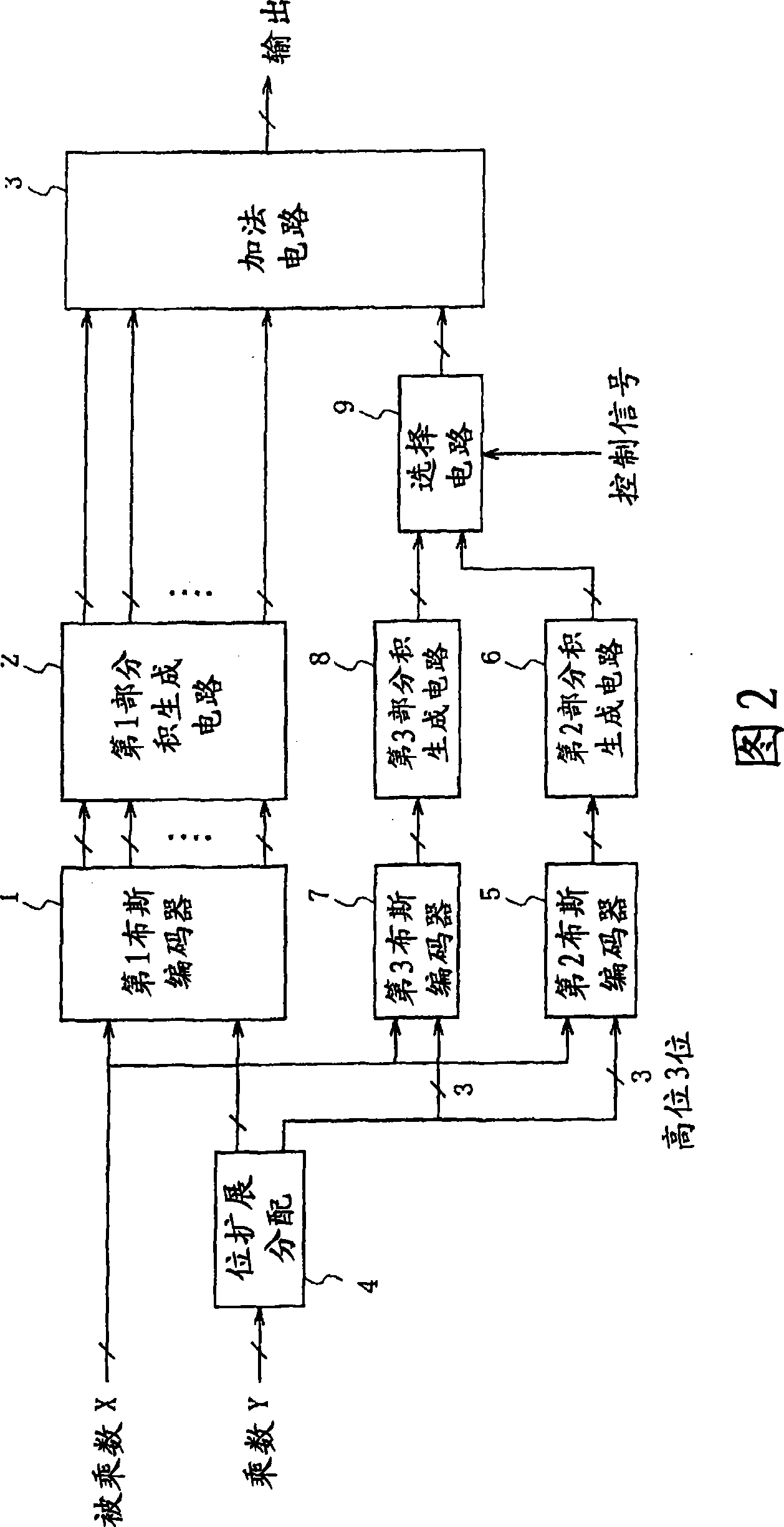

[0101] A multiplier according to Embodiment 2 of the invention will be described using FIG. 2 .

[0102] FIG. 2 is a block diagram showing a multiplier that receives an unsigned multiplier as an input according to the second embodiment. In FIG. 2 , the same symbols as those in FIG. 1 denote the same or corresponding parts. In addition, 7 is the third Booth encoder which encodes the input signal according to the same symbolization rule as the first Booth encoder, and 8 is the third part which uses the output of the third Booth encoder 7 to generate the partial product The product generating circuit 9 is a selection circuit for selecting and outputting either the output of the second partial product generating circuit 6 or the output of the third partial product generating circuit 8 .

[0103] In FIG. 2 , the difference from the multiplier of the first embodiment shown in FIG. 1 is that a third Booth encoder 7 , a third partial product generation circuit 8 , and a selection cir...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More