Systems and methods for forming integrated circuit components having matching geometries

A technology of integrated circuits and geometric shapes, applied in circuits, electrical components, electric solid devices, etc., can solve the problems of reducing efficiency, increasing the cost of integrated circuit devices, increasing cycle time and manpower, etc., to reduce cycle time and reduce geometry Shape difference, effect of increasing yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] refer to Figures 1 to 5 The present invention and its advantages are best understood by example embodiments wherein like numerals are used to indicate like and corresponding parts.

[0019] figure 1 A top view of an example semiconductor wafer 10 according to one embodiment of the invention is shown. Semiconductor wafer 10 may include a plurality of dies or chips 12, each including one or more integrated circuits including a plurality of integrated circuit components. Semiconductor wafer 10 may comprise a thin, circular sheet of monocrystalline semiconductor material suitable for use in the manufacture of semiconductor devices and / or integrated circuits. Semiconductor wafer 10 may include any suitable number of dies 12 , which may be physically separated from each other after integrated circuits are formed in each die 12 .

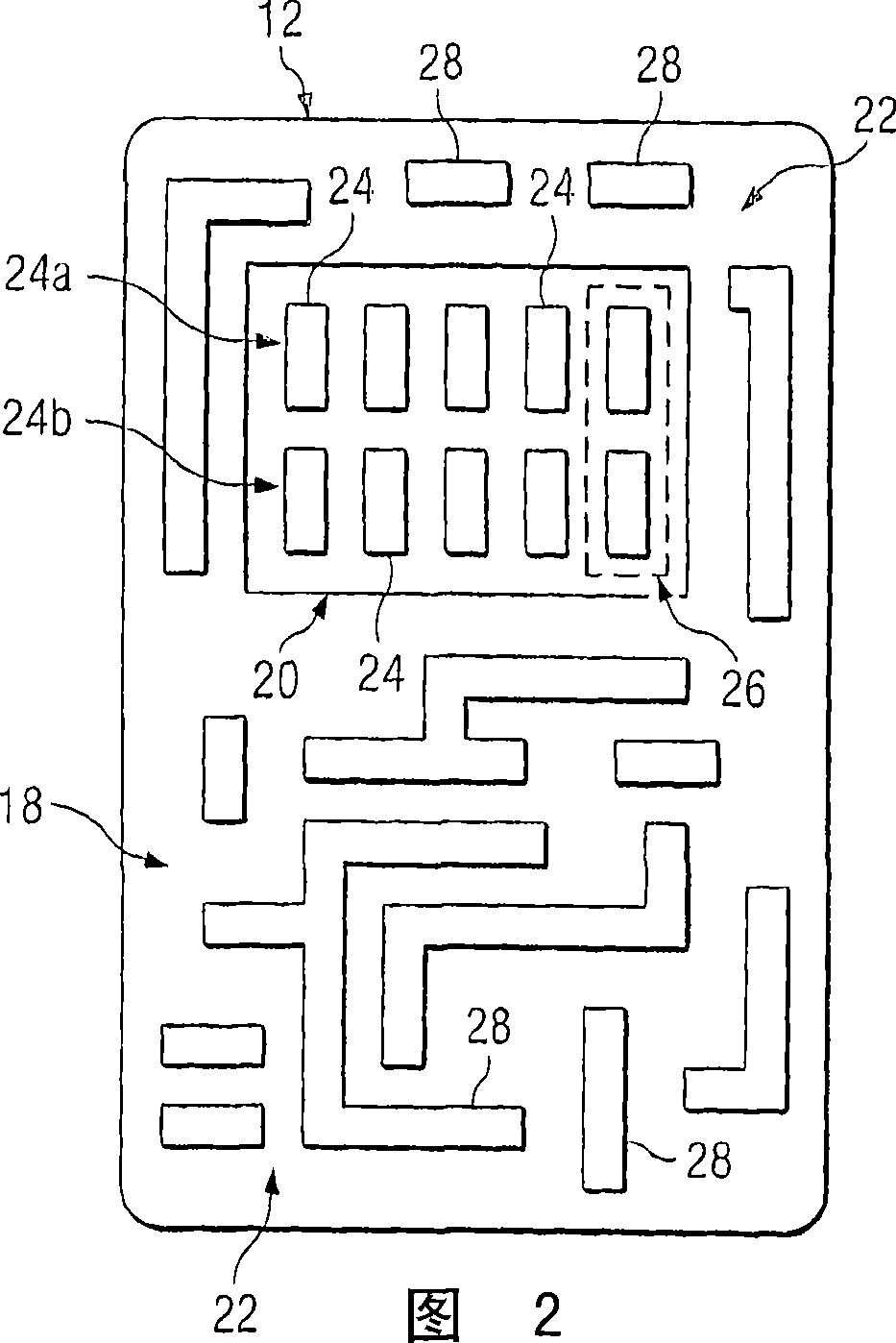

[0020] Figure 2 shows a single die 12 of a semiconductor wafer 10, which may include integrated circuit components formed in accordance with an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More