Control method and bus interface of RAM use right

A technology of bus interface and usage rights, which is applied to the control method of RAM usage rights and the field of bus interfaces, can solve the problems of unable to meet the requirements of communication speed and difficult to realize strict control of communication timing, so as to improve communication speed, increase speed, optimize The effect on overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Hereinafter, the method for controlling the use of RAM and the implementation of the bus interface of the present invention will be described in detail through specific embodiments in conjunction with the drawings.

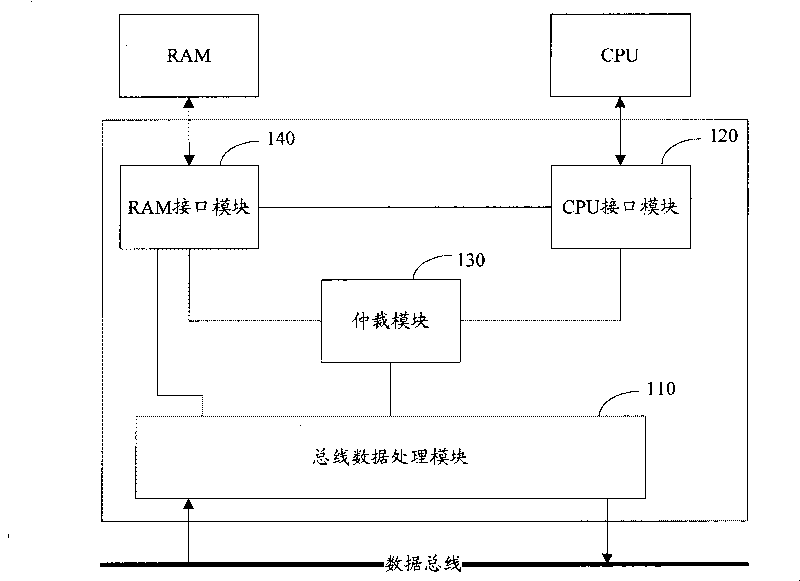

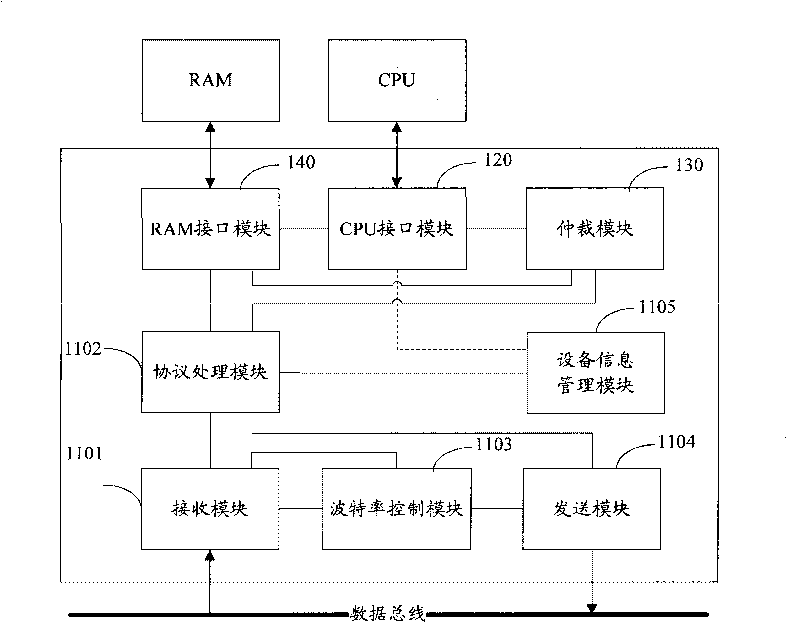

[0046] figure 1 It is a schematic diagram of the structure of the bus interface of the present invention, such as figure 1 As shown, the bus interface includes: a bus data processing module 110, a CPU interface module 120, an arbitration module 130, and a RAM interface module 140; among them,

[0047] The bus data processing module 110 is used to receive data from the bus, and when determining the use of RAM according to the received data, send an application for the right to use RAM to the arbitration module 130; also used to when the arbitration module 130 determines that the bus data processing module 110 obtains RAM When using the right, the RAM interface module 140 is used to access data with the RAM; it is also used to output the data read from the RAM to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More