Structure for testing reliability analysis of integrated circuit inner layer dielectric

A technology of integrated circuits and test structures, applied in circuits, electrical components, electric solid devices, etc., can solve problems such as easy burning of metal wires and abnormal testing, and achieve the effect of reducing the possibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to better understand the technical solutions provided by the present invention, the following will be further described in conjunction with specific examples of the present invention, but they do not limit the present invention.

[0025] One of the preferred embodiments of the present invention is described in detail below to illustrate the concept of the present invention and to show the more important inventive features of the present invention.

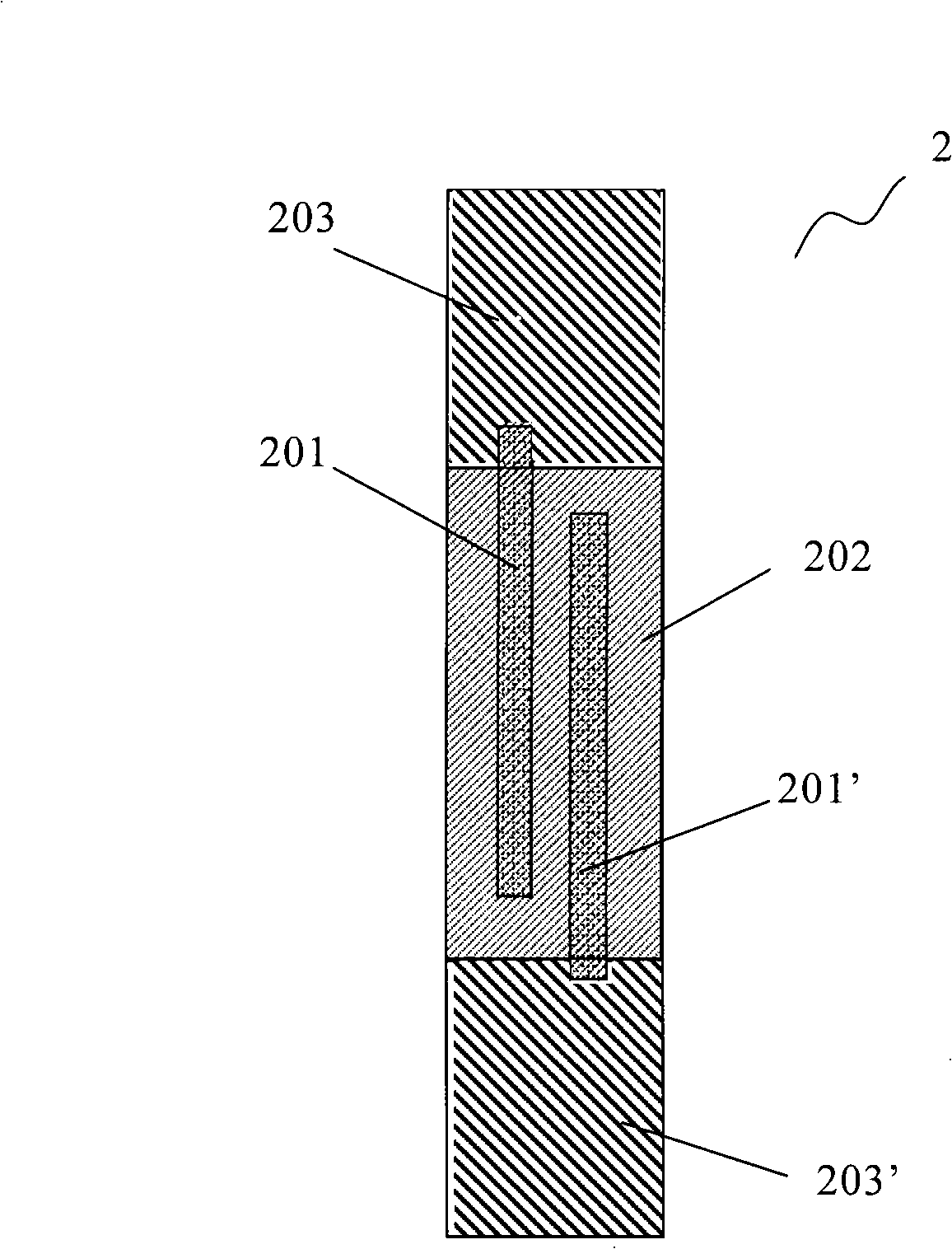

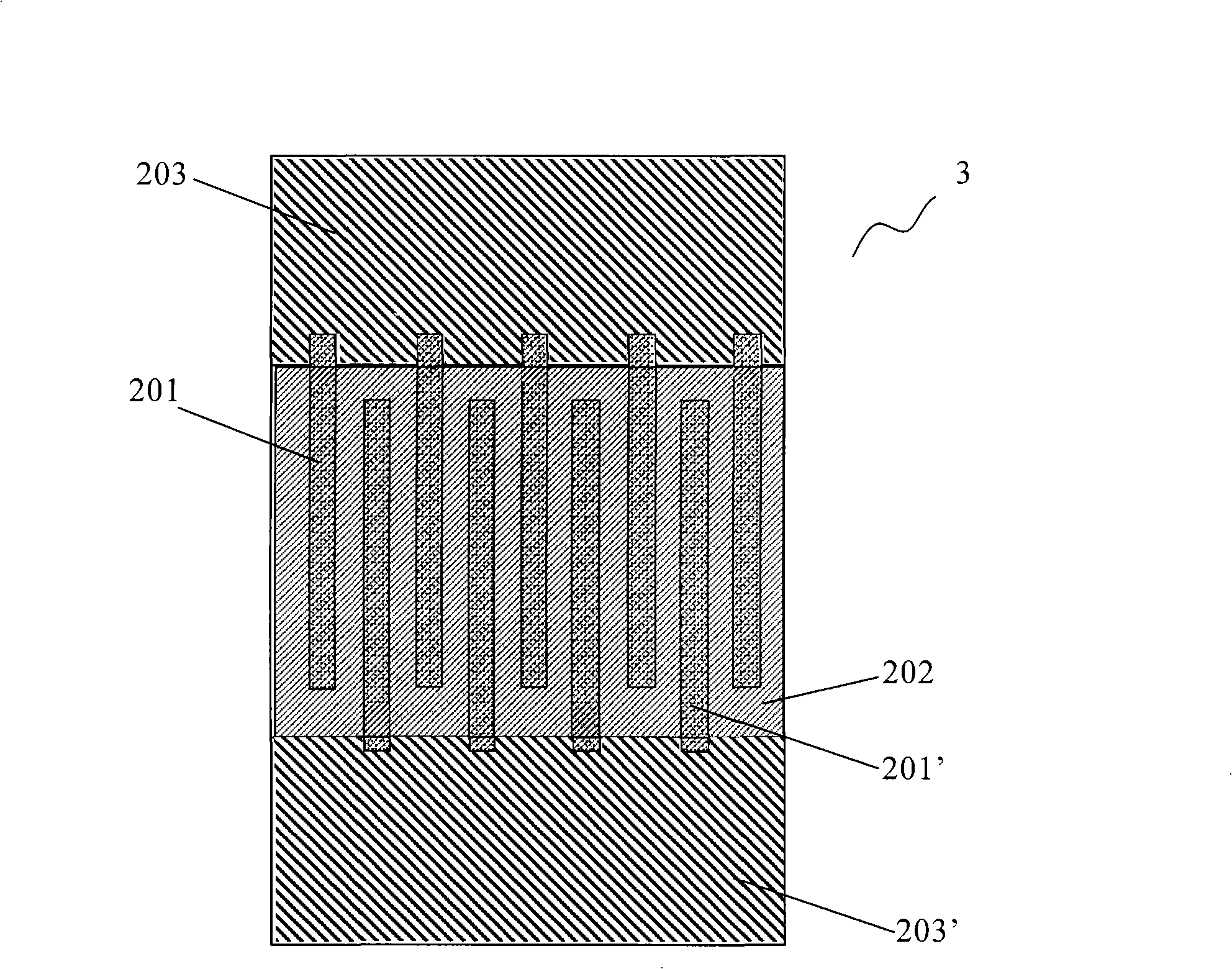

[0026] figure 2 It is a schematic structural diagram for testing the reliability analysis of the inner layer dielectric of the integrated circuit for a specific embodiment of the present invention, such as figure 2 As shown, the test structure 2 consists of:

[0027] The metal wire structures 201 and 201', as components of the reliability test structure, are equivalent to metal wires used to form circuits in integrated circuit devices. Therefore, the design specifications of the metal structures 201 and 201', th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More