Virtual test bus circuit for network-on-chip system and test method thereof

A technology of virtual testing and network-on-chip, applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve the problems that the connection lines are not effectively used, the test time cannot be effectively reduced, etc., and it is easy to test data broadcasting, eliminate The effect of redundant test time and good flexibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

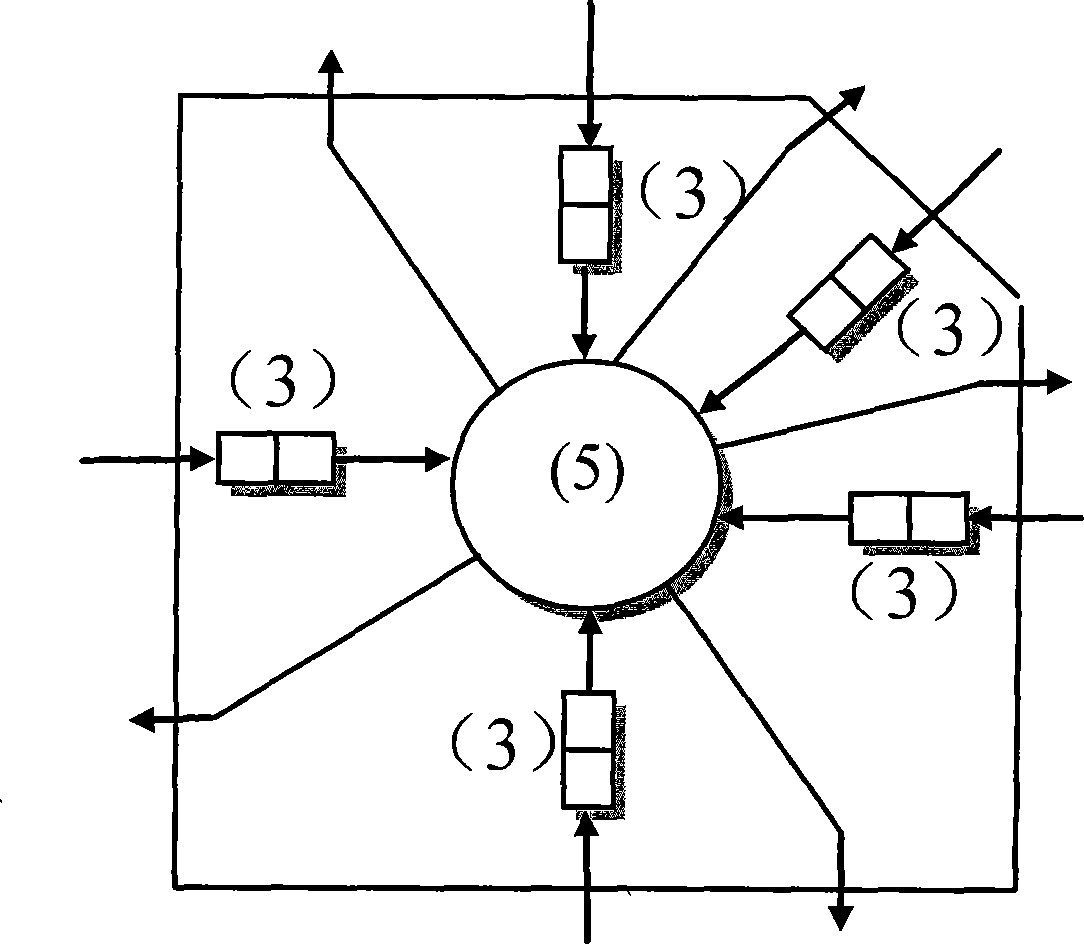

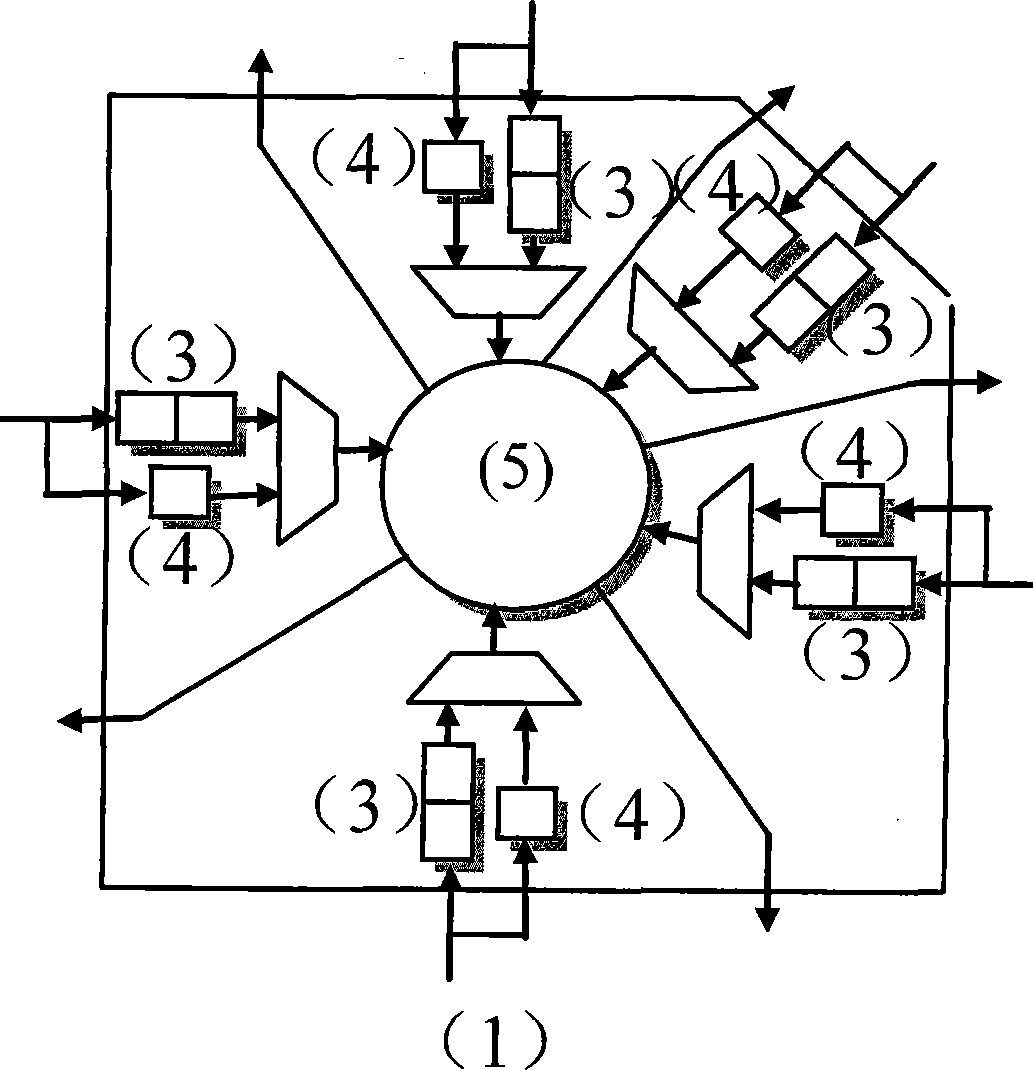

[0056] Such as Figure 5 As shown, the figure is an example of a router module after design for testability, in which modules 4, 7, and 9 are modules added by design for testability.

[0057] The router contains 5 sets of input and output ports, namely east, south, west, north, and core. Corresponding to each group of input ports, the system is configured with an input control circuit module 3 and a corresponding testability module—the input control circuit bypass module 4 . According to the test enable signal ten, the multiplexer module 9 selects the output of the input control circuit module 3 as the final output signal in the working state, and selects the output of the input control circuit bypass module 4 as the final output in the test state. Signal.

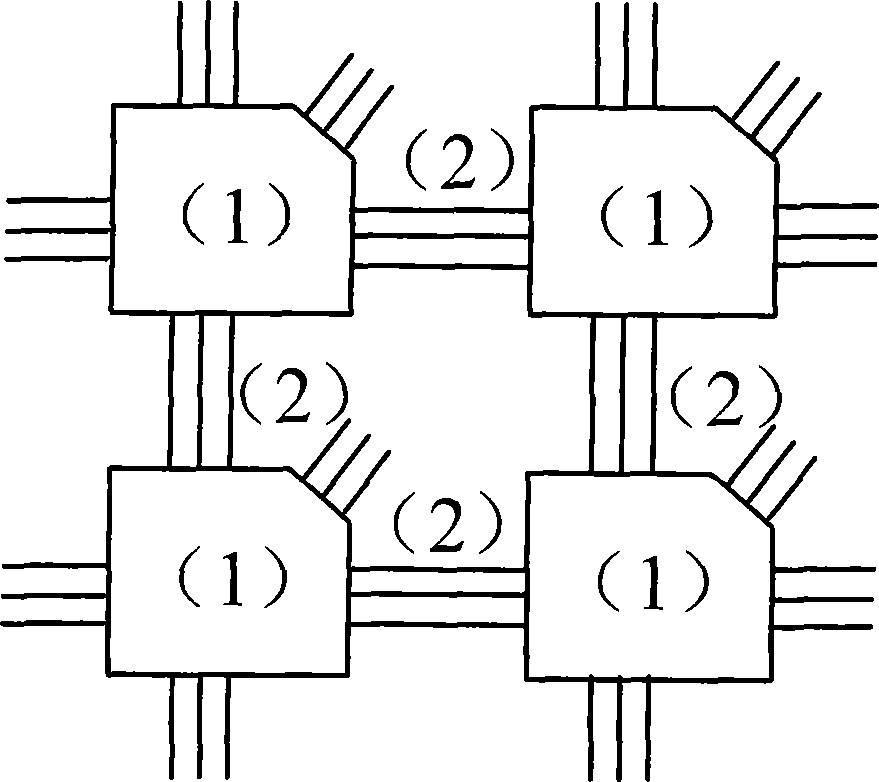

[0058] Each router module includes a routing logic module 6. In order to generate a virtual test bus, a test control module 7 is added to the routing logic module 6 in this embodiment. According to the values of the t...

Embodiment 2

[0062] The invention also provides a test method based on the virtual test bus circuit for the on-chip network system. The main design of this test method has two aspects, on the one hand, by generating routing control signals by the information forwarding module 5 during testing, and connecting each router module 1 according to the routing control signals, forming a plurality of virtual test buses, thereby achieving The purpose of improving the utilization efficiency of original connection resources of the network-on-chip system. Another aspect is to eliminate the redundant time caused by the protocol by gating the input control circuit bypass module 4 during the test.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More