Memory access control device

A memory access and memory controller technology, applied in memory systems, instruments, memory address/allocation/relocation, etc., can solve problems such as inability to use memory, and achieve the effect of shortening memory access delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

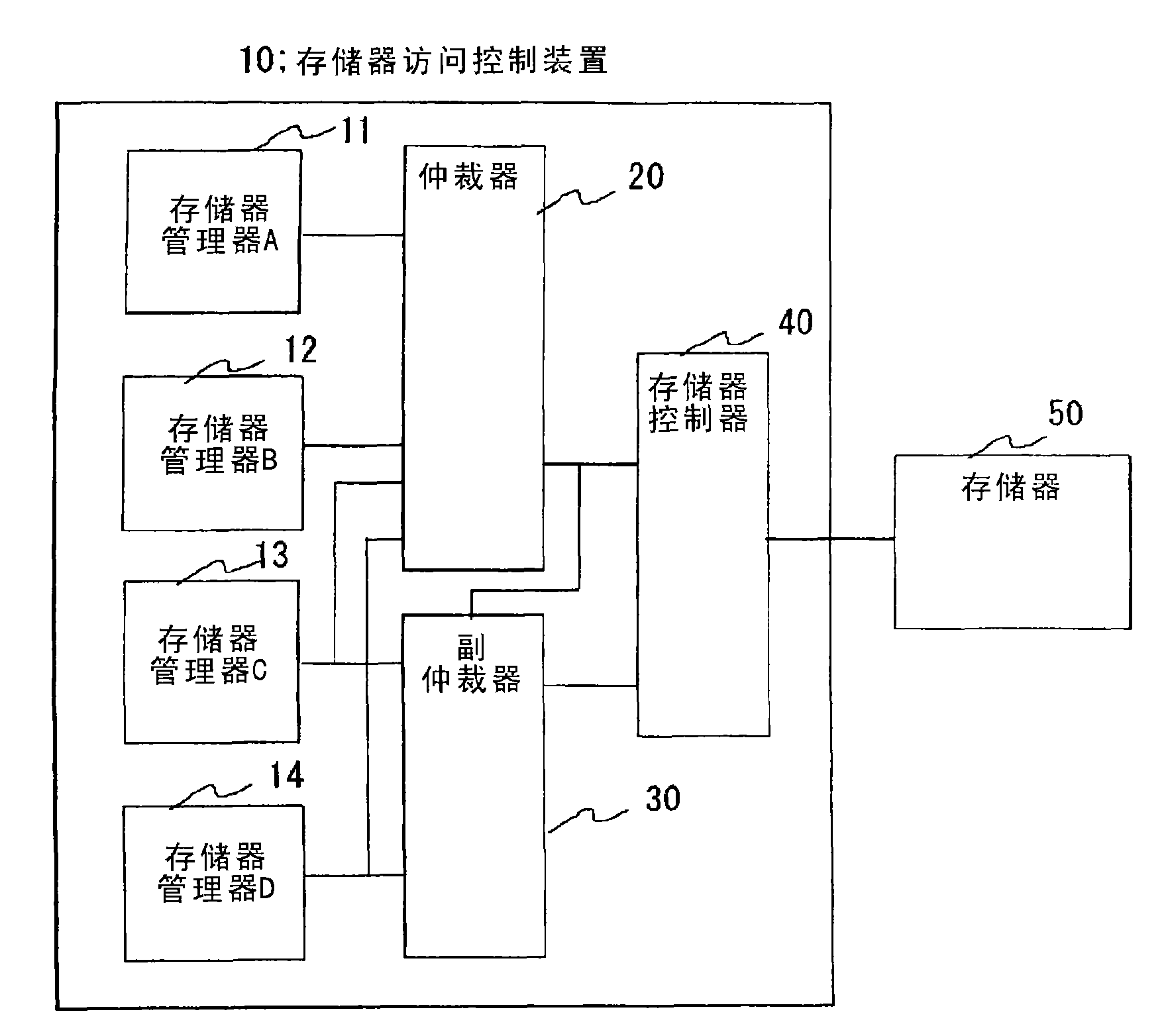

[0065] figure 1 is a diagram showing the structure of the first embodiment of the present invention. This embodiment includes a memory access control device 10 and a memory 50 with a plurality of storage banks. The memory access control device 10 includes: memory managers A (11), B (12); C (13), D (14); arbiter (20); secondary arbiter (30); memory controller 40.

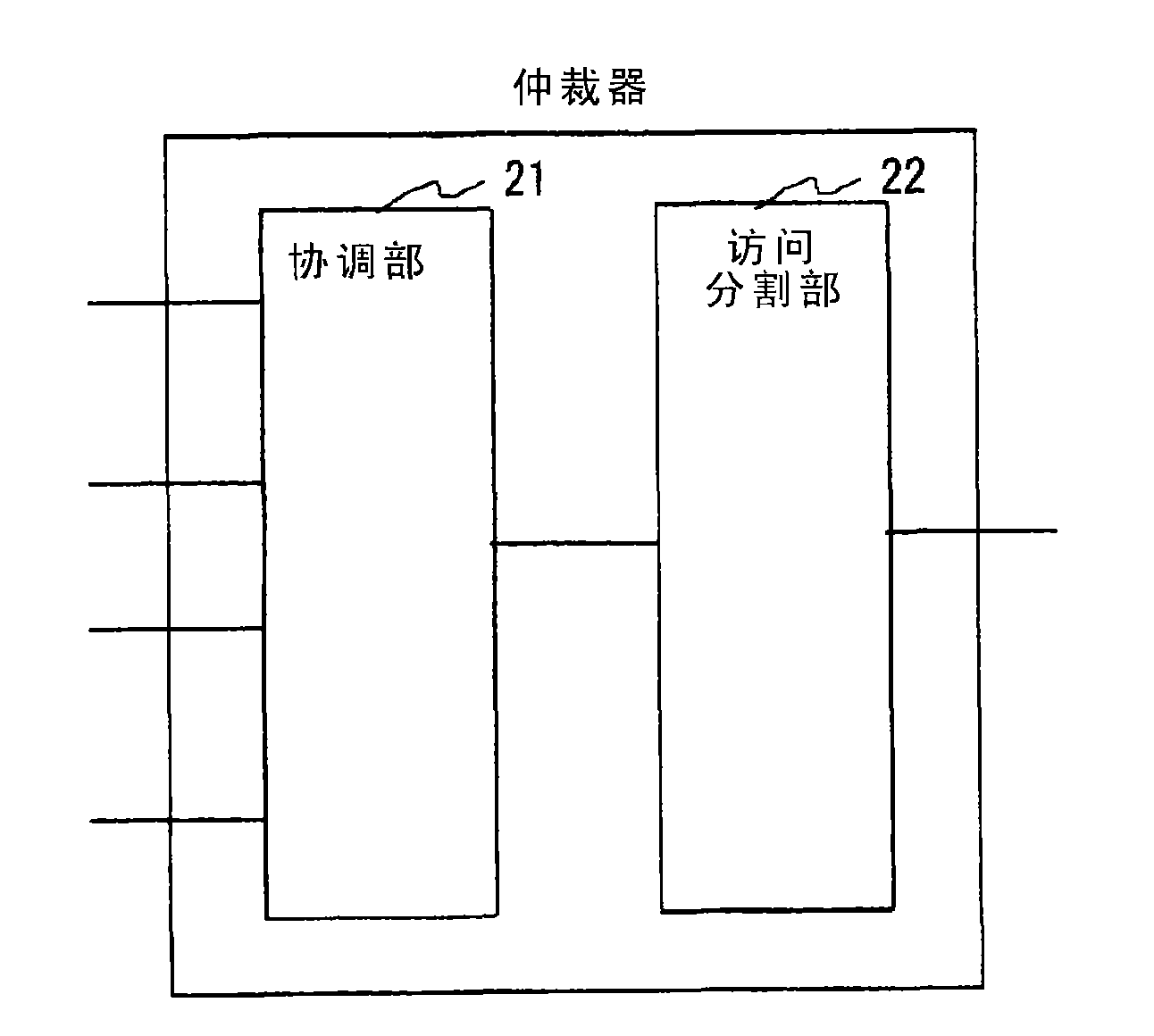

[0066] figure 2 is showing figure 1 A diagram of an example of the structure of the arbiter 20. refer to figure 2 , in this embodiment, the arbiter 20 includes a coordination unit 21 and an access division unit 22, wherein the coordination unit 21 selects a memory manager from a plurality of memory managers 11-14, and the access division unit 22 When the access request consists of multiple burst lengths, the access request is divided into short burst lengths.

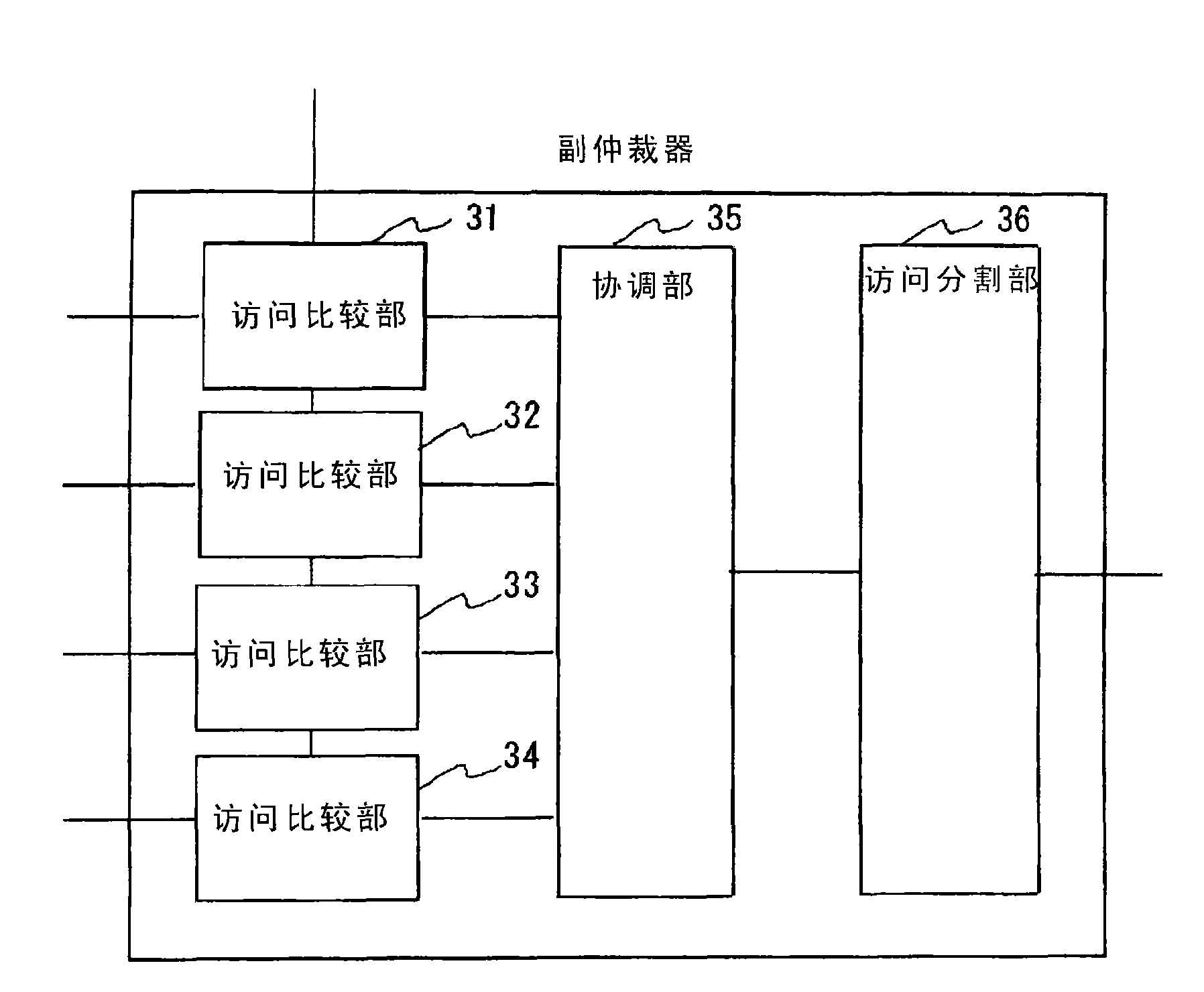

[0067] image 3 is showing figure 1 A diagram of an example of the structure of the sub-arbiter 30. refer to image 3 , in this embodiment, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More