QC-LDPC (Quasi-Cyclic Low-Density Parity-Check) code decoder and implementation method thereof

An implementation method and decoder technology, applied in the field of digital communication

- Summary

- Abstract

- Description

- Claims

- Application Information

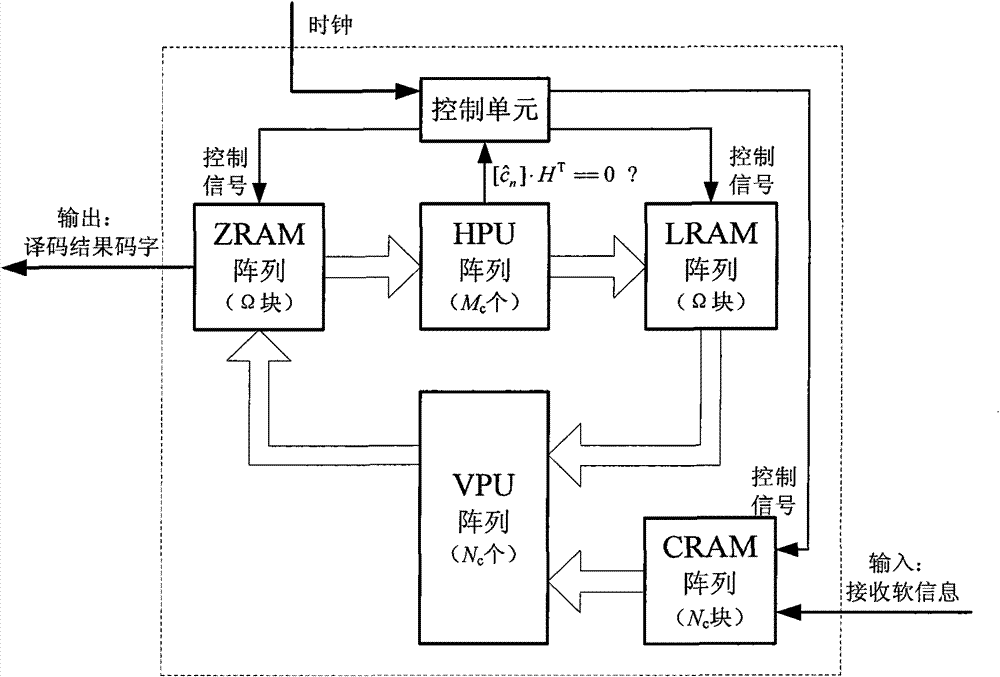

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

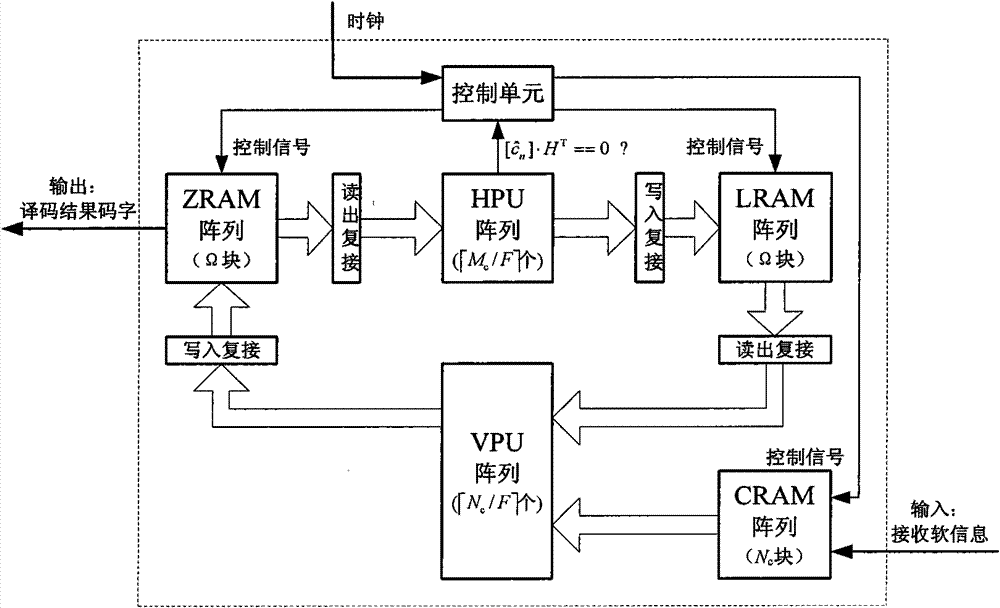

[0140] In this embodiment, the combination factor F 1 =F 2 =2, and the technical solution of the present invention is described by taking the construction of XRAM-C according to CSMG-H as an example.

[0141] Such as Figure 8 As shown, it represents a simple H matrix with a quasi-cyclic structure, which is not an H matrix of an actual QC-LDPC code, and is only used for the QC-LDPC code decoder provided by the present invention and its implementation method The specific implementation will be described in detail. The H matrix is composed of 4 row vectors and 6 column vectors, in which the striped block is CSM, and the colorless block is ZSM, and the CSM is numbered i-j according to its row and column positions, i represents the row, and j represents the column.

[0142] Multiplexing group construction steps: first construct HSG, construct the 1st and 2nd row vectors into HSG1, and the 3rd and 4th row vectors into HSG2; then build VSG, construct the 1st and 2nd column vect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More