Steady state phase-locking error-free phase locking system and phase locking method

A phase-locking error and phase-locking technology, which is applied to the phase-locking system and the phase-locking field where the steady-state phase-locking error is zero, can solve the problems of difficult implementation and complicated circuits.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

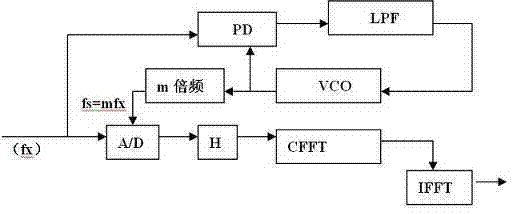

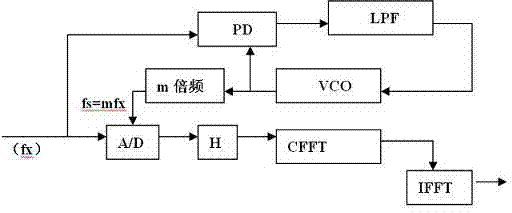

[0070] 1. Set the frequency of the input signal X(t) as fx=250kHz, the amplitude as a, and the initial phase as φx. m=4, N=8, the input signal is divided into two routes, one to the phase-locked loop, and the other to the A / D conversion. After the first road is phase-locked, its output enters the 4 frequency multiplier, and 4fx=fs is obtained as the sampling signal;

[0071] 2. The A / D output is a digital signal sampled at 1MHz, which is transformed into a complex signal by "H" (Hilbert);

[0072] 3, utilize formula (3) to obtain N / m=2, promptly the output of No. 2 filter is:

[0073] F ( N / m ) = F ( 8 / 4 ) = F ( 2 ) = Σ n = 0 7 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More