On-line two-dimensional region management and task setting method of dynamically reconfigurable field programmable gate array (FPGA)

A task and area technology, applied in the field of reconfigurable computing research, to achieve the effect of efficient search

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

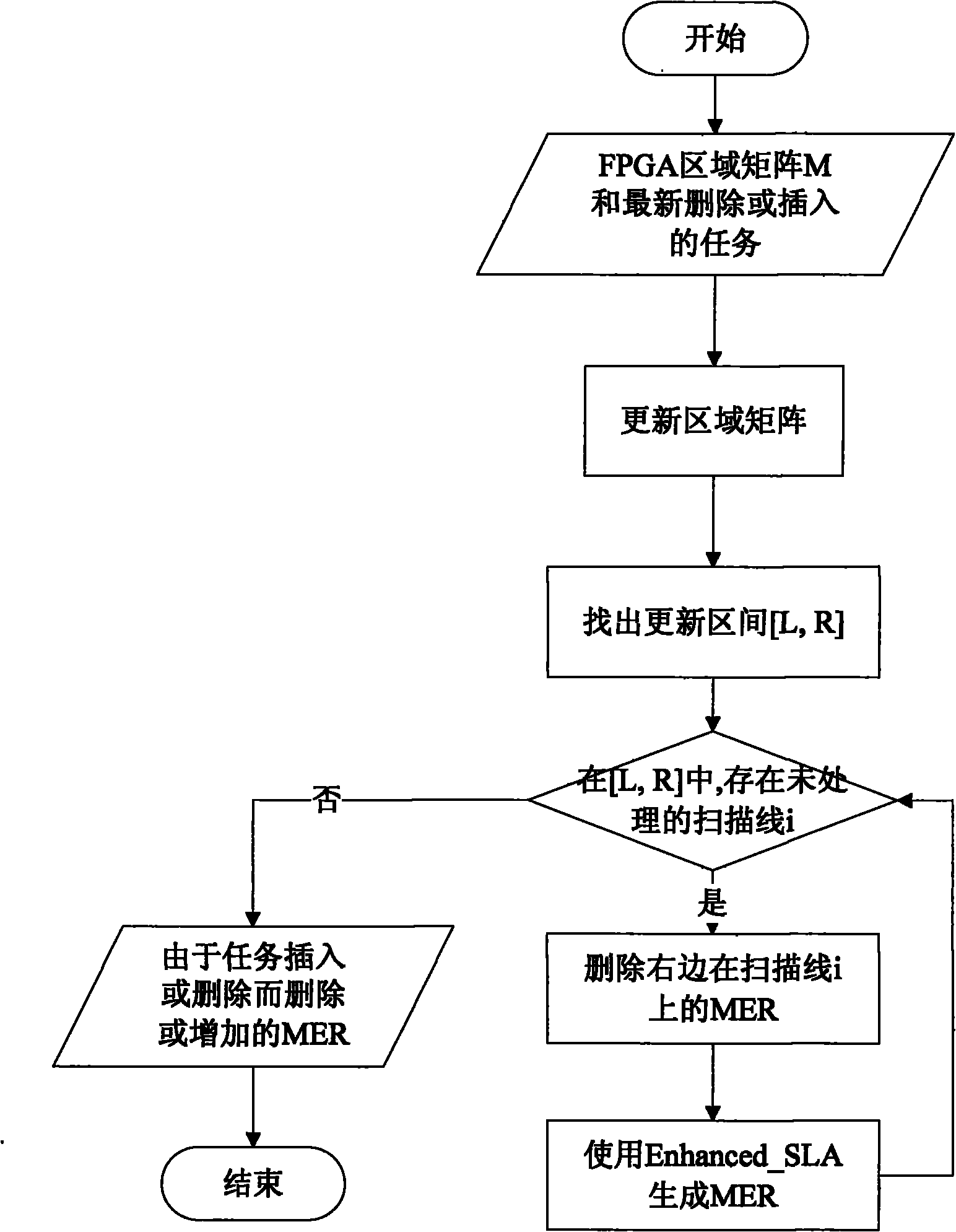

[0062] Update the area matrix M;

[0063] Find out the update interval [L, R], that is, when the hardware task is added or deleted, the range of the column where the scan line needs to be re-executed;

[0064] Determine whether there are unprocessed scanlines in [L, R]?

[0065]If there is an unprocessed scanline i, use the improved scanline algorithm to generate a very large empty rectangle on the scanline i, and return to the step of judging whether there are unprocessed scanlines in [L, R].

[0066] If there are no unprocessed scanlines, output a very large empty rectangle that was deleted or added due to task insertion or deletion.

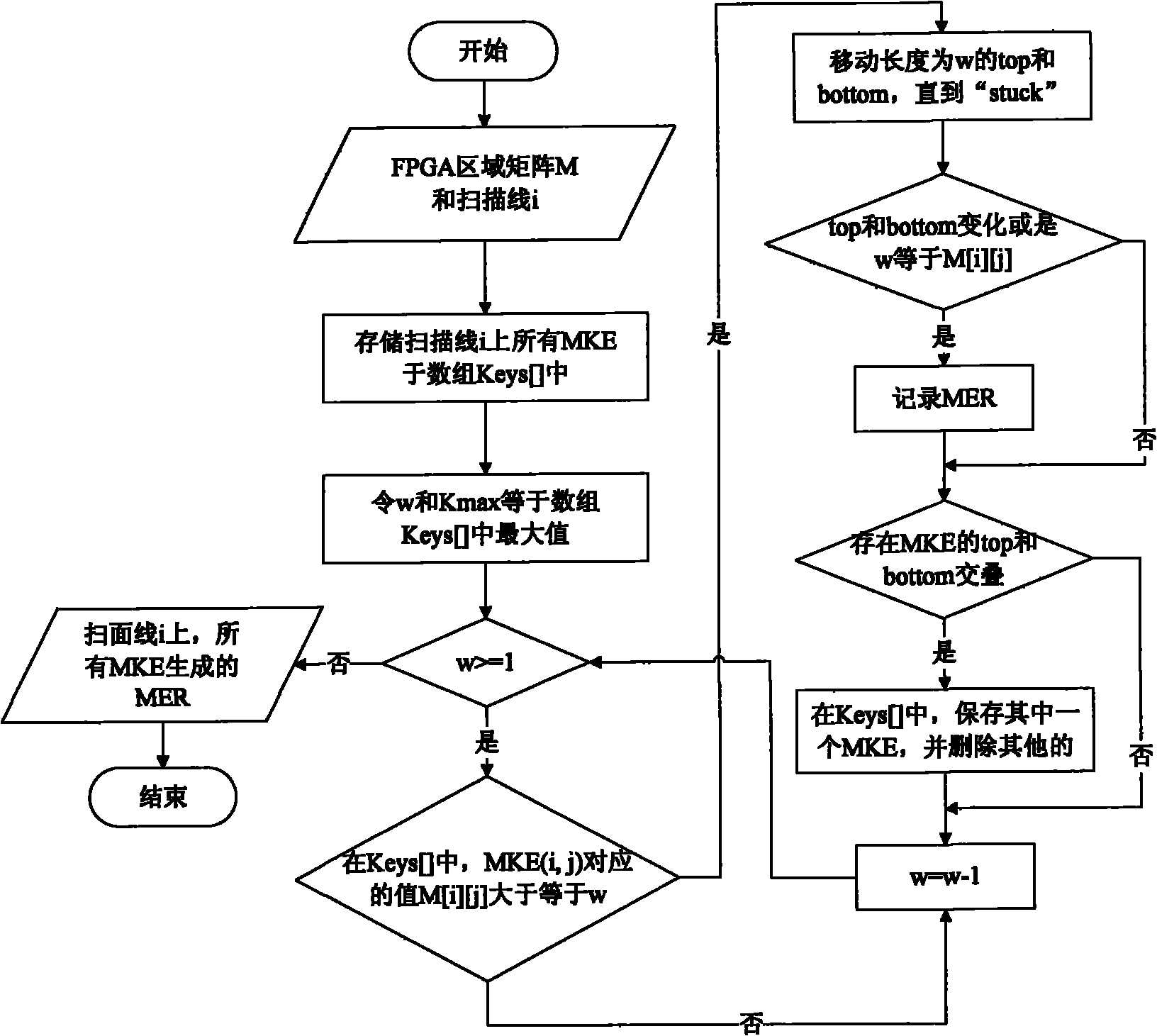

[0067] The improved scan line algorithm comprises the following steps:

[0068] Input FPGA area matrix M, and input scan line i;

[0069] Store all maximum key elements (MKE) on the scan line i in the array Keys[];

[0070] Let variables w and K max Equal to the maximum value in the array Keys[];

[0071] Judging whether w≥1 holds true? ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More