System and method of controlling power consumption in a digital phase locked loop (DPLL)

A phase-locked loop and control signal technology, applied in the field of phase-locked loops, can solve the problem of spending a lot of time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

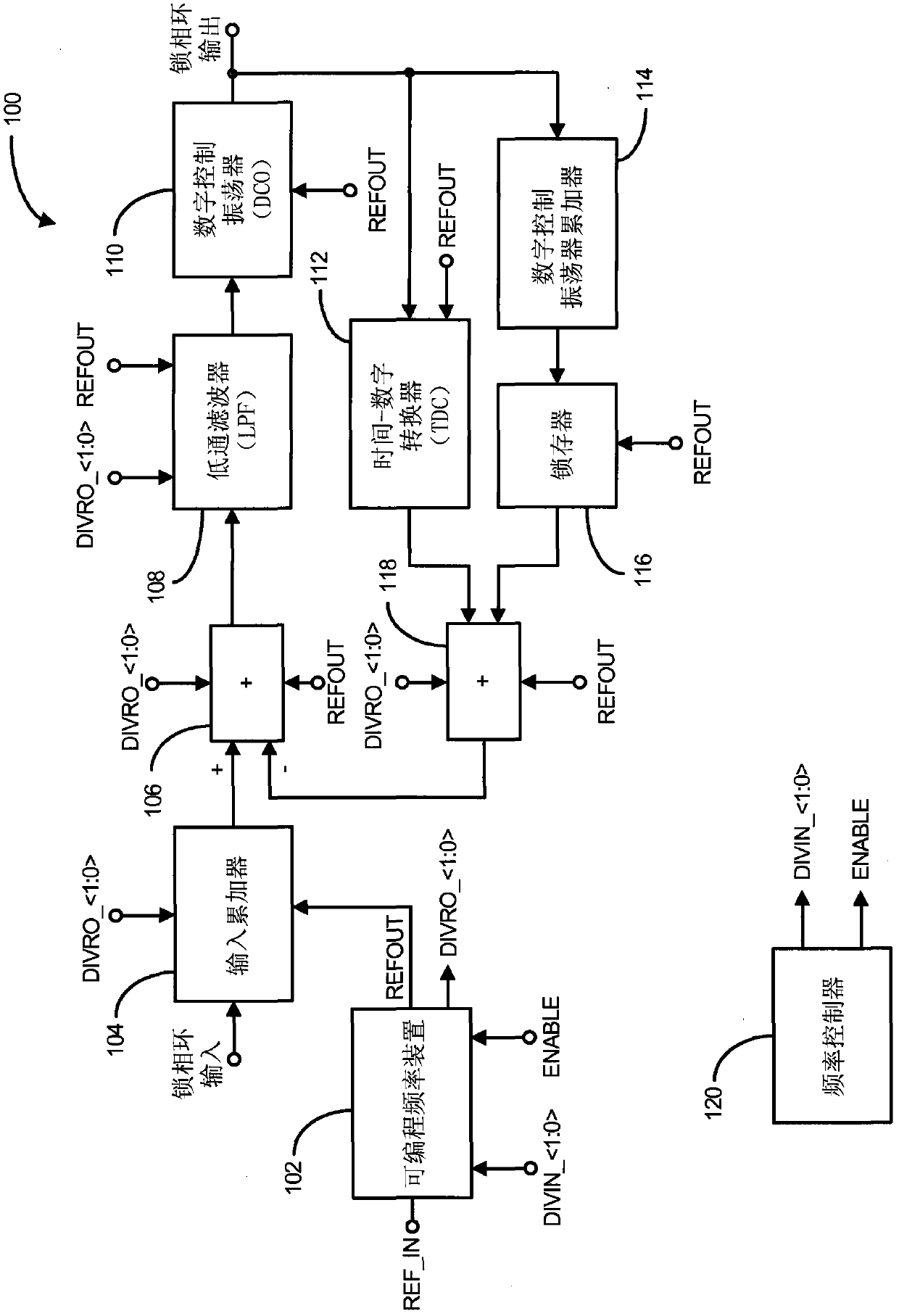

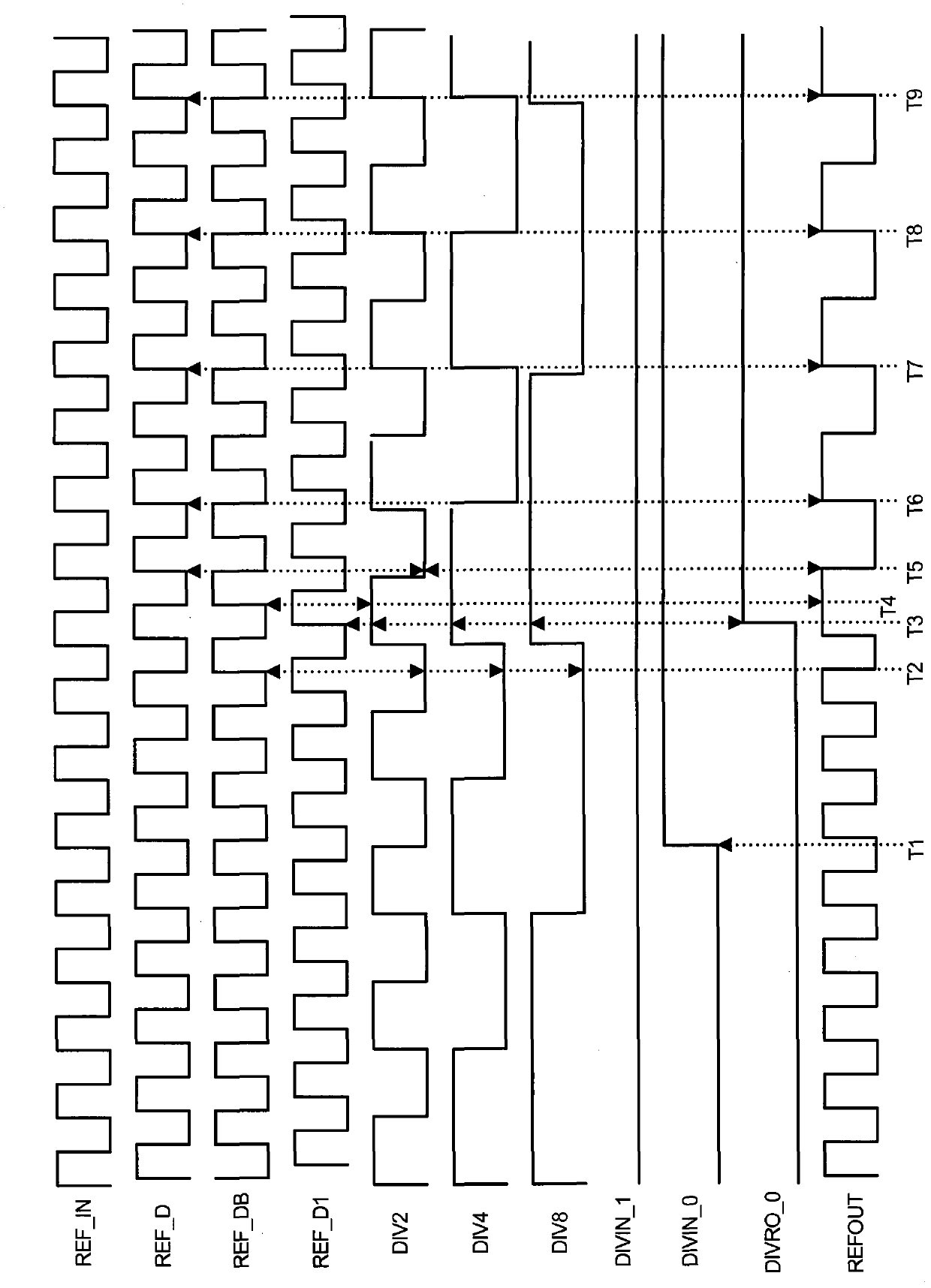

[0014] figure 1 A block diagram of an exemplary digital phase locked loop (DPLL) 100 is illustrated in accordance with an aspect of the invention. In summary, the DPLL allows programmability of the frequency of the reference clock for power consumption purposes without significantly affecting the loop control of the DPLL. The DPLL performs this process by ensuring that the timing of the reference clock's trigger edge does not substantially change when the reference clock frequency changes. As previously discussed, the DPLL can be placed in a low power mode when the frequency of the reference clock is substantially reduced. Conversely, the DPLL can be placed in a high power mode when the frequency of the reference clock is substantially increased.

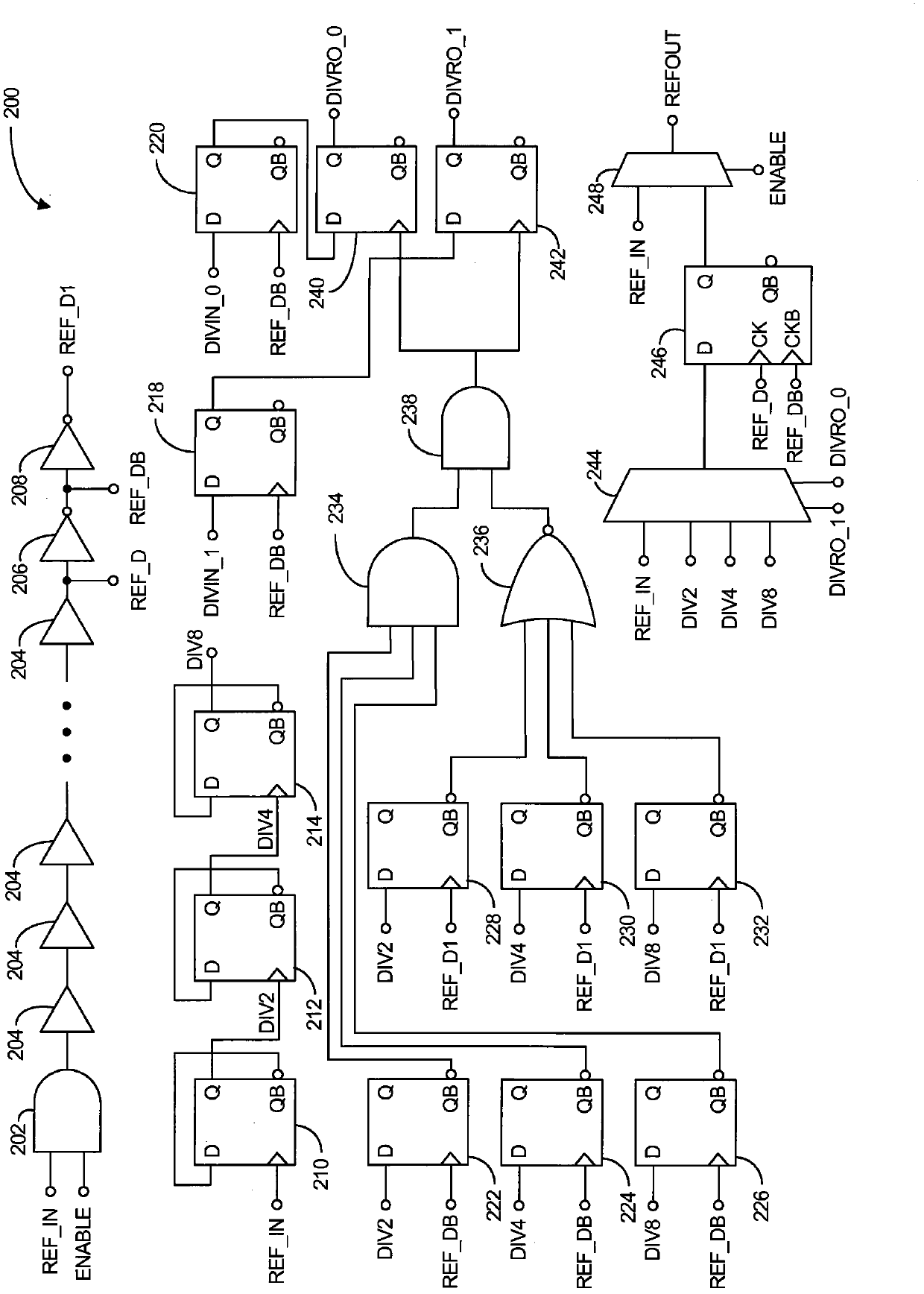

[0015] Specifically, a DPLL includes a programmable frequency device 102, an input accumulator 104, a first summing device 106, a low-pass filter (LPF) or loop filter 108, a digitally controlled oscillator (DCO) 110, a time-to-dig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com