Pulse density modulator for time division-synchronization code division multiple access (TD-SCDMA) and 4G terminal

A TD-SCDMA and pulse density modulation technology, which is applied in the field of pulse density modulators, can solve the problems of slow filter response speed and long modulation period, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

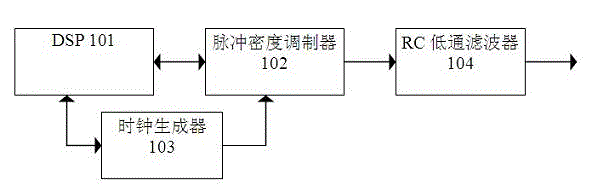

[0080] Example 1: figure 1 It is a block diagram of the pulse density modulation system proposed in this design for TD-SCDMA, Beyond 3G, and 4G terminals. The pulse density modulation system consists of the following components:

[0081] (1) Controller with DSP as the core (No. 101)

[0082] (2) Pulse Density Modulator PDM (102)

[0083] (3) Clock generator (103)

[0084] (4) Pulse density modulator off-chip RC low-pass filter (104)

[0085] Wherein, the DSP 101 provides a control signal for the pulse density modulator PDM 102 to control the level amplitude of the output signal of the pulse density modulator PDM 102 and the refresh rate of the output signal. The clock generator 103 provides a working clock signal for the pulse density modulator PDM 102 . An off-chip RC low pass filter 104 is then used to convert the output of the pulse density modulator PDM 102 into an analog signal.

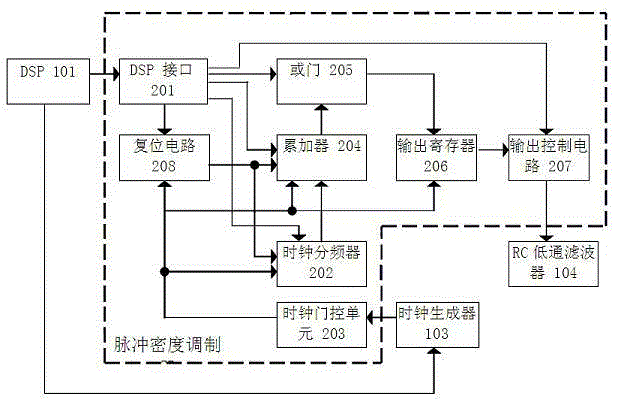

[0086] In the above-mentioned pulse density modulation system, the pulse density modul...

Embodiment 2

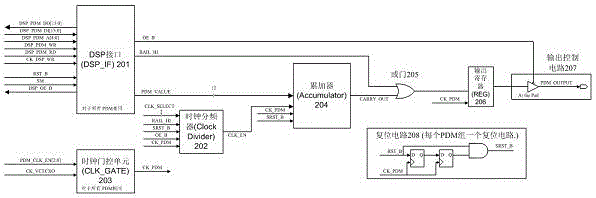

[0104] Embodiment 2: The relationship between PDM102 and the external and internal detailed input and output signals, such as image 3 shown.

[0105] The input and output signals of the DSP interface 201 are shown in Table 1.

[0106] The input and output signals of the clock gating unit 203 are shown in Table 2.

[0107] The input and output signals of the accumulator 204 are shown in Table 3.

[0108] The input and output signals of the clock divider 202 are shown in Table 4.

[0109] The input and output signals of the OR gate 205 are shown in Table 5.

[0110] The input and output signals of the output control circuit 207 are shown in Table 7.

[0111] The input and output signals of the reset circuit 208 are shown in Table 8.

Embodiment 3

[0112] Embodiment 3: PDM 102 outputs logic 1 and logic 0. Its output is passed through an analog low-pass off-chip filter to generate an analog value. When it outputs a high-level signal, the voltage is very close to the power supply voltage Vcc (3.3V in this design), and when it outputs a low-level signal, the voltage is very close to the ground GND voltage.

[0113] PDM 102 should have sufficient resolution to perform the above tasks. Currently, we expect 12-bit resolution. Also, the PDM 102 can output from V L to V H (where V L is the voltage corresponding to a logic low level, V H is the voltage corresponding to the logic high level) all voltage values in the range. At the same time, the output of the PDM 102 can also be set to a high-impedance state Hi-Z (ie, the PDM output is set to output prohibition. Output prohibition is only performed on the output pin).

[0114] The refresh rate of PDM 102 can be set by DSP 101 using DSP software / firmware, with faster r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More