Method and system for information interaction and resource distribution of multi-processor core

A multi-processor core and information interaction technology, applied in resource allocation, electrical digital data processing, instruments, etc., to achieve the effect of ensuring information exchange

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

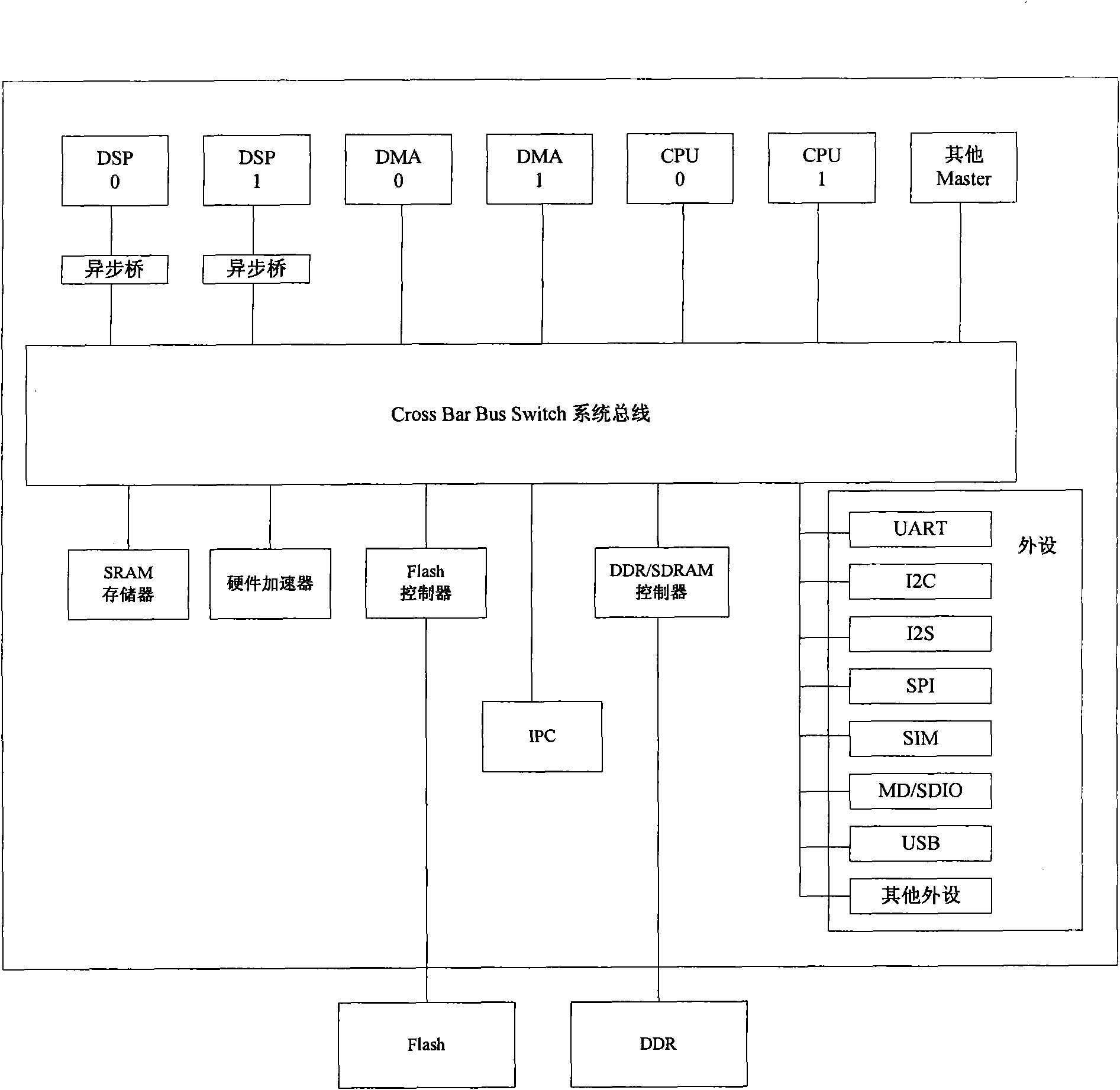

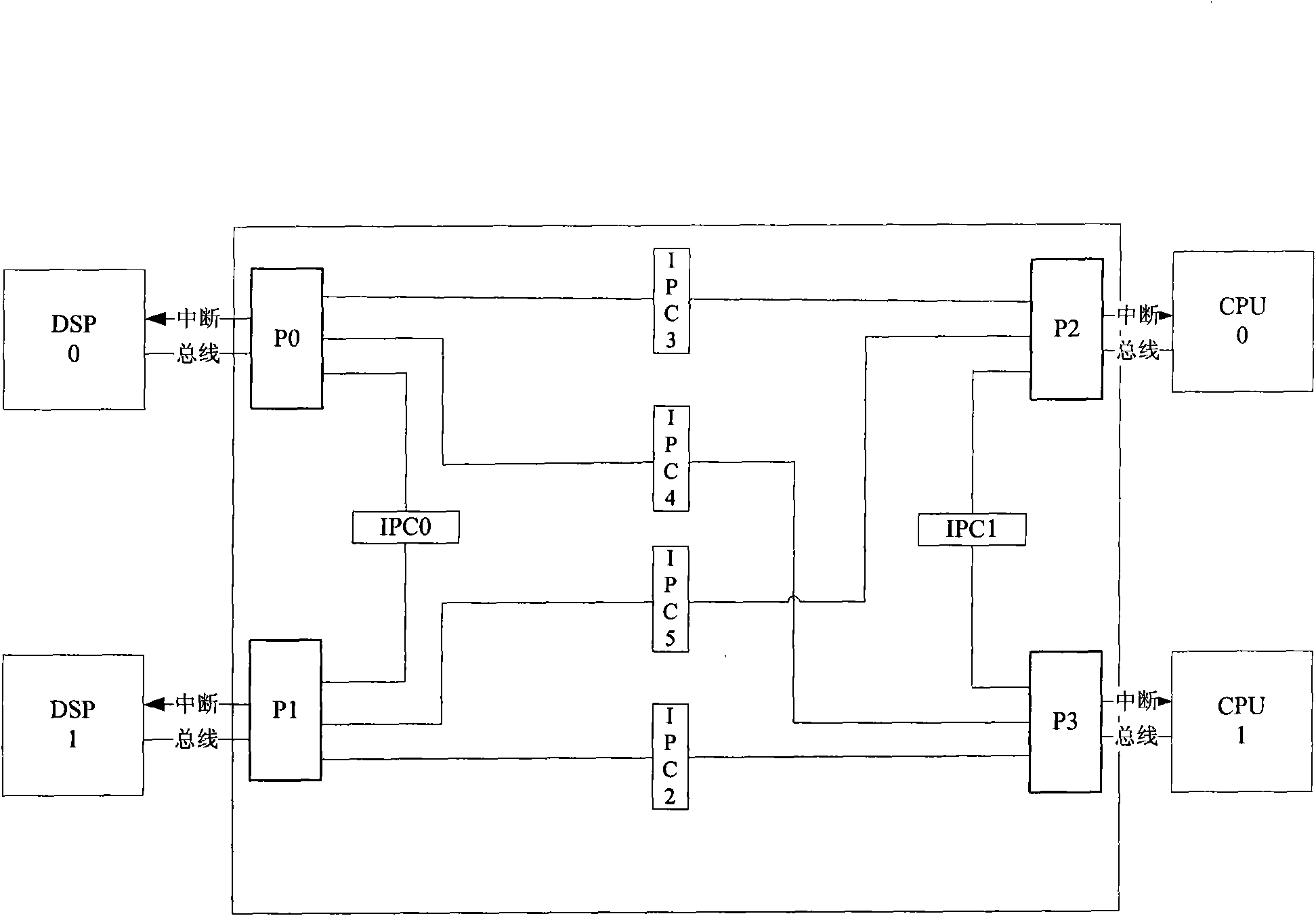

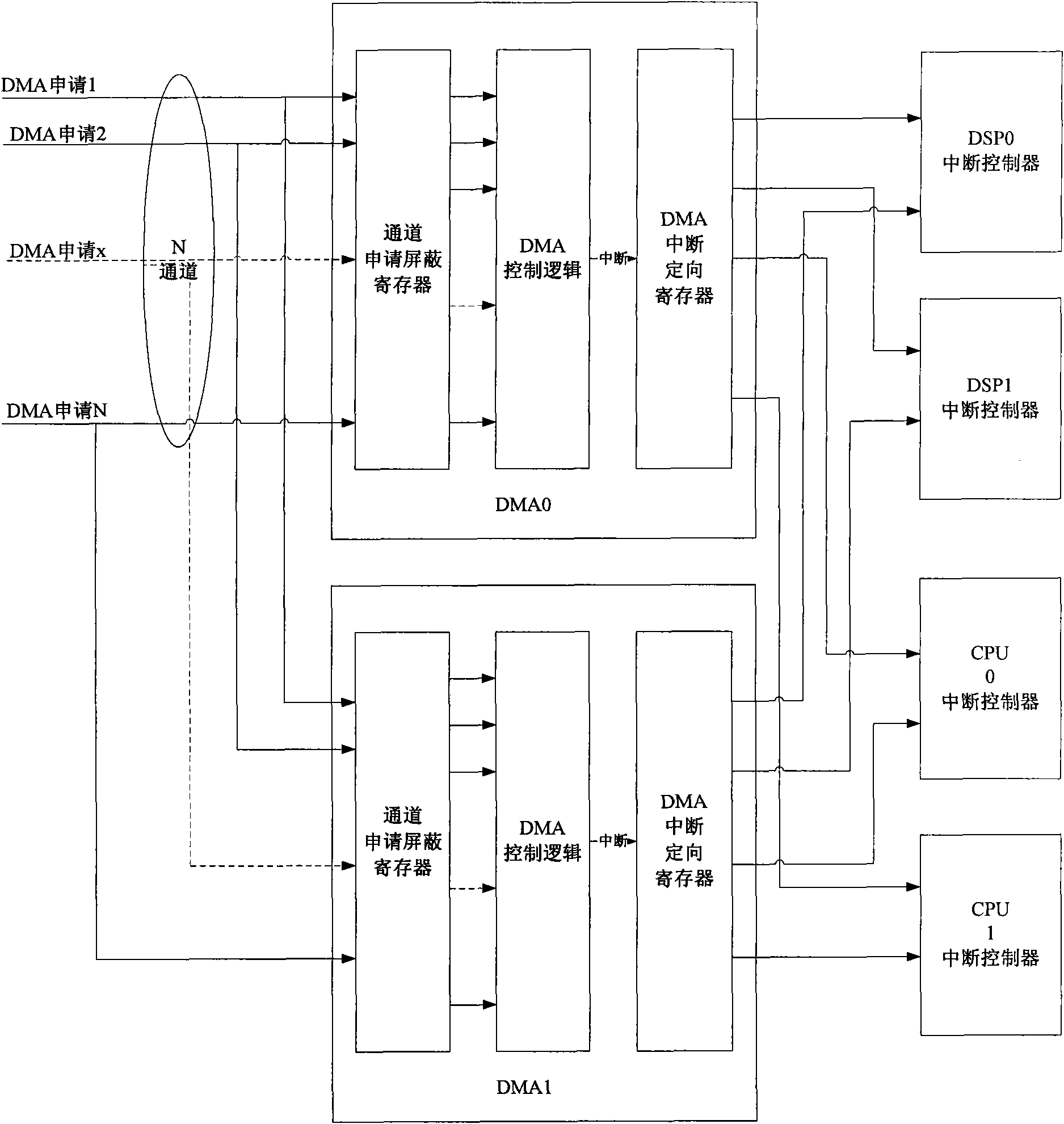

[0027] The core of the present invention is: configure the IPC array, each port of the IPC array is connected to a processor, and configure the group sending control register at the port, and control the information interaction between the processors through the operation of the group sending control register ; Inside the DMA controller, configure the channel application mask register and the interrupt orientation register connected to the interrupt controller of each processor, the channel application sent by the bus slave device is input into the channel application mask register of each DMA controller, and pass to all The selection operation of the channel application mask register is used to determine that the corresponding DMA controller responds to the corresponding channel application; the control logic module in the responding DMA controller sends an interrupt application, and through the selection of the interrupt orientation register, it is sent to the corresponding pr...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap