Address generation for multiple access of memory

A memory address, memory technology, applied in the field of turbo decoder architecture, which can solve the problems of high ASIC clock rate, high power consumption, high end-user price, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

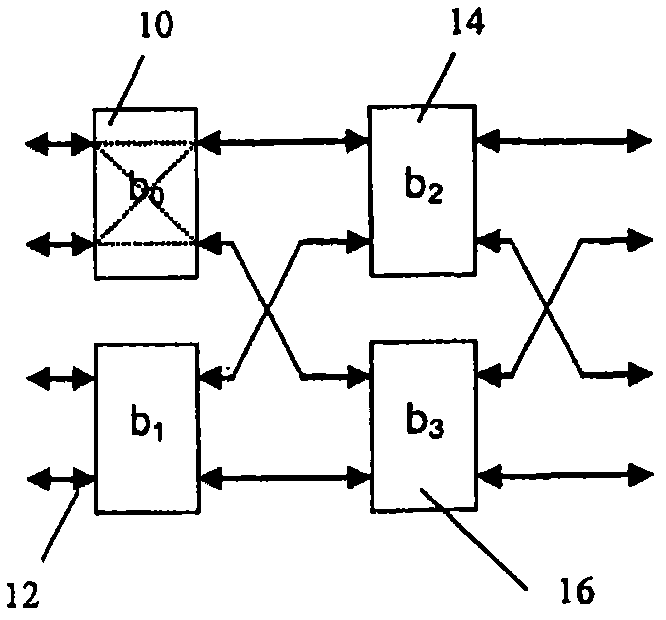

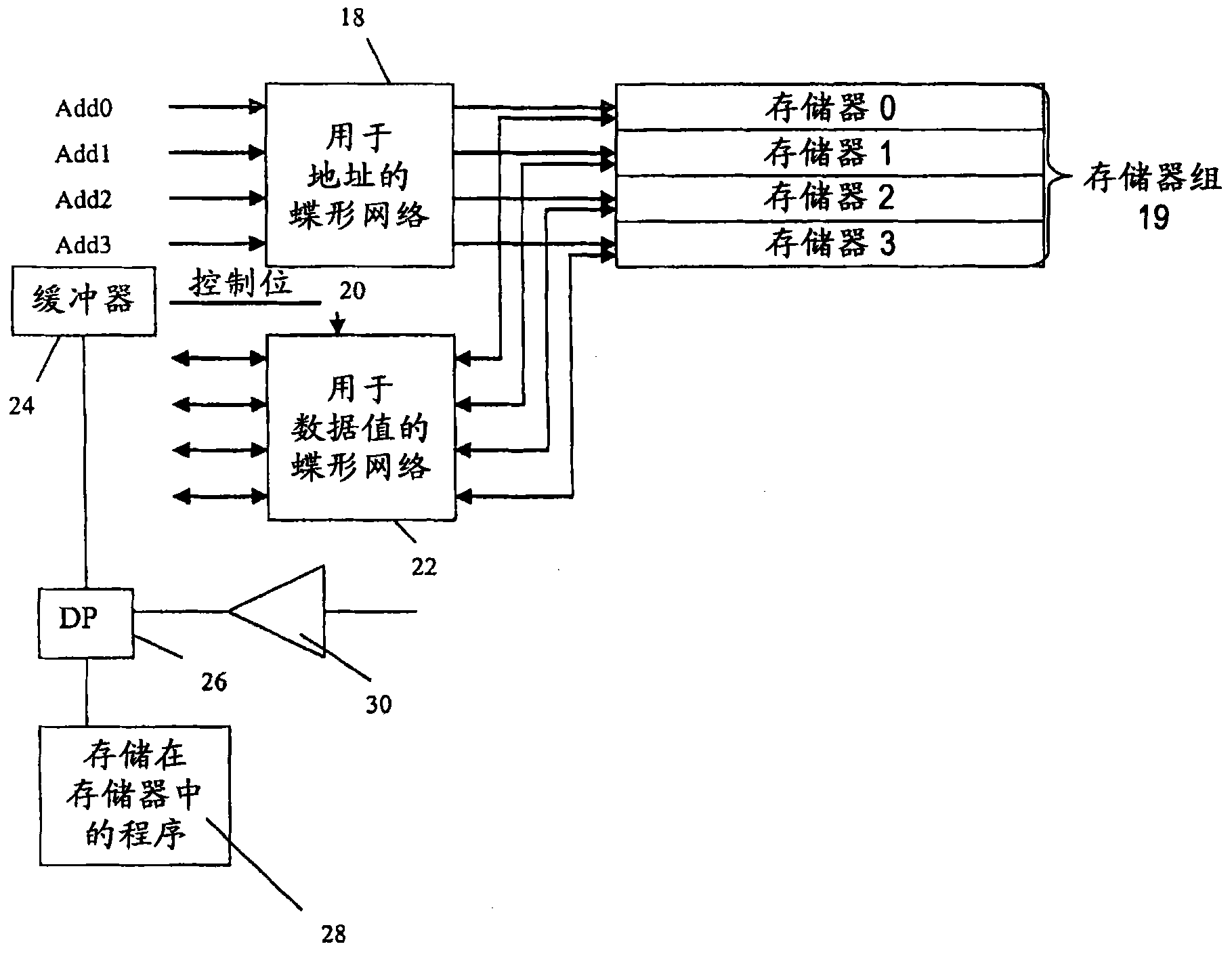

[0025] The general method referred to above for the Multiple Access Decoder can be applied to a turbo code with a quadratic permuted polynomial interleaver for inner interleaving. On the other hand, using the properties of quadratic permutation polynomials, the parallel processing access scheme can be simplified and optimized. Specifically, the routing network between the memory and the turbo decoder becomes simple, and the control bits can be generated on the fly. The parallel access scheme described in the exemplary embodiments herein relies on quadratic permutation polynomials.

[0026] Embodiments of the present invention may be used in networks operating with, for example, 3G, WiMAX, LTE (3.9G or Long Term Evolution of UTRAN), HSDPA / HUSPA (High Speed Downlink / Uplink Packet Access) and other wireless protocols . Embodiments of the invention are not limited to a particular radio protocol, but may be used in mobile devices / user equipment and / or network elements (such as ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More