System and method for designing integrated circuits that employ adaptive voltage scaling optimization

An integrated circuit, a technique for designing circuits, applied in the field of integrated circuit design, capable of solving problems such as obstruction, setup or hold time violation, and damage to circuit logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

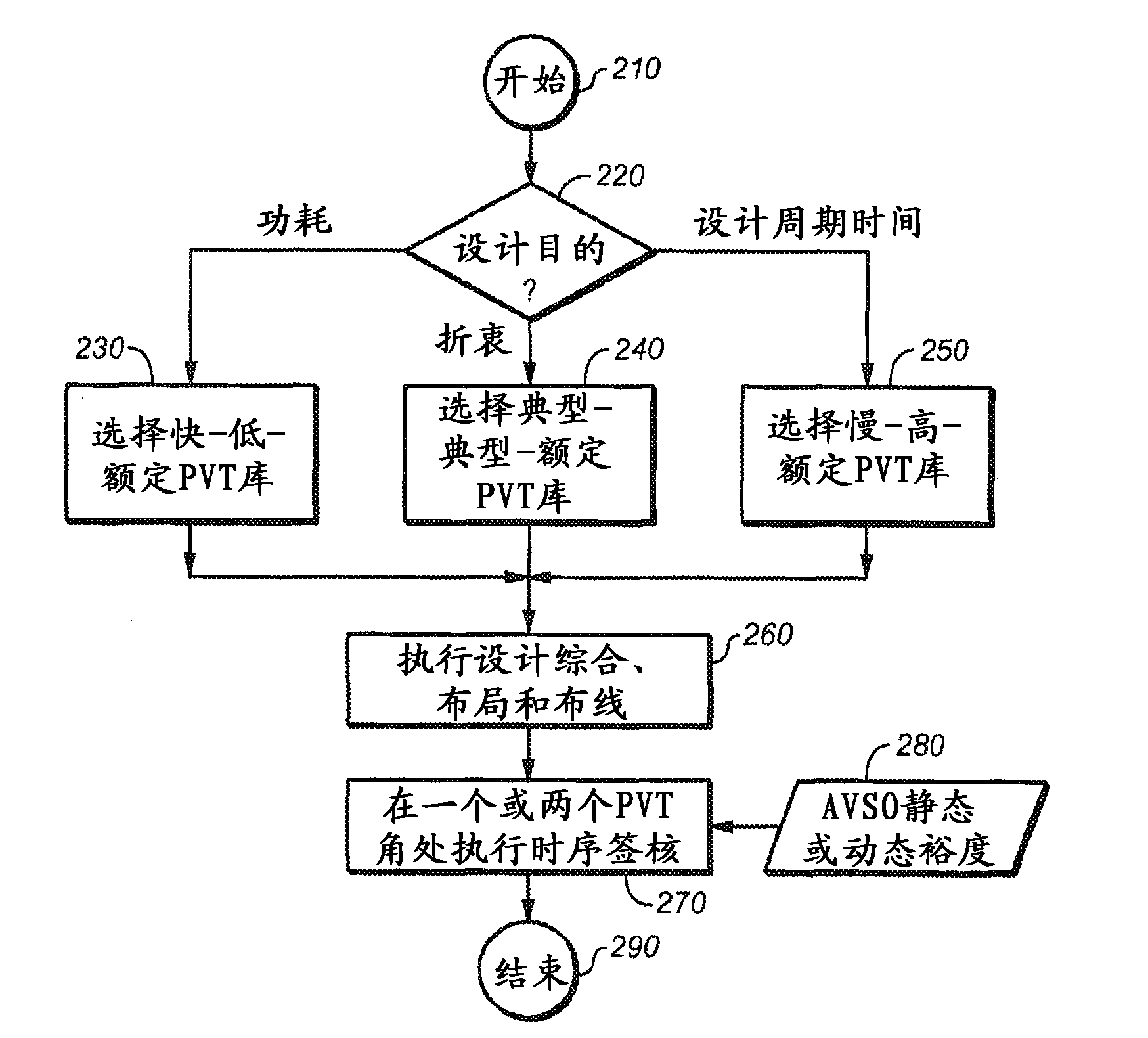

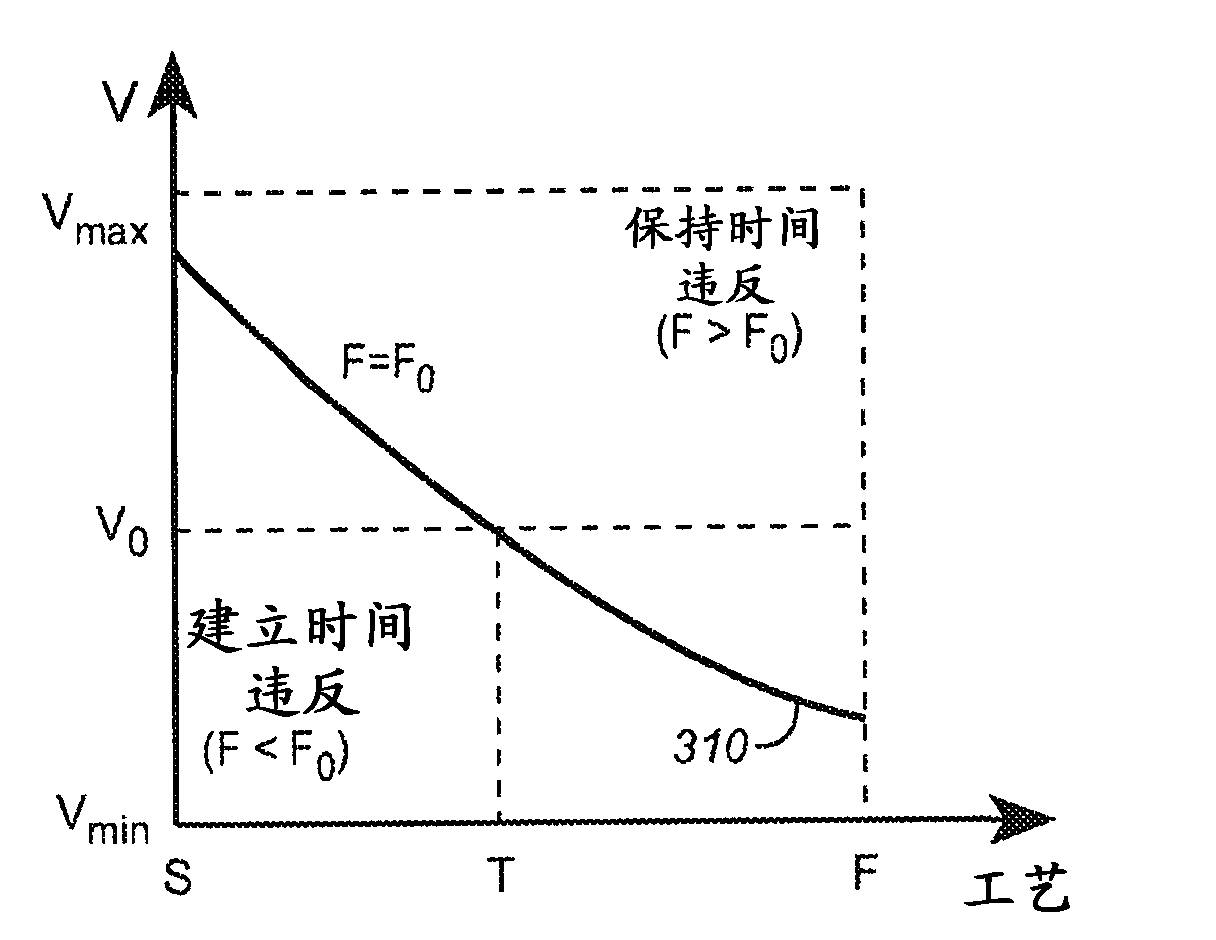

[0020] It has been found that conventional IC design flows fail to take advantage of the AVSO IC's ability to adjust its supply voltage in real time to achieve signal propagation speed adjustment. A better design flow for AVSO ICs would allow the circuit designer to predetermine whether power consumption, rapid development (also known as turnaround) time, or a tradeoff between the two is the design goal. It has also been found that implementing the slow and fast PVT and RC corner results of conventional signoff timing is inappropriate for AVSO ICs. The timing signoff of the AVSO IC should advantageously utilize values of PVT and RC corners and on OCV margins that are never considered by the conventional timing signoff process.

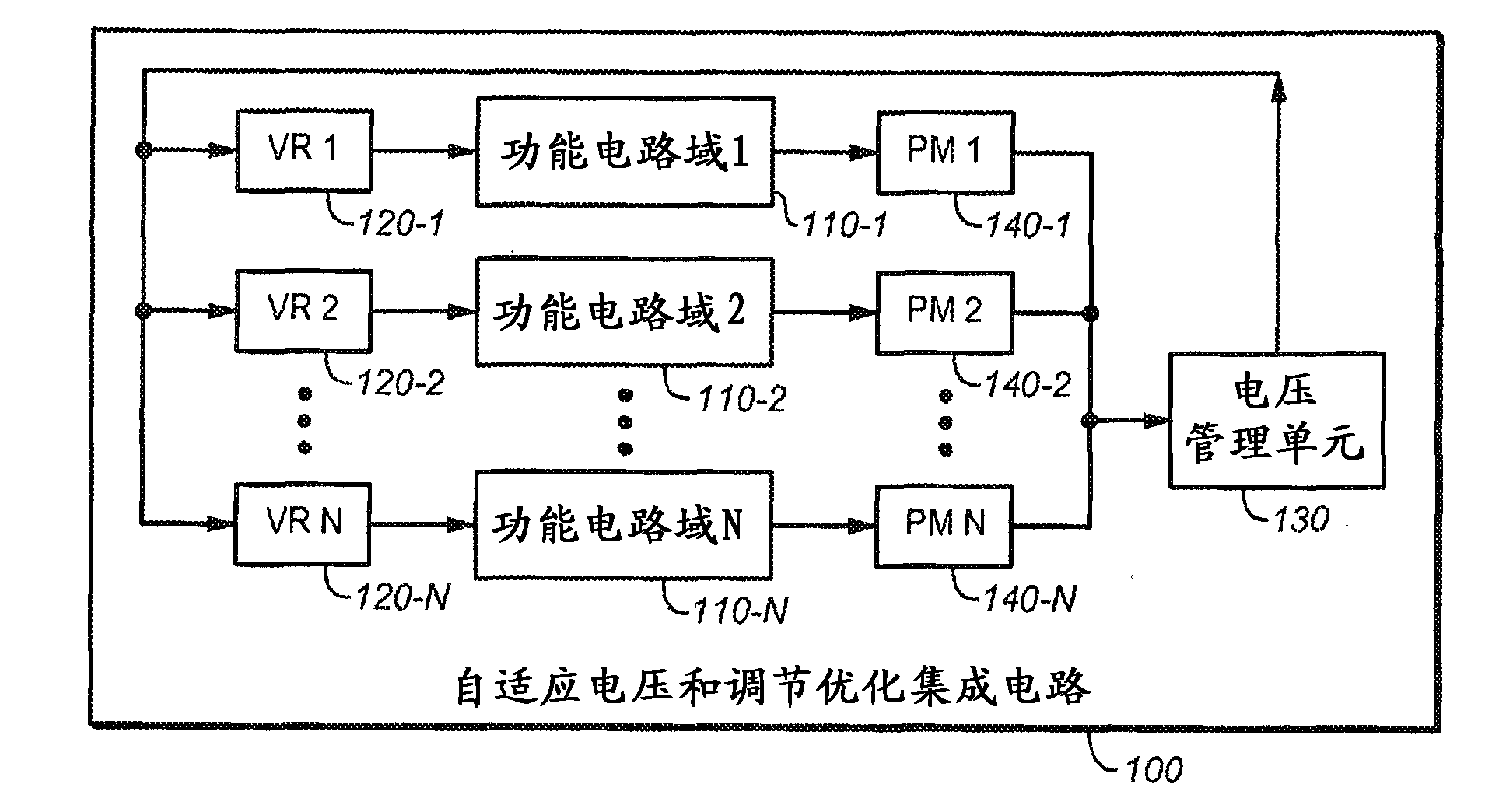

[0021] Various embodiments of systems and methods for designing AVSO ICs are described herein. The main purpose when designing any IC is to generate the F 0 The following design works as expected. Various embodiments described herein allow circuit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More