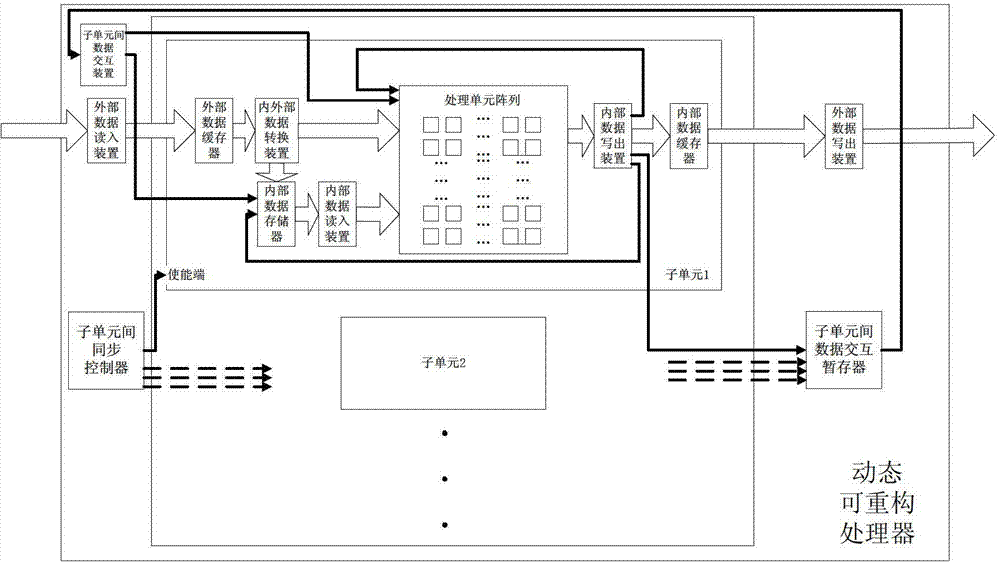

Method for hierarchically describing configuration information of dynamic reconfigurable processor

A technology for configuring information and processors, which is applied in the direction of electrical digital data processing, instruments, computers, etc., and can solve the problems of excessive storage and transmission of configuration information

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

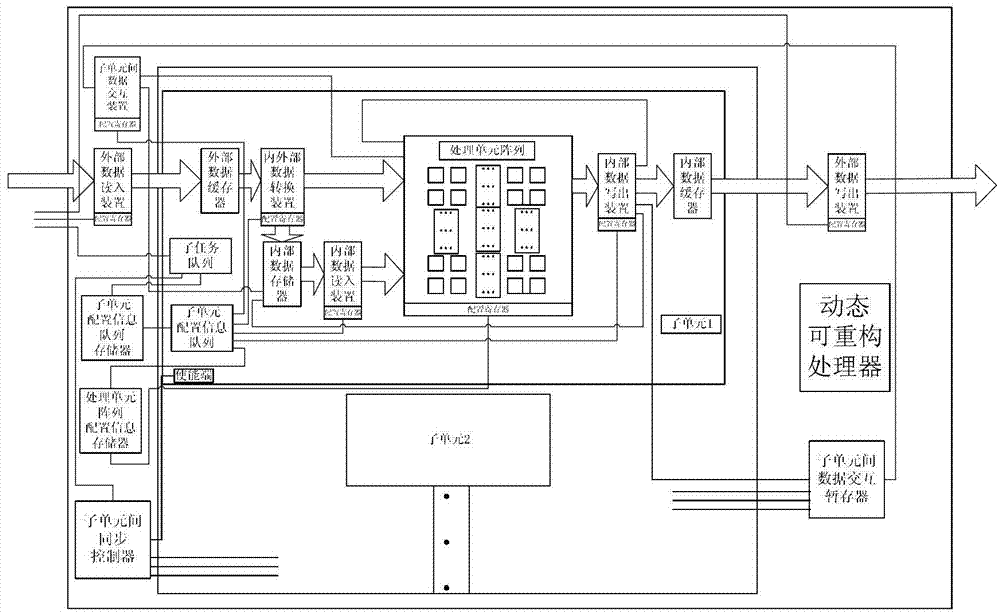

Examples

Embodiment

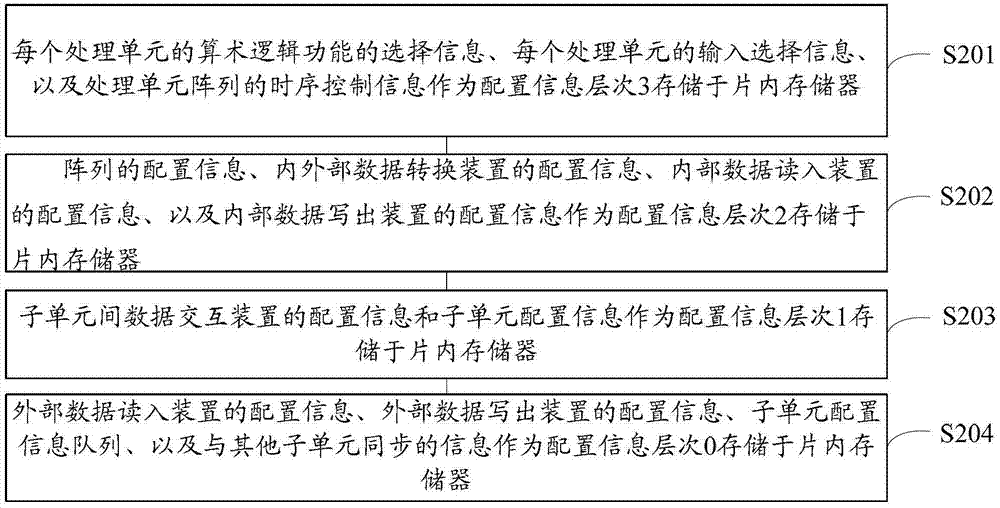

[0071] refer to figure 2 , shows a flowchart of a method for hierarchically describing configuration information of a dynamically reconfigurable processor according to the present invention, the method specifically includes:

[0072] Step S201, the selection information of the arithmetic logic function of each processing unit, the input selection information of each processing unit, and the timing control information of the processing unit array are stored in the on-chip memory as configuration information level 3;

[0073] Step S202, the configuration information of the array, the configuration information of the internal and external data conversion device, the configuration information of the internal data reading device, and the configuration information of the internal data writing device are stored in the on-chip memory as configuration information level 2;

[0074] Step S203, the configuration information of the inter-subunit data interaction device and the subunit con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More