IBIS (Input/Output Buffer Information Specification) model verification method and system

A model verification and model technology, which is applied in the fields of communication and electronics, can solve problems such as inability to verify the accuracy of the model, and achieve the effect of accelerating research and development progress, quality, and high precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

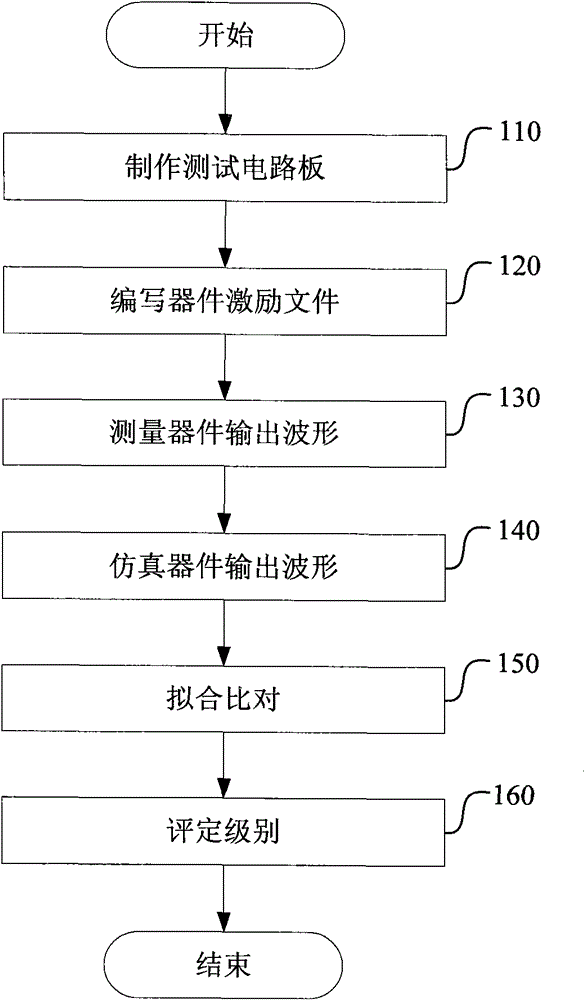

[0033] The present invention adopts following technical scheme:

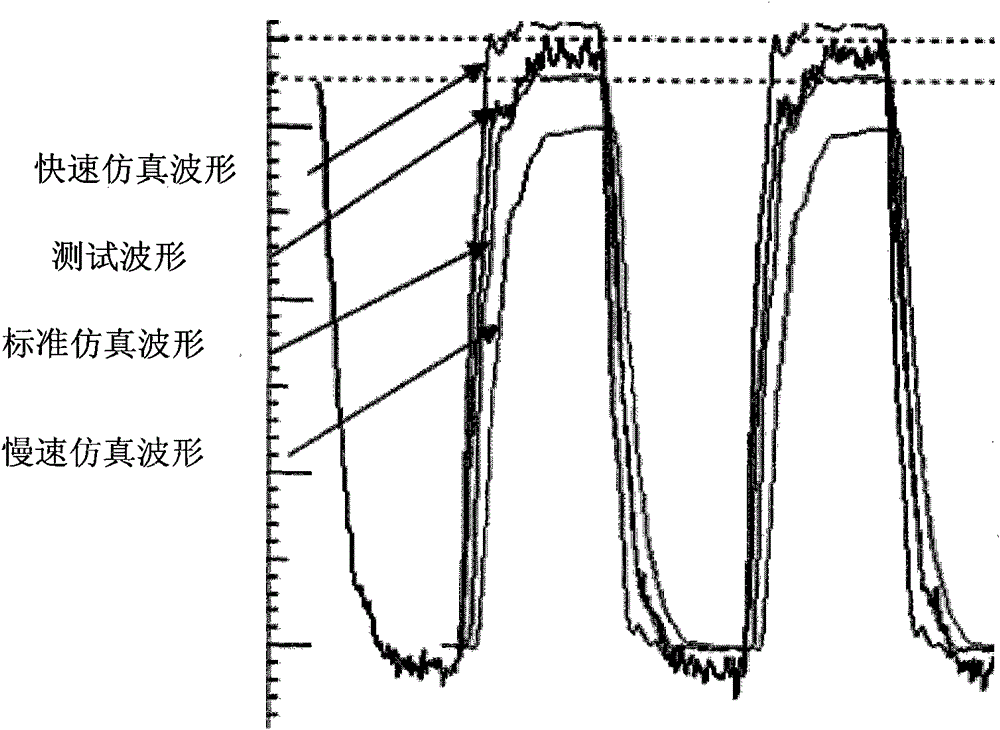

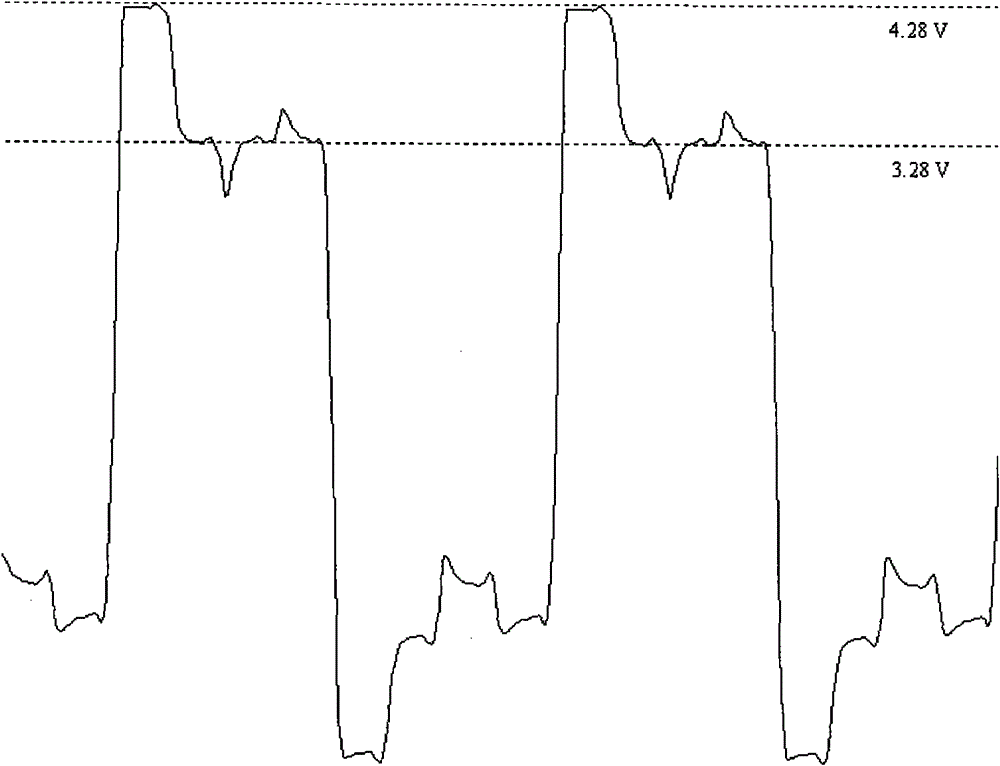

[0034] A standard test circuit board is constructed for the pins corresponding to the model to be verified of the device, and the test circuit board covers as much as possible the pins corresponding to all the models to be verified on the device to ensure high utilization of the test circuit board. Use appropriate stimulus to make the corresponding pins of the model to be verified emit the required waveform, and then use a suitable instrument to capture this waveform to complete the acquisition of the verification benchmark. Construct the circuit topology model of the pin corresponding to the model to be verified on the circuit board of the test board in the simulation tool, and perform reflection simulation. At this time, the simulation waveform obtained by simulating according to the model to be verified can be obtained. The test waveform captured by the instrument is compared and measured with the simulated w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More