Pseudo-wire labeling method for MPLS (Multiple Protocol Label Switching) network virtual exchange embodiment

A virtual switching instance and network virtualization technology, applied in the field of chip processing, can solve the problems of occupying the register memory of chips and devices, different access pseudowires, and complex configuration levels, so as to reduce delay and jitter, save hardware resources, The effect of fewer message processing procedures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

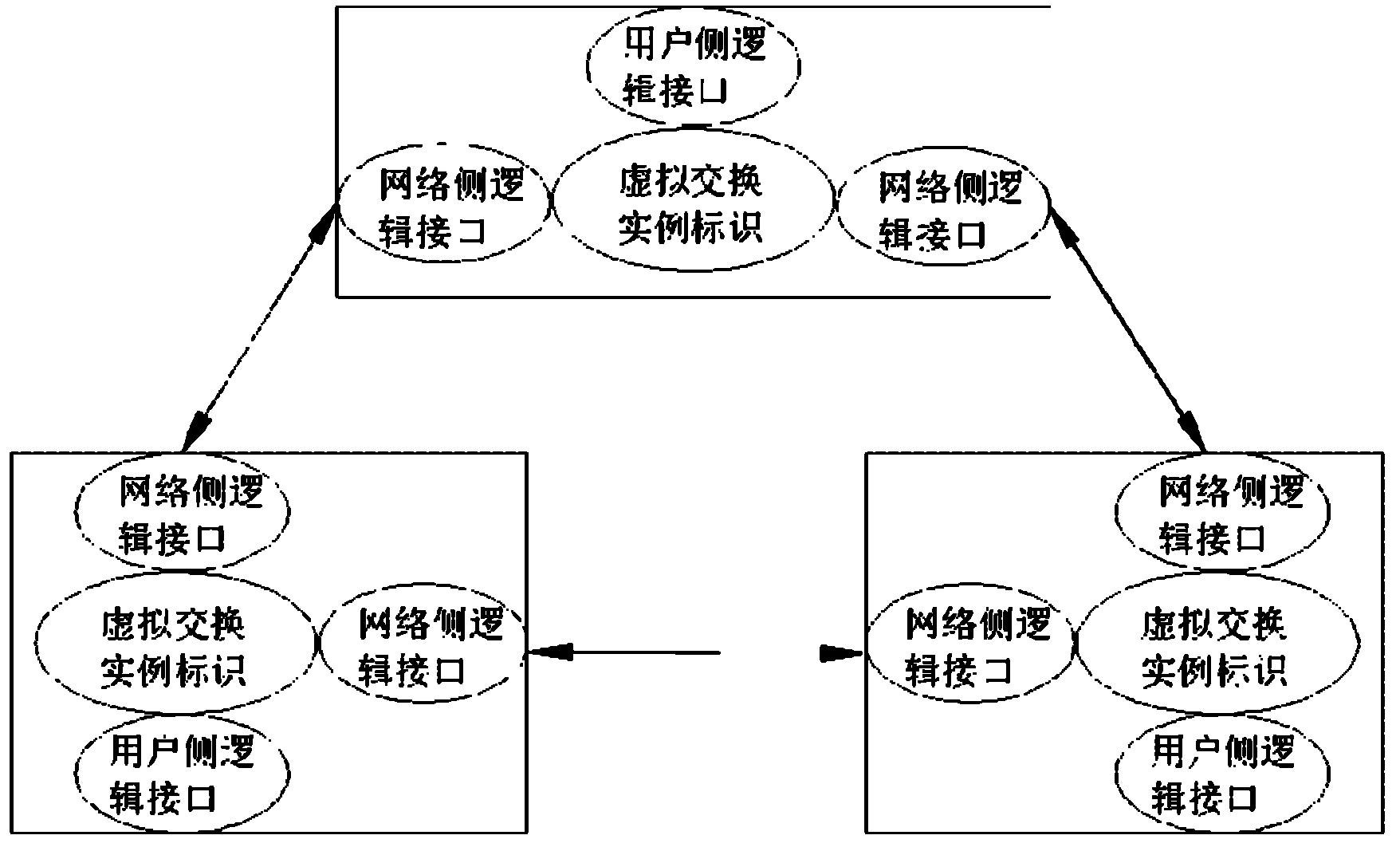

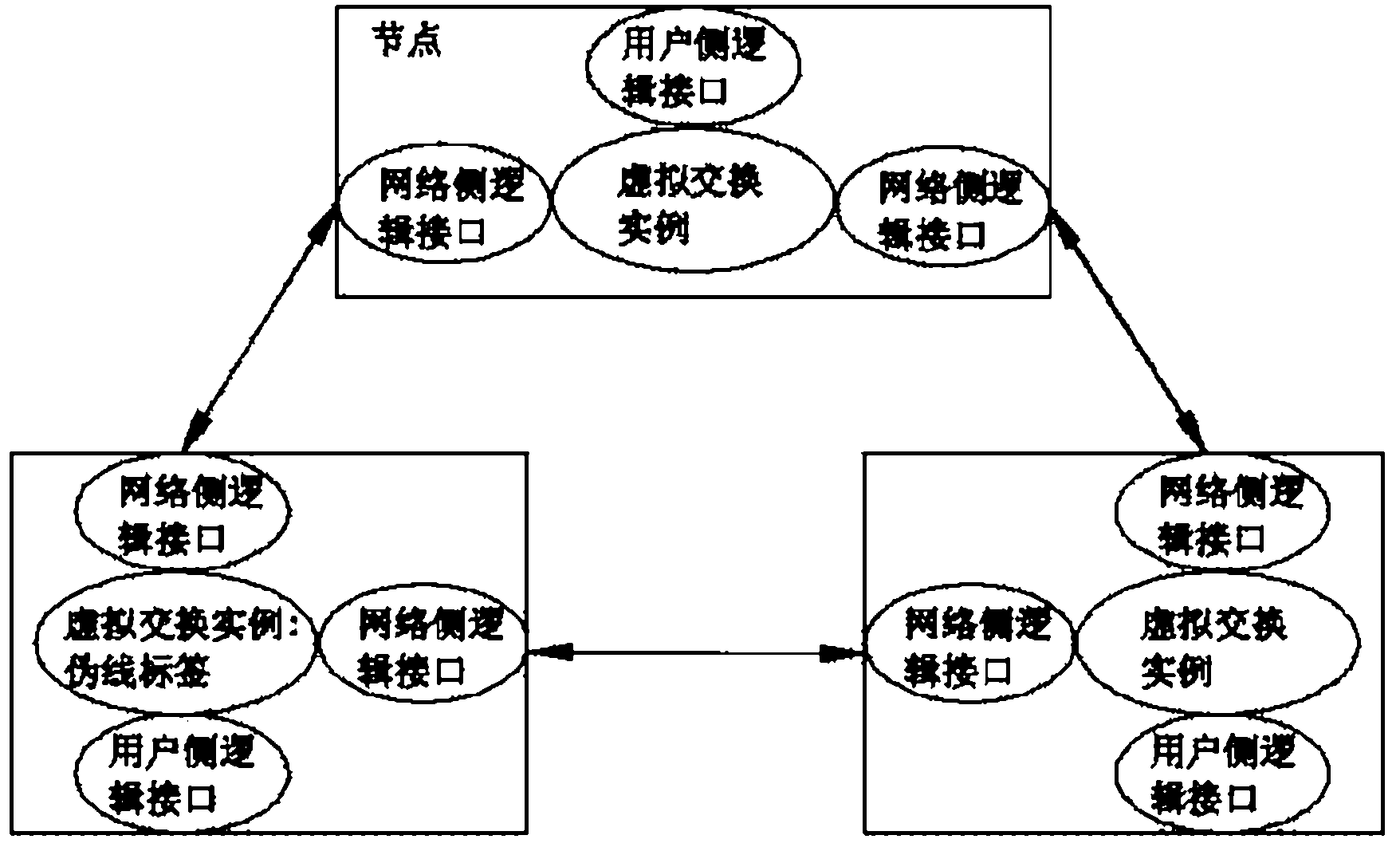

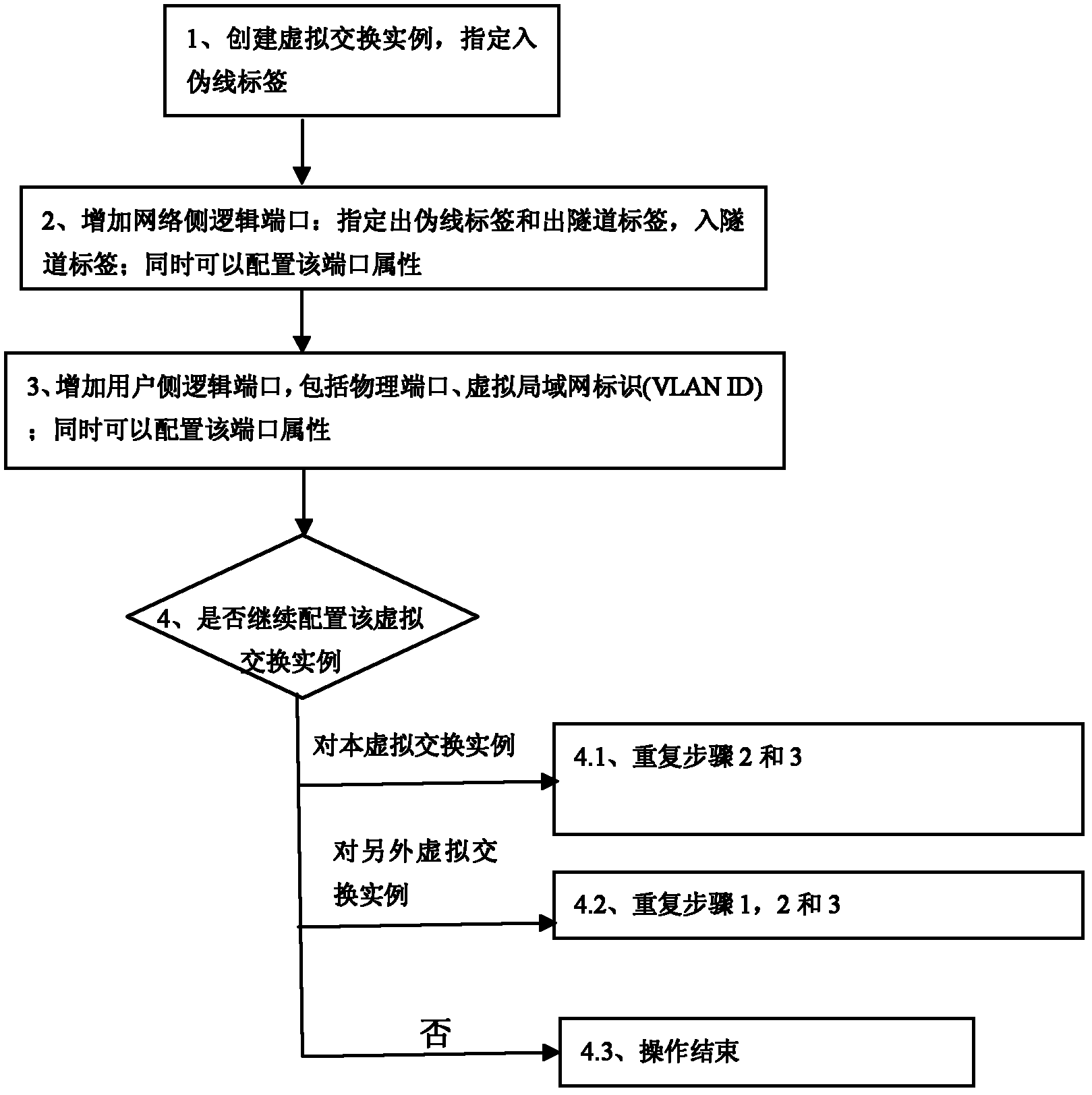

[0055] Embodiments of the present invention are described in further detail below in conjunction with accompanying drawings:

[0056] A kind of pseudo wire label method used for MPLS network virtual switching instance, the configuration process in the two-layer virtual private network is as follows:

[0057] (1) Create a virtual switching instance and specify the incoming pseudowire label;

[0058] (2) Add network-side logical ports in the virtual switching instance, specify outgoing pseudowire labels, outgoing tunnel labels, and incoming tunnel labels, and configure the described network-side logical port attributes;

[0059] (3) Add a user-side logical port to the virtual switching instance, the user-side logical port includes a physical port and a virtual local area network identifier, and configure attributes of the user-side logical port.

[0060] A logical port entry and exit table is defined, and the entry and exit table is generated through direct configuration of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More