Vertical coplanar waveguide with tunable characteristic impedance, design structure and method of fabricating the same

A characteristic impedance and vertical alignment technology, applied to waveguides, waveguide devices, circuits, etc., can solve problems such as prolonging the design cycle and product launch time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

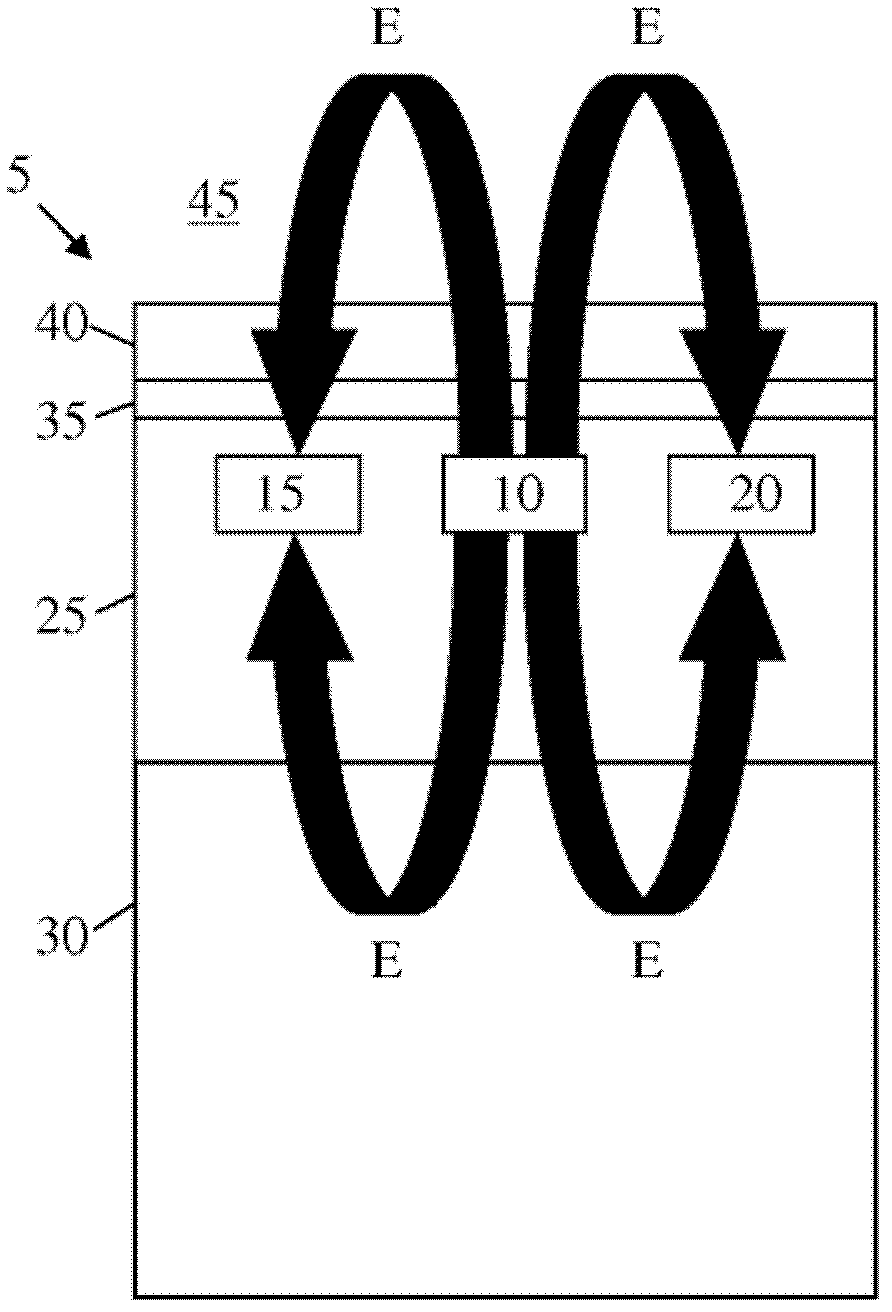

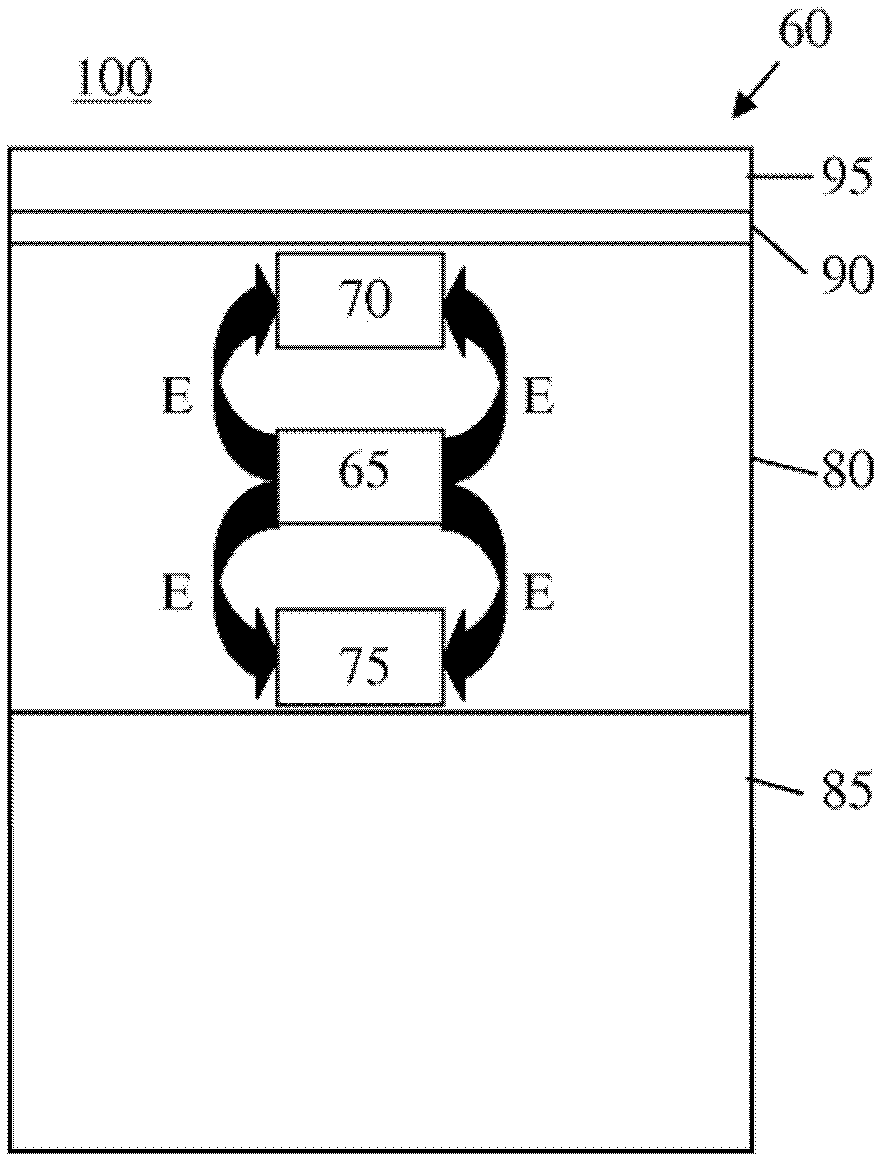

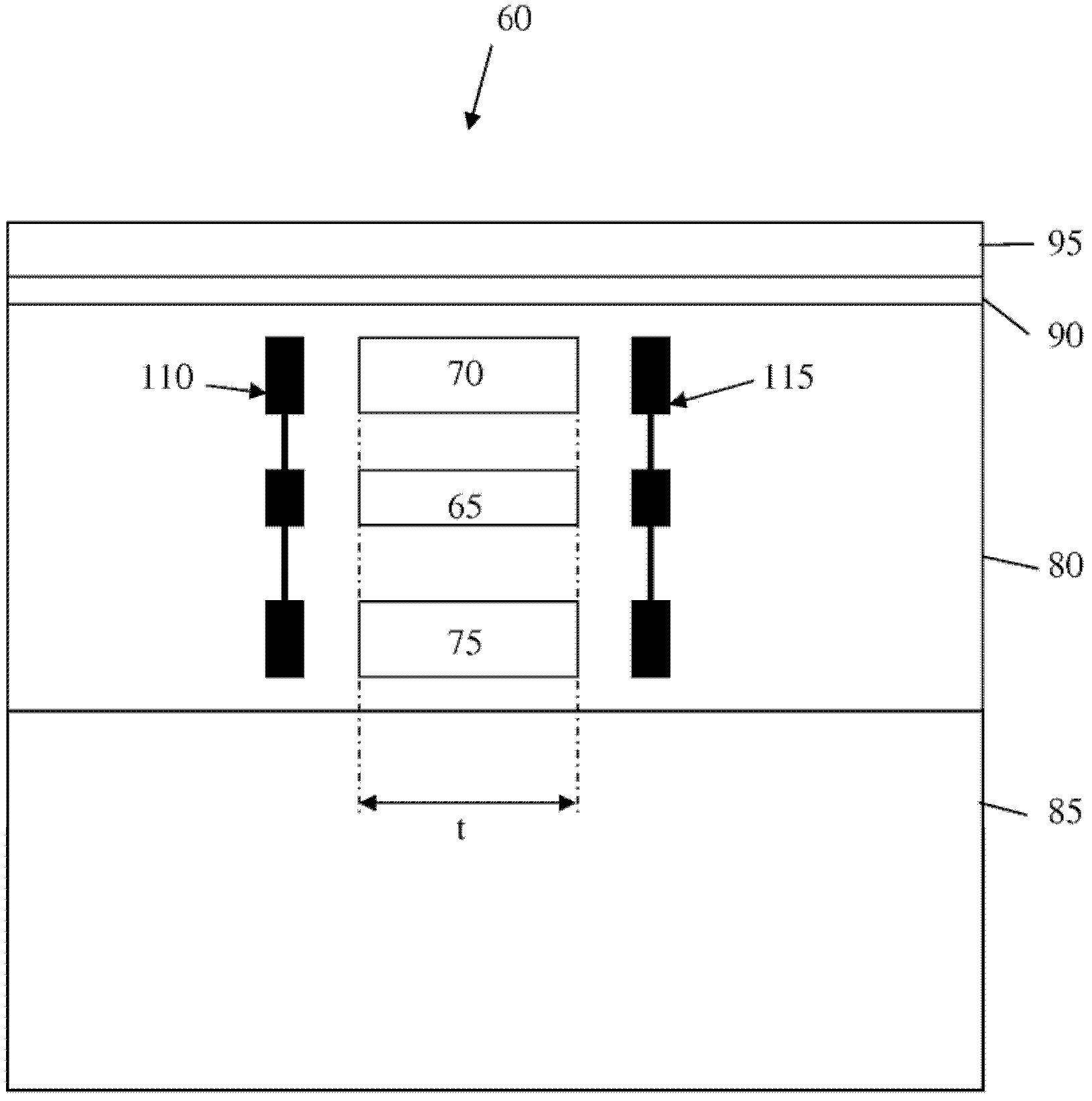

[0015] The present invention generally relates to on-chip transmission lines, and more particularly to on-chip vertical coplanar waveguides with tunable characteristic impedance, design structures and methods of manufacture thereof. In an embodiment, the on-chip transmission line includes a signal line formed in a wiring layer on the active device. The first ground line is formed in the wiring layer below the signal line and separated from the signal line by a dielectric material. The second ground line is formed in the wiring layer above the signal line, and is also separated from the signal line by a dielectric material. The signal line and the two ground lines are vertically aligned in the dielectric material, which creates a substantially symmetrical electric field for the vertical coplanar waveguide. In this way, embodiments of the present invention provide design structures that are easier to accurately model.

[0016] According to aspects of the present invention, the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap