Phase-locked loop with low-gain voltage-controlled oscillator

A technology of voltage-controlled oscillators and phase-locked loops, which is applied to automatic control of power, electrical components, etc., can solve problems such as system failure and achieve stable phase-locked loops

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

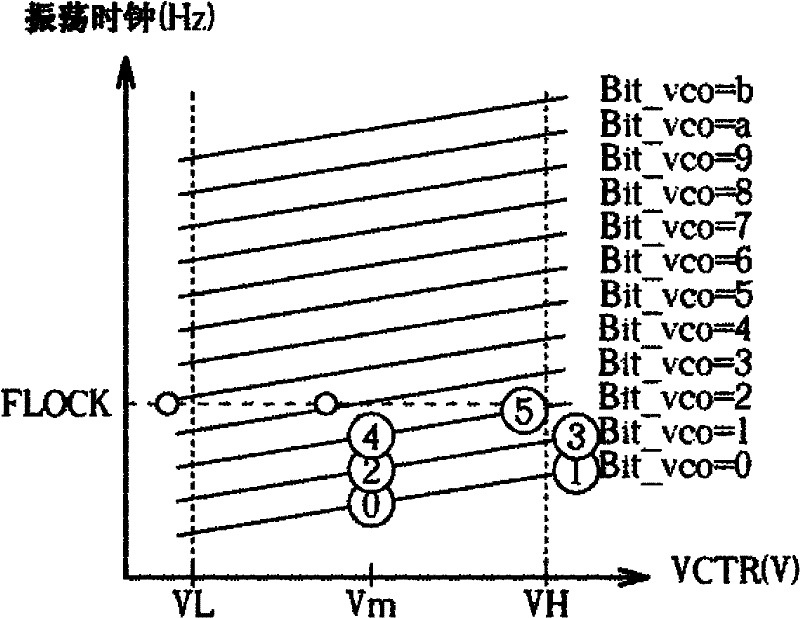

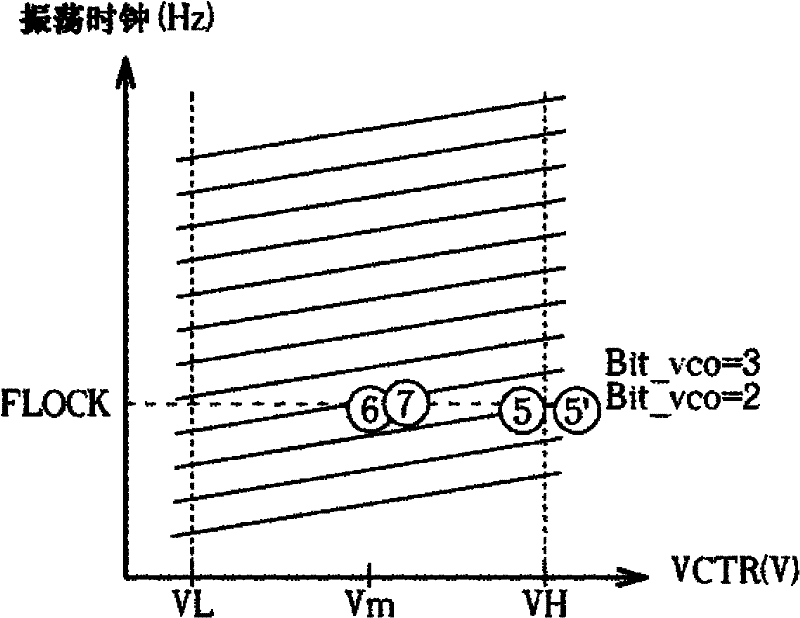

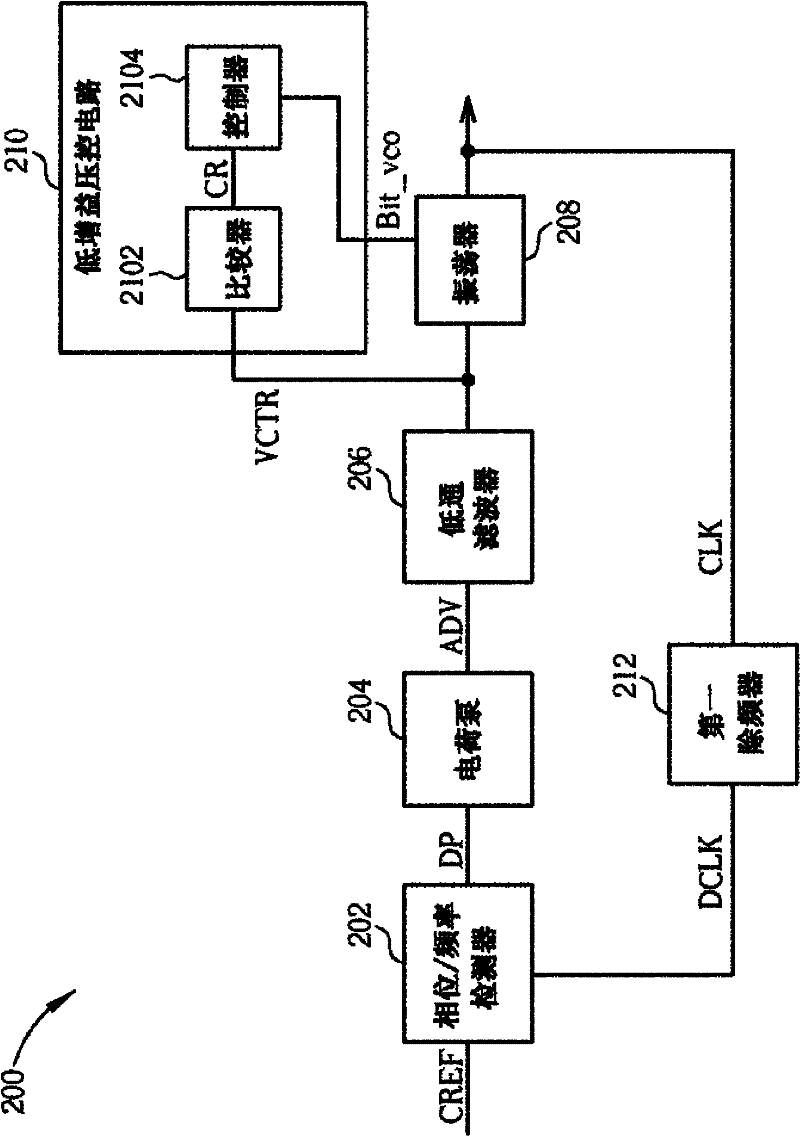

[0063] Please refer to figure 2 , figure 2 It is a schematic diagram illustrating a phase-locked loop 200 with a low-gain voltage-controlled oscillator according to an embodiment of the present invention. The PLL 200 includes a phase / frequency detector 202 , a charge pump 204 , a low-pass filter 206 , an oscillator 208 , a low-gain voltage control circuit 210 and a first frequency divider 212 . The phase / frequency detector 202 is used to generate a detection pulse DP according to the phase / frequency difference between a reference clock CREF and a frequency-dividing oscillation clock DCLK, wherein the detection pulse DP and the phase / frequency difference are linearly proportional. The charge pump 204 is coupled to the phase / frequency detector 202 for generating a detection voltage ADV according to the detection pulse DP; the low-pass filter 206 is coupled to the charge pump 204 for generating an oscillation according to the detection voltage ADV The oscillator control volta...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com