storage device

A storage device and storage layer technology, applied in information storage, static storage, digital storage information, etc., can solve the problems of difficult to manufacture reference storage cells, difficult to prepare reference storage cells, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

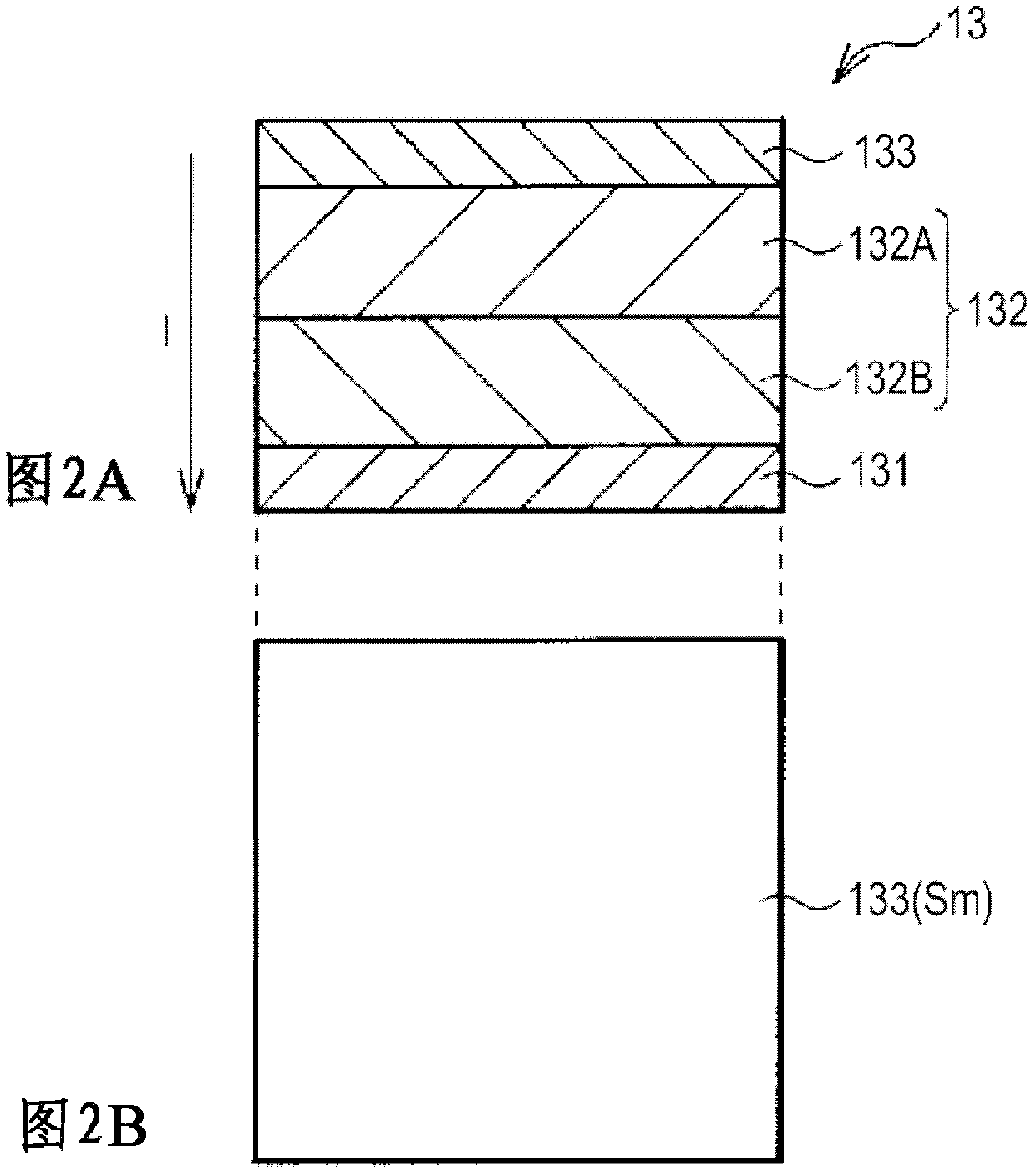

[0023] 1. First Embodiment (Example in which the area of the second variable resistance element constituting the reference memory cell is larger than the area of the first variable resistance element of the memory cell)

[0024] 2. Second Embodiment (Example in which the second variable resistance element constituting the reference memory cell is provided with a plurality of variable resistance elements having the same configuration as the first variable resistance element)

[0025]

[0026] [Configuration of Storage Device 1]

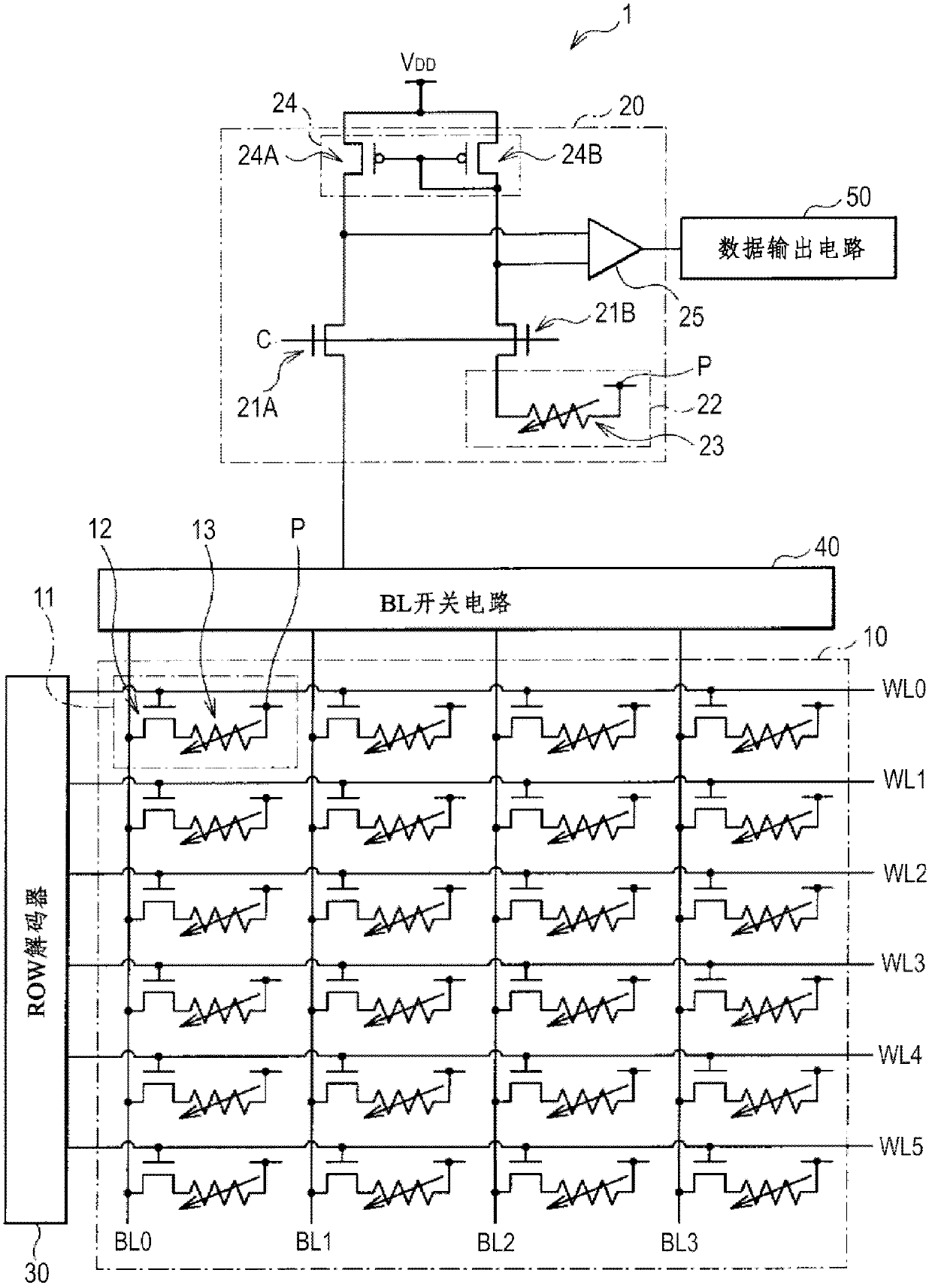

[0027] figure 1 A schematic configuration of the storage device 1 according to the first embodiment of the present invention is shown. This storage device 1 includes a memory array (storage unit) 10 , a readout circuit 20 , a ROW decoder 30 , a BL switch circuit 40 , and a data output circuit 50 .

[0028] (storage array 10)

[0029] The memory array 10 has a plurality of memory cells 11 arranged in a matrix (for example, 4 columns×6 rows) in ...

no. 2 approach

[0073] Figure 7 A schematic configuration of a storage device 2 according to a second embodiment of the present invention is shown. This embodiment differs from the first embodiment described above in that a plurality of variable resistance elements 26 having the same configuration as the variable resistance elements 13 in the memory cell 11 are included in the reference memory cell 22A as second variable resistance elements. Each of the plurality of variable resistance elements 26 is connected in parallel to one terminal of the transistor 21B for applying a read voltage through a transistor 27 . exist Figure 7 In this example, three variable resistance elements 26 are connected in parallel, but the number of variable resistance elements 26 may be two or more.

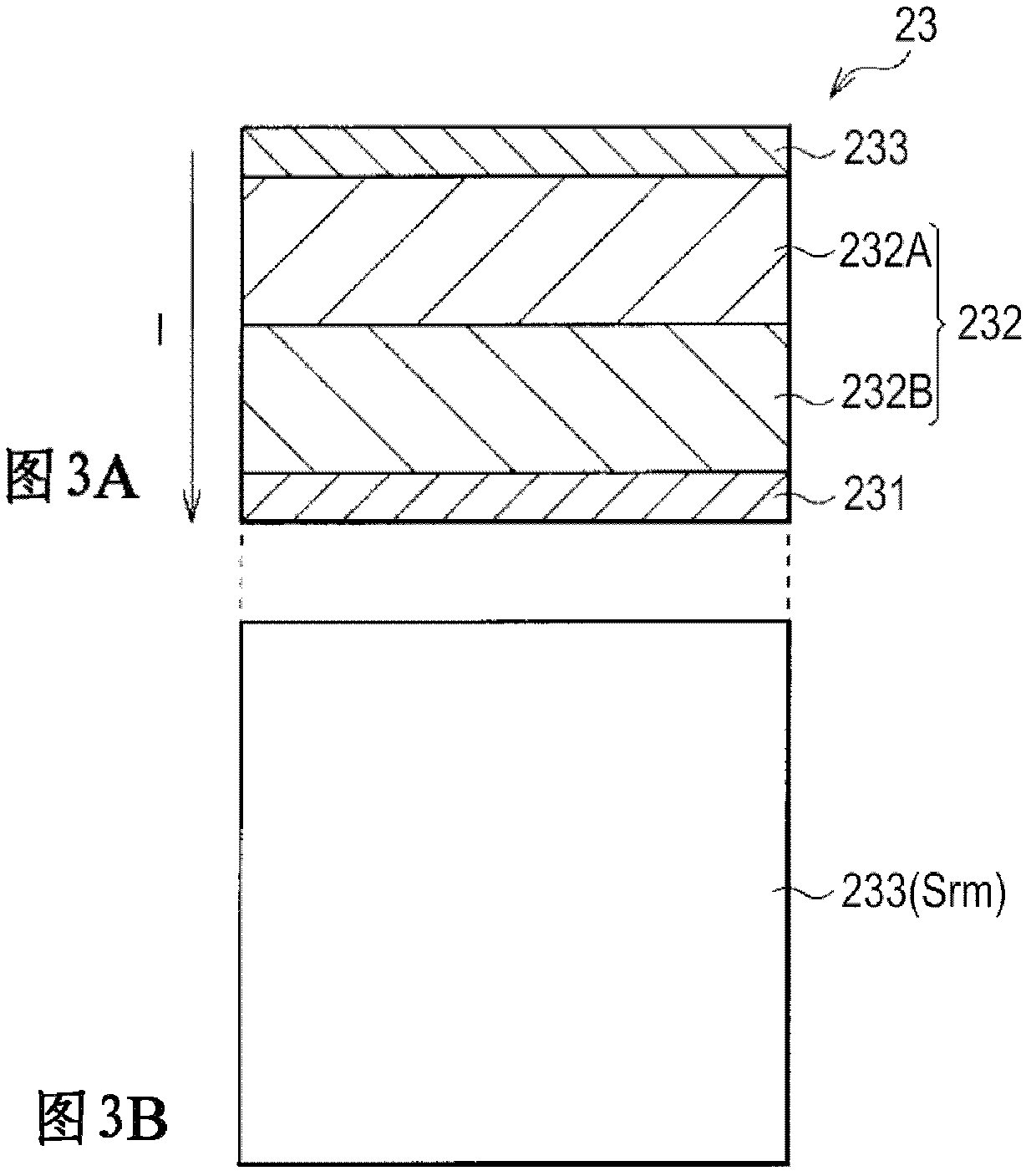

[0074] Figure 8A represents the cross-sectional configuration of the resistance change element 26, while Figure 8B A planar arrangement of the variable resistance element 26 is shown. The variable resistance e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More